0-

Изобретение относится к технике телевиД ения и может быть использован для сжатия, полосы частот видеосиг- нала. Цель изобретения - повышение точ ности преобразования видеосигнала при сжатии его полосы частот.

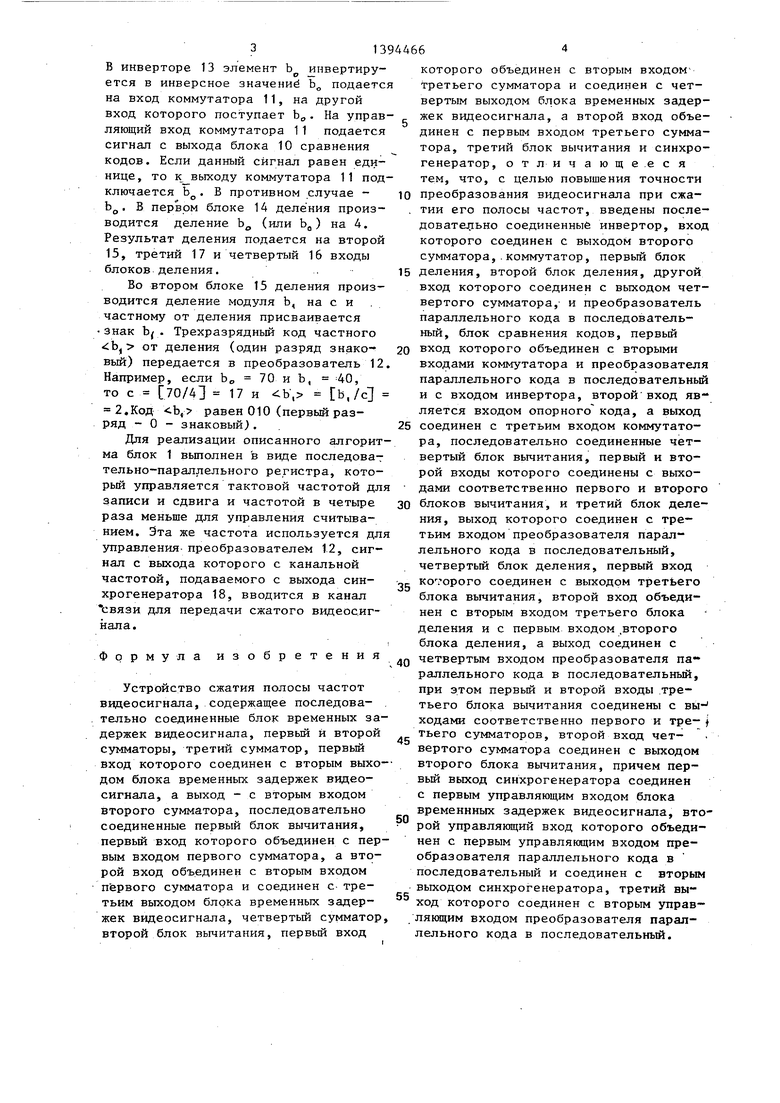

На чертеже представлена электрическая структур.ная схема устройства сжатия полосы частот видеосигнала. Устройство сжатия полосы частот видеосигнала содержит блок 1 временных задержек видеосигнала, первый сумматор 2, первый блок 3 вычитания, третий, сумматор 4, второй блок 5 вычитания, второй сумматор 6, третий блок 7 вычитания, четвертый сумматор 8, четвертый блок 9 вычитания, блок 10 сравнения кодов, коммутатор 11, преобразователь 12 параллельного код в последовательный, инвертор 13, первый 14 и второй 15 блоки, деления, четвертый блок 16 деления, третий блок 17 деления, синхрогенератор 18.

Устройство сжатия полосы частот видеосигнала работает следующим образом,

В устройстве сжатия полосы частот видеосигнала реализуется быстрое пре- образование Адамара четырех кодируемых элементов изображения. При этом ос уществляется адаптивное кодирование трех элементов трансформанты Ь, , Ъ Hbj. Адаптация заключается в выбо- ре передаваемого значения Ь; (i 1, 2,3) В зависимости от значения Ь для каждого кодируемого квартета элементов Ад, a, а,, и а,. В основу адаптивного кодирования положена зависи- мость границ (верхней и нижней) изменения Ь; (i Г,2,3) от Ьд :

bg, если Ь„ 126; (252 - Ь„), если На кодирование jb;| отводится два бита. Адаптивное четьфехуровневое (двухбитовое) кодирование 1Ь;1 осуществляется по следующему алгоритму. Для каждой кодируемой группы из четырех элементов вычисляется

Гь„/4, если Ьд :й 126; Л J

(252-Ь)/4, если Значение (252 - bo) является ин- версией bj, при b 126 и формируется в инверторе 13. Сравнение Ь с 126 производится с помощью блока 10 сравнения кодов. Выбор bo 1ши (252

- Ь) для вычислениями осуществляется коммутатором 11, управляемым сигналом с выхода блока 10. В первом блоке 14 деления производится вычисление д . Затем модуль |Ь;| каждого из трех коэффициентов Ь, , bj и bg делится на & и результат деления - трехразрядньй код (один разряд - знаковый, равный знаку Ь; ) - передается в преобразователь 12.

Пример. Пусть для некоторой кодируемой группы а 3, а, 7, а О, aj 18. При этом Ь 28, Ь, -22, bj -8, b, 14. Так как bo 28 126, то & 7 и :Ь, -3, -i 2, где ib-, - трехразрядный код bj . На приемной стороне по принятому Ь

Л

также вычисляется д, а значение Ь;

g 5

0 с Q

5

0

вычисляется по правилу Ь; СЬ;.Д.

Для рассмотренного примера Ь, -21, Ь -7 и bj 14. Порогом является значение Ь, . Таким образом, порог адаптивен и может изменяться от группы к группе.

Кодируемые элементы а; шестиразрядные и на четыре элемента приходится 24 бита. Элементы преобразования имеют большую разрядность и при .полноразрядном кодировании bj,, Ь, , b , bj на чётьфе элемента преобразования нужно затратить 32 бита, т.е. есть избыточность в передаваемых элементах преобразования, если последние кодиру-} ются не 3 ав НС имо.

Указанный принцип кодирования реализуется следующим образом.

На вход блока 1 поступает видеосигнал в цифровом виде (дискретнаирован- ный и квантованный на 64 уровня). В блоке 1 осуществляется формирование кодируемой группы из четьфех элементов: а, а,, а на,. В первом сумматоре 2 вычисляется сумма а + а,. В первом блоке 3 - разность а„ - а, . . Второй сумматор 6 производит сложение а, с аз, во втором блоке 5 осуществляется вычитание а из а. Второй . сумматор 6 предназначен для вычисления элемента трансформанты Ь. В четвертом сумматоре 8 формируется значение Ь,. Третий 7 и четвертый 9 блоки формируют Ь и Ьз соответственно. В блоке 10 сравнения кодов производит ся сравнение элемента преобразования Ь, с кодом числа 126. Если , сигнал на выходе блока 10-равен единице.

в инверторе 13 элемент ется в инверсное на вход коммутатора 11, вход которого поступает ляющий вход коммутатора

Ьр инвертиру- значениё Ь подается на другой Ьд. На управ- 11 подается

сигнал с выхода блока 10 сравнения кодов. Если данный сигнал равен единице, то к выходу коммутатора 11 подключается Ь. В противном случае - Ъд, В первом блоке 14 деления производится деление Ь (или Ь) на 4. Результат деления подается на второй 15, третий 17 и четвертый 16 входы блоков деления.

Во втором блоке 15 деления производится деление модуля Ь, на с и частному от деления присваивается Знак Ь . Трехразрядный код частного Ь, от деления (один разряд знаковый) передается в преобразователь 12 Например, если Ь, 70 и Ъ, 40, то с 70/41 17 и Ь , Ь,/с

2,Код Ь, равен 010 (первый разряд - О - знаковый).

Для реализации описанного алгоритма блок 1 вьшолнен в виде последоват тельно-параллельного регистра, который управляется тактовой частотой для записи и сдвига и частотой в четыре раза меньше для управления считыванием. Эта же частота используется для управления- преобразователем 12, сигнал с выхода которого с канальной частотой, подаваемого с выхода син- хрогенератора 18, вводится в канал связи для передачи сжатого видеосигнала.

Формула изобретения

Устройство сжатия полосы частот видеосигнала, содержащее последова- тельно соединенные блок временных задержек видеосигнала, первый и второй сумматоры, третий сумматор, первый вход которого соединен с вторым выходом блока временных задержек видеосигнала, а выход - с вторым входом второго сумматора, последовательно соединенные первый блок вычитания, первый вход которого объединен с первым входом первого сумматора, а второй вход объединен с вторым входом первого сумматора и соединен с-третьим выходом блока временных задержек видеосигнала, четвертый сумматор второй блок вычитания, первый вход

вторым входом соединен с чет4664

которого объединен с третьего сумматора и

вертым выходом блока временных задержек видеосигнала, а второй вход объединен с первым входом третьего сумматора, третий блок вычитания и синхро0

5

0

генератор, отличающе.еся тем, что, с целью повышения точности преобразования видеосигнала при сжа- . тии его полосы частот, введены после- довате/1ьно соединенные инвертор, вход которого соединен с выходом второго сумматора,.коммутатор, первьй блок 5 деления, второй блок деления, другой вход которого соединен с ВЬЕСОДОМ четвертого сумматора,- и преобразователь параллельного кода в последовательный, блок сравнения кодов, первый вход которого объединен с вторыми входами коммутатора и преобразователя параллельного кода в последовательный и с входом инвертора, второй вход является входом опорного кода, а выход соединен с третьим входом коммутатора, последовательно соединенные четвертый блок вычитания, первый и второй входы которого соединены с выходами соответственно первого и второго блоков вычитания, и третий блок деления, выход которого соединен с третьим входом преобразователя параллельного кода в последовательный, четвертый блок деления, первый вход которого соединен с выходом третьего блока вычитания, второй вход объединен с вторым входом третьего блока деления и с первым входом .второго блока деления, а выход соединен с четвертым входом преобразователя па раплельного кода в последовательный, при этом первый и второй входы .третьего блока вычитания соединены с вы- ходами соответственно первого и тре- f тьего сумматоров, второй вход четвертого сумматора соединен с выходом второго блока вычитания, причем первый выход синхрогенератора соединен с первым управляющим входом блока временнных задержек видеосигнала, второй управляющий вход которого объединен с первым управляющим входом преобразователя параллельного кода в последовательный и соединен с вторым выходом синхрогенератора, третий выход которого соединен с вторым управляющим входом преобразователя параллельного кода в последовательный.

5

0

5

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодер видеосигнала | 1987 |

|

SU1506554A1 |

| Кодер видеосигнала | 1989 |

|

SU1667256A2 |

| Кодер сигнала изображения | 1989 |

|

SU1644389A1 |

| Устройство кодирования телевизионного сигнала | 1986 |

|

SU1381730A1 |

| Устройство для эффективного кодирования изображений | 1988 |

|

SU1559412A1 |

| Устройство для кодирования и декодирования телевизионного сигнала | 1988 |

|

SU1649674A1 |

| Устройство передачи и приема цифрового телевизионного сигнала | 1987 |

|

SU1506592A2 |

| Устройство сжатия полосы частот видеосигнала | 1979 |

|

SU792609A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ ВЫСОКОЙ ЧЕТКОСТИ | 2000 |

|

RU2194370C2 |

Изобретение относится к технике телевидения. Цель изобретения - повышение точности преобразования. Устр- во содержит блок 1 временных задержек видеосигнала, сумматоры 2, 6, 4, 8, три блока вычитания 3, 5, 7, син- хрогенератор 18. Для достижения цели в устр-во введены четвертый блок вычитания 9, блок 10 сравнения кодов. коммутатор 11, преобразователь 12 параллельного кода в последовательный, инвертор 13, четьфе блока деления 14, 15, 17, 16. В устройстве реализуется быстрое преобразование Адамара четырех кодируемых элементов изображения. При этом осуществляется адаптивное кодирование трех элементов трансформанты Ь, , Ъ2кЪ. Адаптация заключается в выборе передаваемого значения Ь; (i 1,2,3) в зависимости от значения Ьд для каждого кодируемого квартета элементов а, а,, а, и а,. Блок 1 вьгаолнен в виде последовательно-параллельного регистра, который управляется тактовой частотой для записи и сдвига и частотой, в четыре раза меньшей для управления считыванием. 1 ил. сл

| Устройство сжатия полосы частот видеосигнала | 1979 |

|

SU792609A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-05-07—Публикация

1986-10-08—Подача