1

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислителях для генерации произвольной последовательности кодов.

Известны устройства, предназначенные для генерации кодов и содержащие матричную память, реализованную на элементах И и ИЛИ, регистры и счетчики |1, 2. Недостатком этих устройств является сложность конструкции.

Наиболее близким техническим решением к изобретению является генератор кодов {3, содержащий постоянную матричную память, реализованную на элементах И и ИЛИ, адресные регистры и динамические счетчики.

Сложность конструкции этого устройства обусловлена использованием в устройстве двух счетчиков.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что в генератор кодов, содержащий матрицу из р q элементов И, выходы которых соединены со входами L-fl элементов ИЛИ, выходы которых являются выходами генератора кодов (где Л р-(д-1) - количество, а L - разрядность генерируемых кодов) введены два сдвиговых замкнутых регистра, вход сдвига одного из которых подключен к выходу (L-l-l)-ro элемента ИЛИ, вход сдвига другого сдвигового замкнутого регистра - к первой шине управления генератора кодов. Выходы сдвиговых замкнутых регистров подключены к координатным шинам матрицы элементов И, входы установки сдвиговых замкнутых регистров - ко второй шине управления генератора кодов.

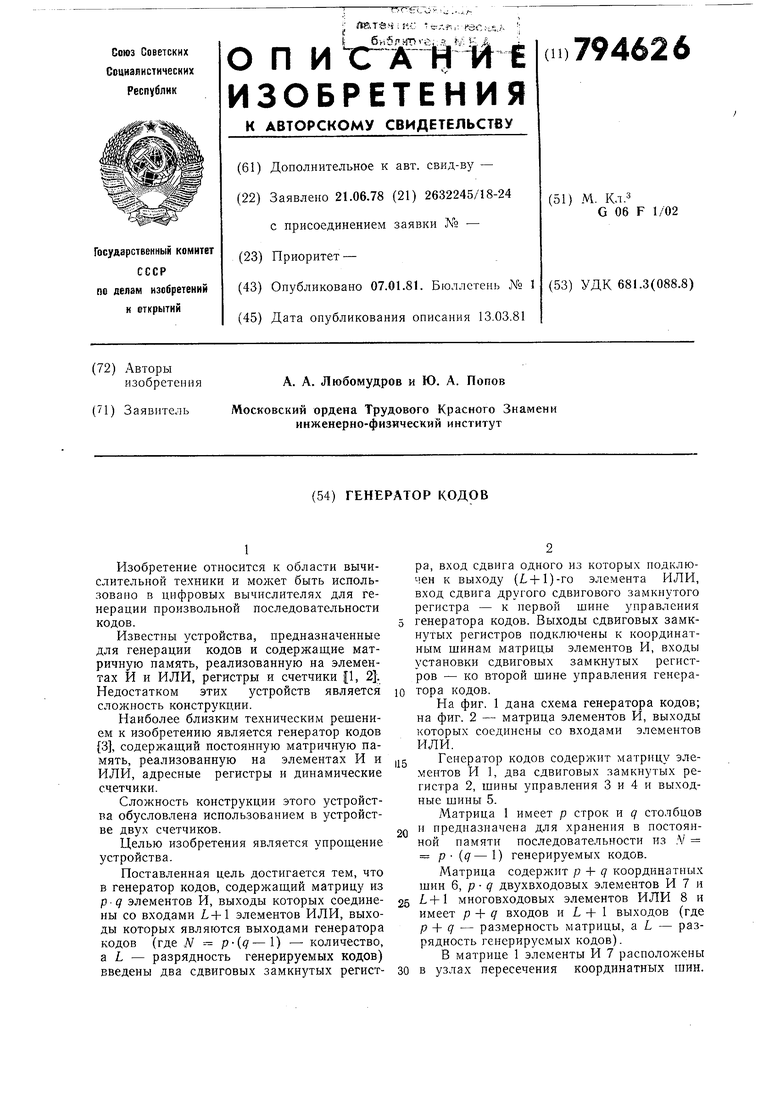

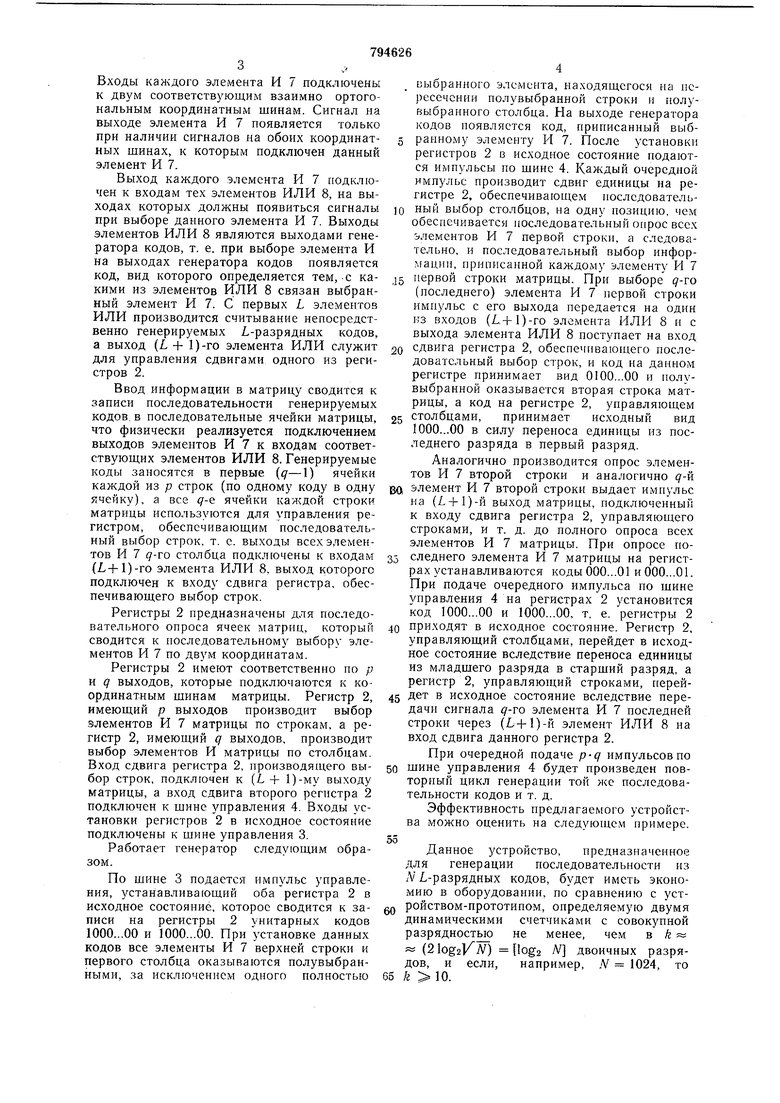

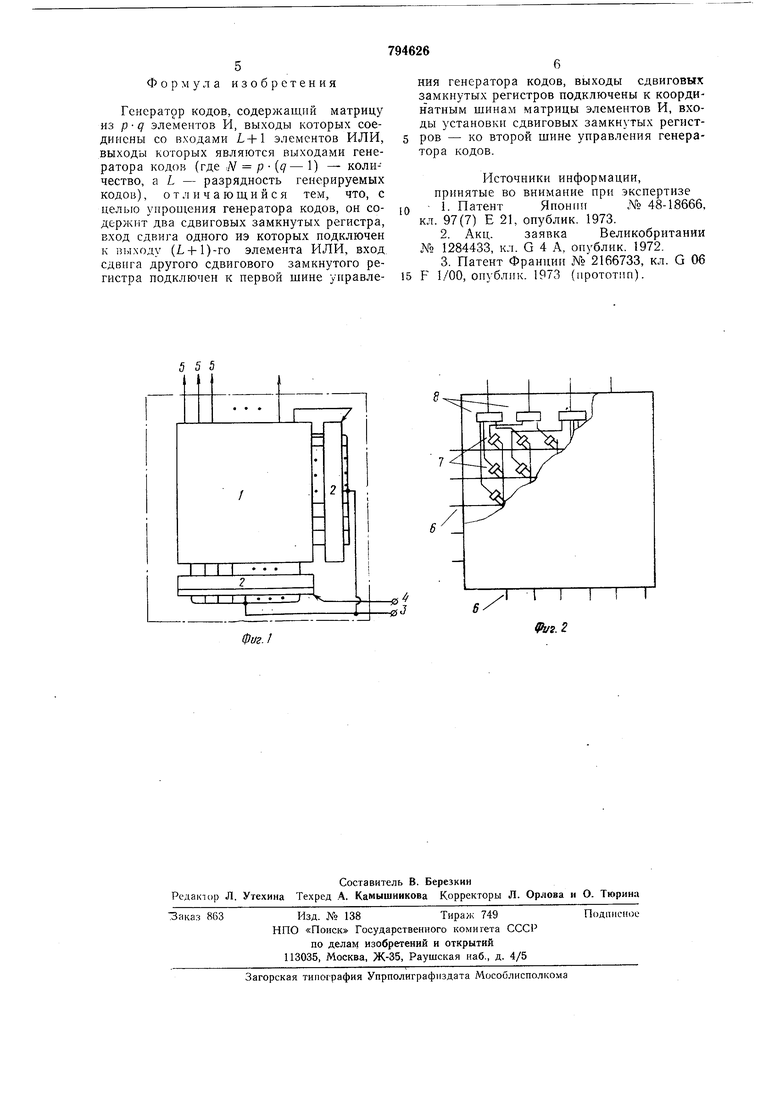

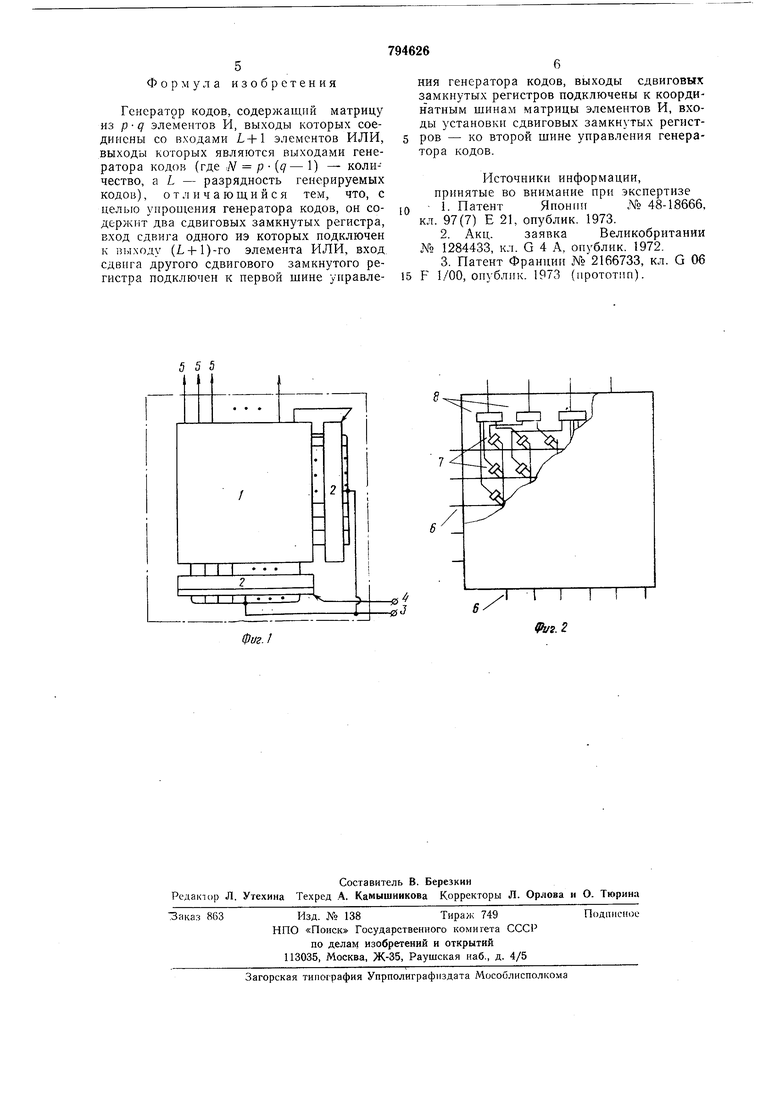

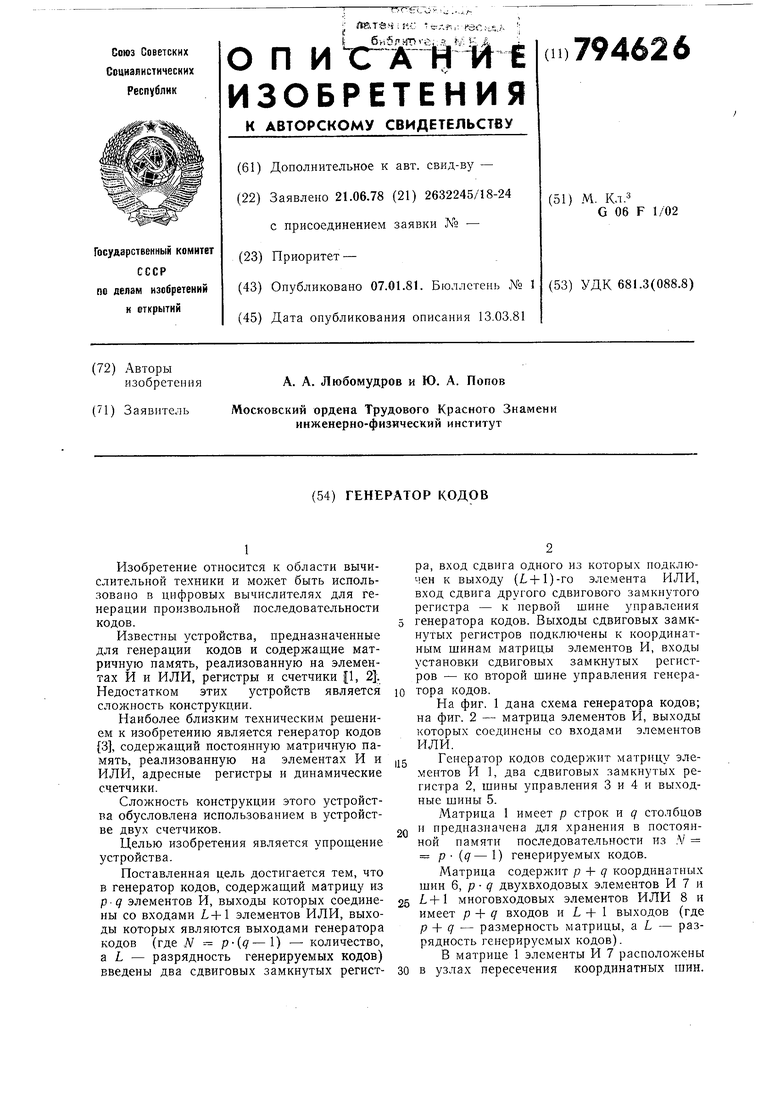

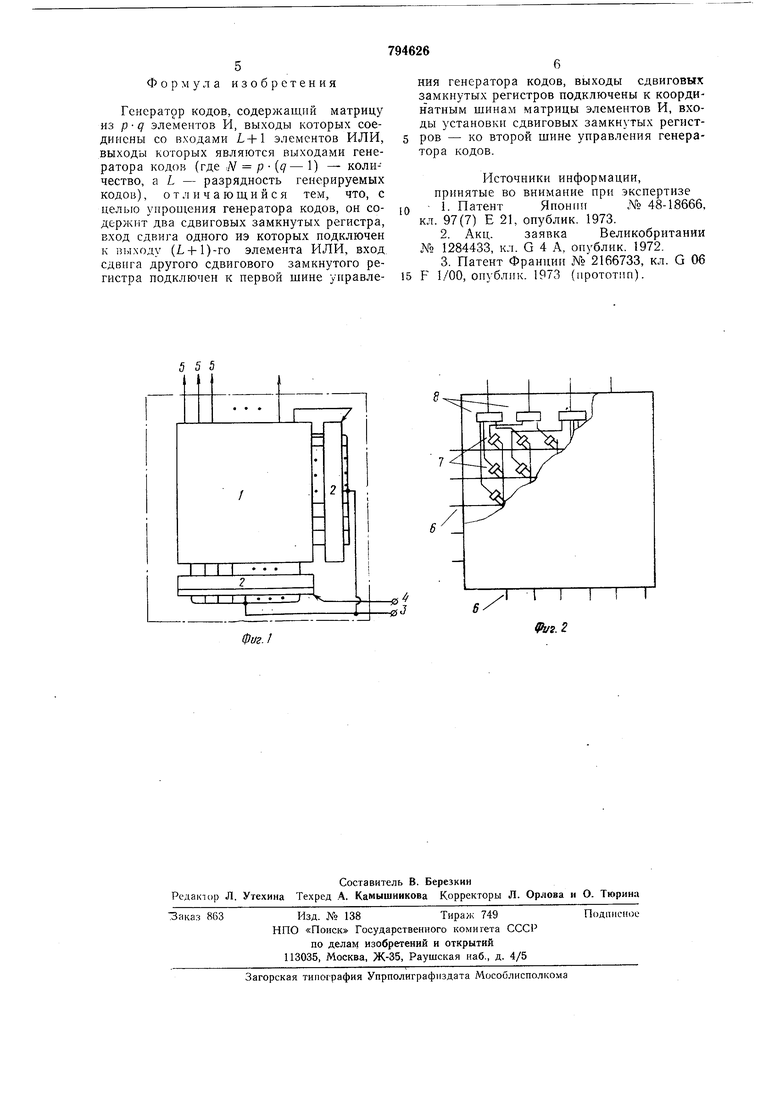

На фиг. 1 дана схема генератора кодов; на фиг. 2 - матрица элементов И, выходы которых соединены со входами элементов ИЛИ.

Генератор кодов содержит матрицу элементов И 1, два сдвиговых замкнутых регистра 2, шины управления 3 и 4 и выходные шины 5.

Матрица 1 имеет р строк и q столбцов и предназначена для хранения в постоянной памяти последовательности из .V р (q-1) генерируемых кодов.

Матрица содержит р + q координатных щин Q, р q двухвходовых элементов И 7 и L+1 многовходовых элементов ИЛИ 8 и имеет р + q входов и L + 1 выходов (где р + q - размерность матрицы, а L - разрядность генерируемых кодов).

В матрице 1 элементы И 7 расположены в узлах пересечения координатных шин.

Входы каждого элемента И 7 подключены к двум соответствующим взаимно ортогональным координатным шинам. Сигнал на выходе элемента И 7 появляется только при наличии сигналов на обоих координатных шинах, к которым подключен данный элемент И 7.

Выход каждого элемента И 7 подключен к входам тех элементов ИЛИ 8, на выходах которых должны появиться сигналы при выборе данного элемента И 7. Выходы элементов ИЛИ 8 являются выходами генератора кодов, т. е. при выборе элемента И на выходах генератора кодов появляется код, вид которого определяется тем, -с какими из элементов ИЛИ 8 связан выбранный элемент И 7. С первых L элементов ИЛИ производится считывание непосредственно генерируемых L-разрядных кодов, а выход (L 4- 1)-го элемента ИЛИ служит для управления сдвигами одного из регистров 2.

Ввод информации в матрицу сводится к записи последовательности генерируемых кодов, в последовательные ячейки матрицы, что физически реализуется подключением выходов элементов И 7 к входам соответствующих элементов ИЛИ 8. Генерируемые коды заносятся в первые (q-1) ячейки каждой из р строк (по одному коду в одну ячейку), а все q-e ячейки каждой строки матрицы используются для управления регистром, обеспечивающим последовательный выбор строк, т. с. выходы всех элементов И 7 q-TO столбца подключены к входам (L+l)-ro элемента ИЛИ 8, выход которого подключен к входу сдвига регистра, обеспечивающего выбор строк.

Регистры 2 предназначены для последовательного опроса ячеек матриц, который сводится к последовательному выбору элементов И 7 по двум координатам.

Регистры 2 имеют соответственно по р и q выходов, которые подключаются к координатным шинам матрицы. Регистр 2, имеющий р выходов производит выбор элементов И 7 матрицы по строкам, а регистр 2, имеющий q выходов, производит выбор элементов И матрицы по столбцам. Вход сдвига регистра 2, производящего выбор строк, подключен к (L + 1)-му выходу матрицы, а вход сдвига второго регистра 2 подключен к щине управления 4. Входы установки регистров 2 в исходное состояние подключены к шине управления 3.

Работает генератор следующим образом.

По щине 3 подается импульс управления, устанавливающий оба регистра 2 в исходное состояние, которое сводится к записи на регистры 2 унитарных кодов 1000...00 и 1000...00. При установке данных кодов все элементы И 7 верхней строки и первого столбца оказываются полувыбранными, за исключением одного полностью

выбранного элемента, находящегося на пересечении полувыбранной строки и полувыбранного столбца. На выходе генератора кодов появляется код, приписанный выбранному элементу И 7. После установки регистров 2 в исходное состояние подаются импульсы по щине 4. Каждый очередной импульс производит сдвиг единицы на регистре 2, обеспечивающем последовательный выбор столбцов, на одну позицию, чем обеспечивается последовательный опрос всех элементов И 7 первой строки, а следовательно, и последовательный выбор информации, приписанной каждому элементу И 7

J5 первой строки матрицы. При выборе -го (последнего) элемента И 7 первой строки импульс с его выхода передается на один КЗ входов (L-f 1)-го элемента ИЛИ 8 и с выхода элемента ИЛИ 8 поступает на вход

0 сдвига регистра 2, обеспечивающего последовательный выбор строк, и код па данном регистре принимает вид 0100...00 и полувыбранной оказывается вторая строка матрицы, а код на регистре 2, управляющем

5 столбцами, принимает исходный вид 1000...00 в силу переноса единицы из последнего разряда в первый разряд.

Аналогично производится опрос элементов И 7 второй строки и аналогично q-K

o элемент И 7 второй строки выдает импульс на (L+)- выход матрицы, подключенный к входу сдвига регистра 2, управляющего строками, и т. д. до полного опроса всех элементов И 7 матрицы. При опросе последнего элемента И 7 матрицы на регистрах устанавливаются коды 000...01 п 000...01. При подаче очередного импульса по щине управления 4 на регистрах 2 установится код 1000...00 и 1000...00, т. е. регистры 2

0 Приходят в исходное состояние. Регистр 2, управляющий столбцами, перейдет в исходное состояние вследствие переноса единицы из младшего разряда в старщий разряд, а регистр 2, управляющий строками, гсерей5 дет в исходное состояние вследствие передачи сигнала -го элемента И 7 последней строки через ( элемент ИЛИ 8 на вход сдвига данного регистра 2.

При очередной подаче p-q импульсов по

0 щине управления 4 будет произведен повторный цикл генерации той же последовательности кодов и т. д.

Эффективность предлагаемого устройства можно оценить на следуюплем примере.

Данное устройство, предназначенное

для генерации последовательности из ЛL-разрядных кодов, будет иметь экономию в оборудовании, по сравнению с устп ройством-прототипом, определяемую двумя динамическими счетчиками с совокупной разрядностью не менее, чем в k ss (2 log2l/./V) {Iog2 Щ двоичных разрядов, и если, например, N - 1024, то

/г 10.

Формула изобретения

Генератор кодов, содержащий матрицу из р элементов И, выходы которых соединены со входами L+1 элементов ИЛИ, выходы которых являются выходами генератора кодов (где ,N р (q- 1) - количество, а L - разрядность генерируемых кодов), отличающийся тем, что, с целью упрощения генератора кодов, он содержит два сдвиговых замкнутых регистра, вход сдвига одного из которых нодключен к у ыходу (L-M)-ro элемента ИЛИ, вход, сдвига другого сдвигового замкнутого регистра подключен к первой шине управлекия генератора кодов, выходы сдвиговых з амкнутых регистров подключены к координатным шинам матрицы элементов И, входы установки сдвиговых замкнутых регистров - ко второй щине управления генератора кодов.

Источники информации, принятые во внимание при экспертизе 1. ПатентЯпонии№ 48-18666,

10

кл. 97(7) Е 21, опублик. 1973.

2.Акц. заявка Великобритании №- 1284433, кл. G 4 А, опублик. 1972.

3.Патент Франции № 2166733, кл. G 06 15 F 1/00, опублик. 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Ассоциативное запоминающее устройство | 1985 |

|

SU1277211A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Накопитель для матричного запоминающего устройства на цилиндрических магнитных доменах | 1985 |

|

SU1304077A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1984 |

|

SU1256084A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для ввода-вывода графической информации | 1987 |

|

SU1603409A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| Устройство для ввода цифровой информации | 1978 |

|

SU769519A1 |

t

фиг.

5

.0 J

fPi/s.2

Авторы

Даты

1981-01-07—Публикация

1978-06-21—Подача