1

Изобретение относится к области вычислительной техники и может быть использовано для программирования способом «Bf iжигания матриц постоянных заломинающих устройств (ПЗУ) на больших интегральных схемах (БИС) с нихромовыми связями, а также резисторных матриц ПЗУ с плавкими связями различных устройств и систем, предназначенных для автоматизации научных исследований в области биологии, а также в автоматике, радиотехнике, телеметрии и т. д.

До недавнего времени программирование матриц ПЗУ на БИСах осуществлялось на технологическом уровне заводом-изготовителем ПЗУ, а потребитель получал готовые ПЗУ с фиксированной информацией. В на-стоящее время как у нас в стране, так и за рубежом подготавливаются к серийному выпуску матрицы на БИСах с нихромовыми связями, а также резисторные матрицы ПЗУ с плавкими связями, содержащие все элементы памяти. Освоение данных матриц .ПЗУ позволит потребителю самому фиксировать в матрицах требуемую информацию способом «выжигаиия связей, что даст большой экономический эффект и увеличит сферу использования и гибкость в применении матриц ПЗУ на БИСах 1.

Однако устройства для автоматического программирования матриц ПЗУ способом «выжигания связей не известны.

Известно устройство для ручного «выжигания связей резисторных матриц ПЗУ с плавкими связями 2.

Оно содержит тумблеры, одни концы которых объединены и соединены с шиной питания, а другие соединены с соответствующими первыми входами резисторной матрицы ПЗУ с плавкими связями, стрелочный прибор типа миллиамперметра, один контакт которого подключен к одному из вторых входов резисторной матрицы, а другой - через источник питания к щине нулевого потенциала.

Устройство позволяет проводить программирование резисторных матриц ручным переключением соответствующих тумблер.ов.

Однако оно не позволяет проводить автоматическое программирование матриц ПЗУ способом «выжигания ; имеет низкую производительность труда; затрудняет программирование матриц с большим объемом

информации; не обеспечивает контроля достоверности информации и ее защиты и не обеспечивает проведения автоматического условного перехода по признаку «конец выжигания к следующему адресу программы.

Наиболее близким из известных цо технической сущности к изобретению является устройство для управления подпрограммами, содержащее блок памяти, блок сравнения, регистры начального и конечного адресов подпрограммы, блоки элементов И, переключатели режимов и счетчик номеров команд, выход которого подключен к входу блока памяти и первым входам блоков сравнения. Второй вход первого блока сравнения соединен с выходом регистра конечного адреса подпрограммы. Выход регистра начального адреса подпрограммы через первый блок элементов И соединен с первым входом счетчика номеров команд. Управляющий вход первого блока элементов И через переключатель режимов подключен к выходу второго блока сравнения. Выход регистра адресов команды перехода подключен к второму входу второго блока сравнения и через второй блок элементов И к второму входу счетчика номеров команд. Управляющий вход второго блока элементов И соединен с выходом первого блока сравнения. Блок памяти содержит дешифратор адресов, первый блок адресных усилителей, входы которого соединены с выходами дешифратора адресов, первый блок накопителей, одни входы которого соединены с выходами первого блока адресных усилителей, первый блок разрядных усилителей, выходы которого соединены с другими входами первого блока накопителей информации, а входы первого блока разрядных усилителей соединены с выходами пульта управления, блок сравнения, блок схем И и счетчик адресов 3.

Это устройство не позволяет осушествлять автоматическое программирование потребителем матриц ПЗУ на БИСах способом «выжигания связей; обеспечить достаточную достоверность и защиту информации при программировании матриц ПЗУ способом «выжигания связей; формировать признаки «конец выжигания и осуществлять условный переход по этому признаку к следующему адресу программы.

Целью изобретения является расширение области применения устройства за счет осуществления программирования потребителем, повышения достоверности и надежности записи.

Поставленная цель достигается тем, что в устройство для программирования блоков постоянной памяти, содержащее счетчик адресов, первый вход которого соединен с первым выходом пульта управления, дешифратор адреса, одни из входов которого соединены со вторыми выходами пульта управления, другой вход дешифратора адреса подключен к второму входу счетчика адресов и первому выходу блока управления, связанный с пультом управления, первый блок адресных усилителей, входы которого соединены с выходами дешифратора адреса, первый блок памяти, одни из входов которого соединены с выходами первого блока адресных усилителей, блок сравнения, первые входы которого соединены с выходами первого блока памяти и первыми входами блока элементов И, второй вход блока элементов И подключен к первому выходу блока сравнения, второй выход которого связан с блоком управления и пультом управления, выходы блока элементов И соединены с разрядными шинами и третьими выходами пульта управления, шину нулевого потенциала и шину питания, введены второй адресный блок усилителей, второй блок памяти, два блока разрядных усилителей, блок расширителей импульсов, два блока токовых ключей, элемент ИЛИ-НЕ и ограничительный элемент, один вывод которого соединен с шиной нулевого потенциала, а другой вывод - с первым выходом первого блока токовых ключей н одним из входов элемента ИЛИ-НЕ. Вторые выходы первого блока токовых ключей и выходы второго блока токовых ключей соединены с выходами устройства. Первый вход второго блока токовых ключей соединен с шиной питания. Вторые входы второго блока токовых ключей и входы первого блока токовых ключей соединены с выходами блока расширителей импульсов, входы которого соединены с выходами блока элементов И. Выходы блоков разрядных усилителей соединены соответственно с другими входами первого блока памяти и одними из входов второго блока памяти, выходы которого подключены к вторым входам блока сравнения. Входы второго блока памяти соединены с выходами второго блока адресных усилителей, входы которого соединены с

выходами дешифратора адреса. Вторые входы блоков разрядных усилителей соединены с третьими выходами пульта управления и разрядными шинами. Третьи входы блоков разрядных усилителей связаны с

блоком упраэления.

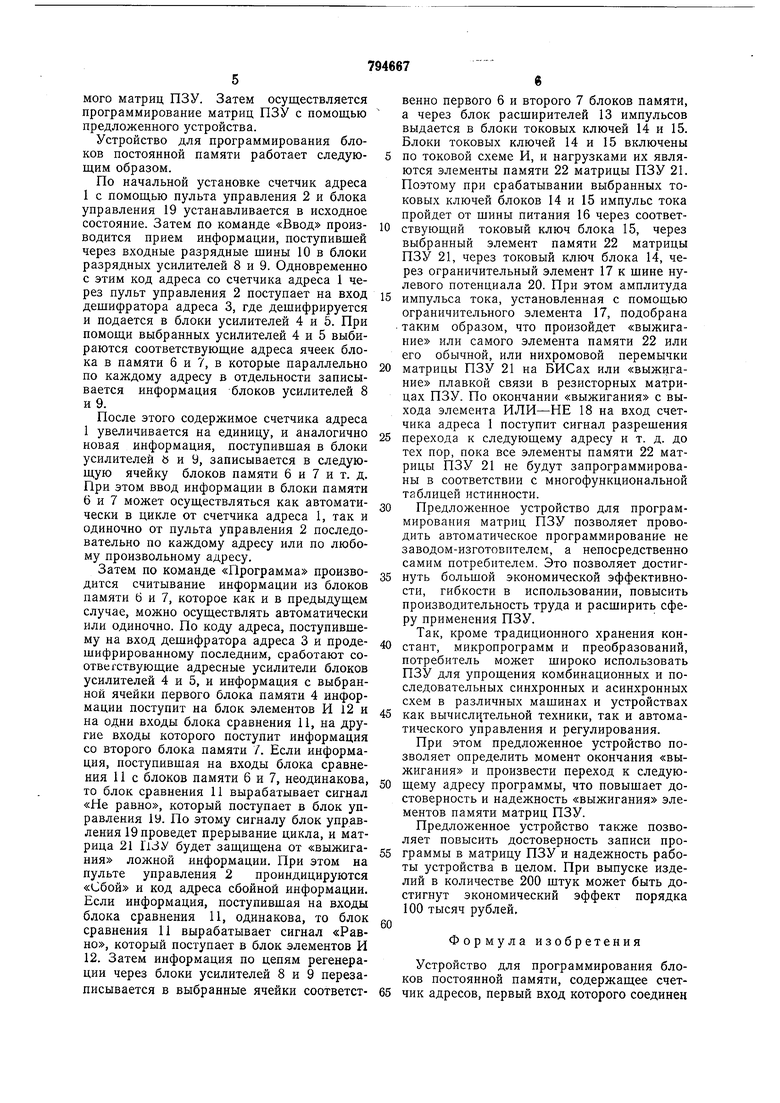

На чертеже изображена функциональная схема предложенного устройства.

Оно содержит счетчик адресов 1, пульт управления 2, дешифратор адресов 3, блоки

усилителей 4 и 5, блоки памяти 6 и 7, блоки разрядных усилителей 8 и 9, разрядные шины 10, блок сравнения И, блок элементов И 12, расширитель импульсов 13, блоки токовых ключей 14 и 15, шину питания 16, ограничительный элемент 17, элемент ИЛИ - НЕ 18, блок управления 19, шину нулевого потенциала 20.

Перед началом работы потребитель матриц (ПЗУ) на (БИСах) с обычными или

нихромовыми перемычками или матриц резисторного И ПЗУ с плавкими связями, в соответствии с требуемой программой хранения постоянной информации, составляет, многофункциональные таблицы истинности,

которые являются спецификацией содержимог о матриц ПЗУ. Затем осуществляется программирование матриц ПЗУ с помощью предложенного устройства.

Устройство для программирования блоков постоянной памяти работает следующим образом.

По начальной установке счетчик адреса 1 с помощью пульта управления 2 и блока управления 19 устанавливается в исходное состояние. Затем по команде «Ввод производится прием информации, поступившей через входные разрядные шины 10 в блоки разрядных усилителей 8 и 9. Одновременно с этим код адреса со счетчика адреса 1 через пульт управления 2 поступает на вход дешифратора адреса 3, где дешифрируется и подается в блоки усилителей 4 и 5. При помощи выбранных усилителей 4 и 5 выбираются соответствующие адреса ячеек блока в памяти 6 и 7, в которые параллельно по каждому адресу в отдельности записывается информация блоков усилителей 8 и 9.

После этого содержимое счетчика адреса 1 увеличивается на единицу, и аналогично новая информация, поступившая в блоки усилителей 6 и 9, записывается в следующую ячейку блоков памяти 6 и 7 и т. д. При этом ввод информации в блоки памяти 6 и 7 может осуществляться как автоматически в цикле от счетчика адреса 1, так и одиночно от пульта управления 2 последовательно по каждому адресу или по любому произвольному адресу.

Затем по команде «Программа производится считывание информации из блоков памяти б и 7, которое как и в предыдущем случае, можно осуществлять автоматически или одиночно. По коду адреса, поступившему на вход дешифратора адреса 3 и продешифрированному последним, сработают соответствующие адресные усилители блоков усилителей 4 и 5, и информация с выбранной ячейки первого блока памяти 4 информации поступит на блок элементов И 12 и на одни входы блока сравнения 11, на другие входы которого поступит информация со второго блока памяти /. Если информация, поступившая на входы блока сравнения И с блоков памяти 6 и 7, неодинакова, то блок сравнения 11 вырабатывает сигнал «Не равно, который поступает в блок управления 19. По этому сигналу блок управления 19 проведет прерывание цикла, и матрица 21 ПЗУ будет защищена от «выжигания ложной информации. При этом на пульте управления 2 проиндицируются «Сбой и код адреса сбойной информации. Если информация, поступившая на входы блока сравнения И, одинакова, то блок сравнения И вырабатывает сигнал «Равно, который поступает в блок элементов И 12. Затем информация по цепям регенерации через блоки усилителей 8 и 9 перезаписывается в выбранные ячейки соответственно первого 6 и второго 7 блоков памяти, а через блок расширителей 13 импульсов выдается в блоки токовых ключей 14 и 15. Блоки токовых ключей 14 и 15 включены

по токовой схеме И, и нагрузками их являются элементы памяти 22 матрицы ПЗУ 21. Поэтому при срабатывании выбранных токовых ключей блоков 14 и 15 импульс тока пройдет от шины питания 16 через соответствующий токовый ключ блока 15, через выбранный элемент памяти 22 матрицы ПЗУ 21, через токовый ключ блока 14, через ограничительный элемент 17 к шине нулевого потенциала 20. При этом амплитуда

импульса тока, установленная с помощью ограничительного элемента 17, подобрана таким образом, что произойдет «выжигание или самого элемента памяти 22 или его обычной, или нихромовой перемычки

матрицы ПЗУ 21 на БИСах или «выжигание плавкой связи в резисторных матрицах ПЗУ. По окончании «выжигания с выхода элемента ИЛИ-ПЕ 18 на вход счетчика адреса 1 поступит сигнал разрешения

перехода к следующему адресу и т. д. до тех пор, пока все элементы памяти 22 матрицы ПЗУ 21 не будут запрограммированы в соответствии с многофункциональной таблицей истинности.

Предложенное устройство для программирования матриц ПЗУ позволяет проводить автоматическое программирование не заводом-изготовителем, а непосредственно самим потребителем. Это позволяет достигнуть большой экономической эффективности, гибкости в использовании, повысить производительность труда и расширить сферу применения ПЗУ. Так, кроме традиционного хранения констант, микропрограмм и преобразований, потребитель может широко использовать ПЗУ для упрощения комбинационных и последовательных синхронных и асинхронных схем в различных машинах и устройствах

как вычислительной техники, так и автоматического управления и регулирования.

При этом предложенное устройство позволяет определить момент окончания «выжигания и произвести переход к следующему адресу программы, что повышает достоверность и надежность «выжигания элементов памяти матриц ПЗУ.

Предложенное устройство также позволяет повысить достоверность записи программы в матрицу ПЗУ и надежность работы устройства в целом. При выпуске изделий в количестве 200 штук может быть достигнут экономический эффект порядка 100 тысяч рублей.

Формула изобретения

Устройство для программирования блоков постоянной памяти, содержащее счетчик адресов, первый вход которого соединен

| название | год | авторы | номер документа |

|---|---|---|---|

| Программатор для записи информации в полупроводниковые элементы памяти | 1985 |

|

SU1280449A2 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Программатор | 1987 |

|

SU1541669A1 |

| Имитатор канала | 1984 |

|

SU1239719A2 |

| Имитатор канала | 1985 |

|

SU1287160A1 |

| Имитатор канала | 1985 |

|

SU1280633A2 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Имитатор канала | 1988 |

|

SU1520523A2 |

| Логический анализатор | 1983 |

|

SU1170458A1 |

| Устройство для программирования постоянных запоминающих устройств | 1985 |

|

SU1372354A1 |

Авторы

Даты

1981-01-07—Публикация

1979-02-12—Подача