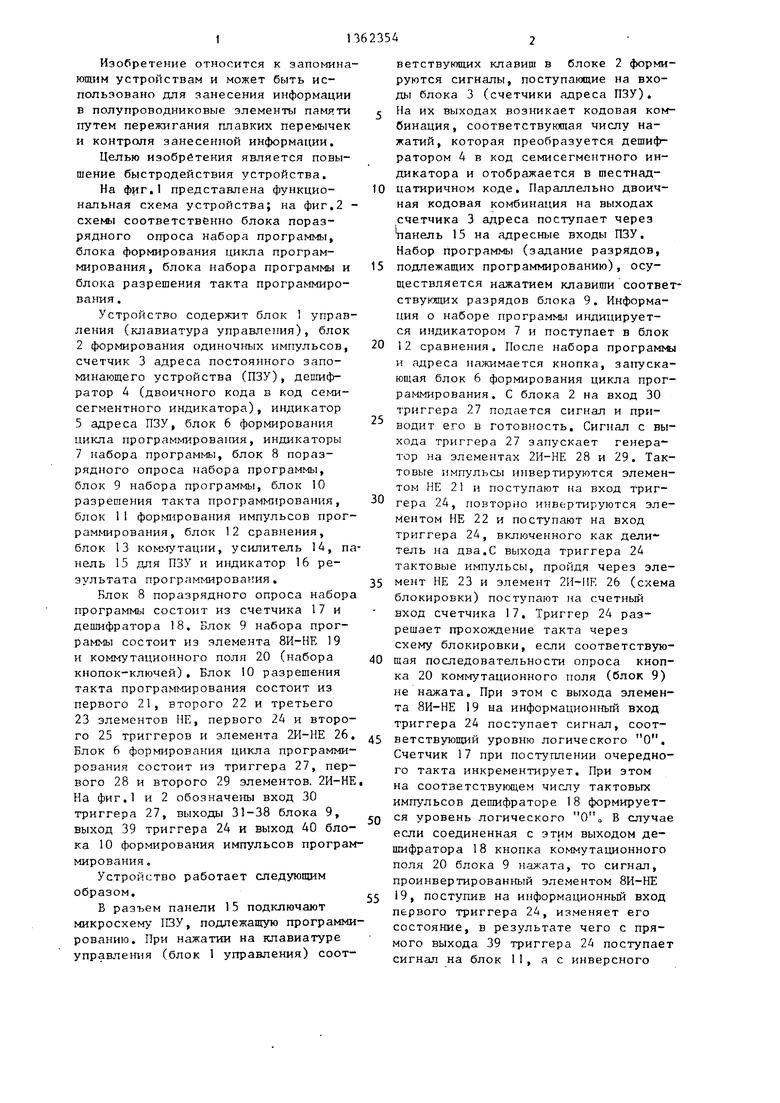

Фиг.1

Изобретение относится к запоминающим устройствам и может быть использовано для занесения информации в полупроводниковые элементы памяти путем пережигания плавких перемычек и контроля занесенной информации.

Целью изобретения является повышение быстродействия устройства.

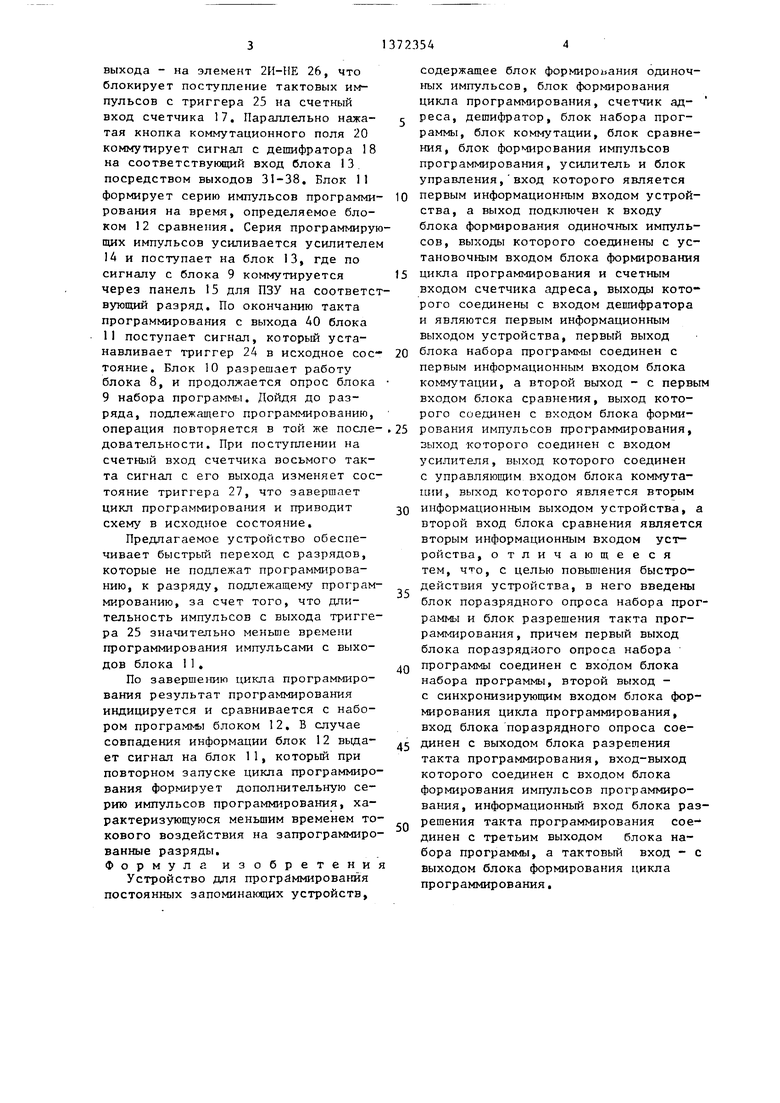

На фиг.1 представлена функцио- нальная схема устройства; на фиг.2 - схемы соответственно блока поразрядного опроса набора программы, блока формирования цикла программирования, блока набора программы и блока разрешения такта программирования .

Устройство содержит блок 1 управления (клавиатура управления), блок 2 формирования одиночных импульсов, счетчик 3 адреса постоянного запоминающего устройства (ПЗУ), дешифратор А (двоичного кода в код семи- сегментного индикатора), индикатор 5 адреса ПЗУ, блок 6 формирования цикла программирования, индикаторы 7 набора программы, блок 8 поразрядного опроса набора программы, блок 9 набора программы, блок 10 разрешения такта программирования, блок 11 форьшрования импульсов программирования, блок 12 сравнения, блок 13 ком гутации, усилитель 14, панель 15 для ПЗУ и индикатор 16 результата программировавши,

Блок 8 поразрядного опроса набора программы состоит из счетчика 17 и дешифратора 18. Блок 9 набора программы состоит из элемента 8И-НЕ 19 и коммутационного поля 20 (набора кнопок-ключей). Блок 10 разрешения такта программирования состоит из первого 21, второго 22 и третьего 23 элементов НЕ, первого 24 и второго 25 триггеров и элемента 2И-НЕ 26. Блок 6 формирования цикла программирования состоит из триггера 27, первого 28 и второго 29 элементов. 2И-НЕ На фиг.1 и 2 обозначены вход 30 триггера 27, выходы 31-38 блока 9, выход 39 триггера 24 и выход 40 блока 10 формирования импульсов программирования ,

Устройство работает следующим образом.

В разъем панели 15 подключают микросхему ПЗУ, подлежащую программированию. При нажатии на клавиатуре управления (блок 1 управления) соот

25

10 15

20 30 5

40

5

ветствуюпшх клавиш в блоке 2 формируются сигналы, поступающие на входы блока 3 (счетчики адреса ПЗУ). На их выходах возникает кодовая комбинация, соответствующая числу нажатий, которая преобразуется дешифратором 4 в код семисегментного индикатора и отображается в шестнадцатиричном коде. Параллельно двоичная кодовая комбинация на выходах счетчика 3 адреса поступает через Т1анель 15 на адресные входы ПЗУ. Набор программы (задание разрядов, подлежащих программированию), осуществляется нажатием клавиши соответствующих разрядов блока 9. Информация о наборе программы индицируется индикатором 7 и поступает в блок 12 сравнения, После набора программа и адреса нажимается кнопка, запускающая блок 6 формирования цикла программирования. С блока 2 на вход 30 триггера 27 подается сигнал и приводит его в готовность. Сигнал с выхода триггера 27 запускает генератор на элементах 2И-НЕ 28 и 29. Тактовые импульсы инвертируются элементом НЕ 21 и поступают на вход триггера 24, повторно инвертируются элементом НЕ 22 и поступают на вход триггера 24, включенного как делитель на два.С выхода триггера 24 тактовые импульсы, пройдя через элемент НЕ 23 и элемент 2И-НЕ 26 (схема блокировки) поступают на счетньш вход счетчика 17. Триггер 24 разрешает прохождение такта через схему блокировки, если соответствующая последовательности опроса кнопка 20 коммутационного поля (блок 9) не нажата. При этом с выхода элемента 8И-НЕ 19 ыа информационный вход триггера 24 поступает сигнал, соответствующий уровню логического О. Счетчик 17 при поступлении очередного такта инкрементирует. При этом на соответствующем числу тактовых импульсов дешифраторе 18 формируется уровень логического О В случае если соединенная с этим выходом дешифратора 18 кнопка коммутационного поля 20 блока 9 нажата, то сигнал, проинвертированный элементом 8И-НЕ 19, поступив на информационный вход первого триггера 24, изменяет его состояние, в результате чего с прямого выхода 39 триггера 24 поступает сигнал на блок 11, а с инверсного

выхода - на элемент 2И-НЕ 26, что блокирует поступление тактовых импульсов с триггера 25 на счетный вход счетчика 17. Параллельно нажа- тая кнопка коммутационного поля 20 коммутирует сигнал с дешифратора 18 на соответствующий вход блока 13 посредством выходов 31-38. Блок 11 формирует серию импульсов программи- рования на время, определяемое блоком 12 сравнения. Серия программирующих импульсов усиливается усилителем 1А и поступает на блок 13, где по сигналу с блока 9 коммутируется

через панель 15 для ПЗУ на соответствующий разряд. По окончанию такта программирования с выхода 40 блока II поступает сигнал, который устанавливает триггер 24 в исходное сое- тояние. Блок 10 разрешает работу блока 8, и продолжается опрос блока 9 набора программы. Дойдя до разряда, подлежащего програм шрованию, операция повторяется в той же последовательности. При поступлении на счетный вход счетчика восьмого такта сигнал с его выхода изменяет состояние триггера 27, что завершает цикл программирования и приводит

схему в исходное состояние.

Предлагаемое устройство обеспечивает быстрый переход с разрядов, которые не подлежат программированию, к разряду, подлежащему программированию, за счет того, что длительность импульсов с выхода триггера 25 значительно меньше времени программирования импульсами с выходов блока 11.

По завершению цикла программирования результат программирования индицируется и сравнивается с набором программы блоком 12. В случае совпадения информации блок 12 выда- ет сигнал на блок 11, который при повторном запуске цикла программирования формирует дополнительную серию импульсов программирования, характеризующуюся меньшим временем токового воздействия на запрограммированные разряды. Формула изобретени

Устройство для программирования постоянных запоминаюсцих устройств,

0 5 Q

д

0

содержащее блок формирования одиночных импульсов, блок формирования цикла программирования, счетчик ад- раса, дешифратор, блок набора программы, блок коммутации, блок сравнения, блок формирования импульсов программирования, усилитель и блок управления, вход которого является первым информационным входом устройства, а выход подключен к входу блока формирования одиночных импульсов, выходы которого соединены с установочным входом блока формирования цикла программирования и счетным входом счетчика адреса, выходы которого соединены с входом дешифратора и являются первым информационным выходом устройства, первый выход блока набора программы соединен с первым информационным входом блока коммутации, а второй выход - с первым входом блока сравнения, выход которого соединен с входом блока формирования импульсов программирования, выход которого соединен с входом усилителя, выход которого соединен с управляющим входом блока коммутации, выход которого является вторым информационным выходом устройства, а второй вход блока сравнения является вторым информационным входом устройства, отличающееся тем, что, с целью повьшшния быстродействия устройства, в него введены блок поразрядного опроса набора программы и блок разрешения такта программирования, причем первый выход блока поразрядного опроса набора программы соединен с входом блока набора программы, второй выход - с синхронизируюш;им входом блока формирования цикла программирования, вход блока поразрядного опроса соединен с выходом блока разрешения такта программирования, вход-выход которого соединен с входом блока формирования импульсов программирования, информационный вход блока разрешения такта программирования сое- динен с третьим выходом блока набора программы, а тактовый вход - с выходом блока формирования цикла программирования.

Xj

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1989 |

|

RU2047920C1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

Изобретение относится к запоминающим устройствам и может быть использовано для занесения информации в полупроводниковые элементы памяти путем пережигания плавких перемычек и контроля занесенной информации. Цель изобретения - повышение быстродействия устройства. Устройство содержит блок 1 управления (клавиатура управления), блок 2 формирования одиночных импульсов, счетчик 3 адреса ПЗУ, дешифратор 4 (двоичного кода в код семисегментного индикатора) , индикатор 5 адреса ПЗУ, блок 6 формирования цикла щ)ограм О1рова- ния, индикаторы 7 набора программы, блок 8 поразрядного опроса набора программы, блок 9 набора программы, блок 10 разрешения такта программирования, блок 11 формирования импульсов программирования, блок 12 сравнения, блок 13 коммутации, усилитель 14, панель 15 для ПЗУ, индикатор 16 результата программирования. По завершении цикла программирования результат программирования индицируется и сравнивается с набором программы блоком 12. В случае совпадения информации блок 12 выдает сигнал на блок 11, который при повторном запуске цикла программировд- ния формирует дополнительную серию импульсов программирования, характеризующуюся меньшим временем токового воздействия на запрограммированные разряды. 2 ил. (Л со ND СО СЛ 4

| ВИСЯЧИЙ ШКВОРНЕВОЙ ЗАМОК | 1924 |

|

SU1040A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

Авторы

Даты

1988-02-07—Публикация

1985-07-01—Подача