тельностей, первогб и второго блоков памяти обратной связи, пятым информационным входом коммутатора, шестой информационный вход последнего соеди нен с выходом первого блока ключей, который является выходом контрольных сигналов второго уровня анализатора, входы первого блока ключей соединены с выходами первого, второго и третье го блоков памяти последовательностей входы включения первого, второго и третьего блоков ключей соединены с одноименным выходом блока управления информационные входы блоков памяти последовательностей и памяти обратно связи и второго блока ключей соединены с информационным выходом блока усилителей, входы записи всех блоков памяти последовательностей и блоков обратной связи соединены с выходом второго строба записи в память блока управления, выходы первого, второго, третьего и четвертого блоков элементов повторителей, первый, второй, третий и четвертый выходы второго блока ключей объединены поразрядно между собой и соединены с соответствующими разрядами информационных входов регистра адреса и третьего блока ключей, выходы которого являют ся выходами контрольных сигналов пер вого уровня анализатора, выходы первого и второго блоков памяти обратной связи соединены поразрядно соответственно с пятым и шестым выходами второго блока ключей и соединены с пятым и шестым разрядами информацион ного входа регистра адреса, причем блок управления содержит мультивибратор, первый, второй, третий, четвертый и пятьй элементы ИЛИ-НЕ, триг гер, блок постоянной памяти, регистр дешифратор, первый, второй, третий и четвертый элементы НЕ, с первого по пятый элементы И)С первого по четвертый элементы задержки, первый и второй элементы И-НЕ, первый и второй формирователи одиночных импульсов, причем вход запуска мультивибратора, первый вход первого эле,мента И-НЕ и вход первого элемента НЕ являются входом режима работы группы входов управления режимами ра боты блока управления, первые входы первого и второго элементов ИЛИ-НЕ, установочный вход триггера, соединенный с входом регистра, первый адресный вход блока постоянной памяти 1 8 соединены соответственно с входами режимов чтения, записиj обмена и блокировки группы входов управления режимами работы блока управления, выход мультивибратора соединен с первьми входами первого и второго элементов И, второго элемента И-НЕ и вторым входом первого элемента И-НЕ, выход которого соединен с первым входом третьего элемента И, а второй вход этого элемента - с выходом второго формирователя одиночных импульсов, выход третьего элемента И является выходом строба записи в счетчик блока управления, выход первого элемента ИЛИ-НЕ соединен с входом второго элемента НЕ, первыми входами третьего элемента ИЛИ-НЕ, четвертого; и пятого элементов И, выход второго элемента ИЛИ-НЕ соединен с вторым входом третьего элемента ИЛИ-НЕ, выход последнего связан с входом третьего элемента НЕ, выход которого и выход третьего элемента ИЛИ-НЕ являются выходом разрешения приема информации блока управления, выход триггера соединен с вторыми входами первого и второго элементов ИЛИ-НЕ и первым входом дешифратора, второй вход которого соединен с выходом первого элемента НЕ, вторым входом пятого элемента И и является выходом разрешения включения ключей блока управления, выход второго элемента НЕ .соединен с третьим входом дешифратора, первыми входами четвертого и пятого элементов ИЛИ-НЕ, соединенный вторыми входами с первым и вторым выходами дешифратора соответственно, третий выход дешифратора связан с входами четвертого элемента НЕ и первого элемента задержки, выходы которых соединены с вторыми входами четвертого и пятого элементов И соответственно, выходы четвертого и первого элементов И являются выходами первого строба записи в память, четвертый выход дешифратора соединен с входом второго элемента задержки, связанного выходом с вторым входом второго элемента И, выход которого и выход пятого элемента И являются выходом второго строба записи в память блока управления, выход четвертого элемента ИЛИ-НЕ соединен с входом первого формирователя, выход которого соединен с вторым входом второго элемента И-НЕ,

выход последнего связан с входом (Третьего элемента задержки, выходом соединенного с входом четвертого элемента задержки, выход которого и выход третьего элемента задержки являются выходом строба записи в регистр адреса блока управления, вход задания состояния блока управления соединен с вторым адресным входом

70458

блока постоянной памяти и информационным входом регистра состояния, тактовый вход которого соединен с первым выходом блока постоянной памяти, второй выход этого блока связан с сбросовым входом триггера, выход регистра состояния соединено четвертым в ход ом дешифратора и является выходом управления коммутатором блока управления .

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1989 |

|

SU1667090A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Система для контроля микропроцессорных устройств | 1983 |

|

SU1228108A1 |

| Программируемое постоянное запоминающее устройство с контролем | 1979 |

|

SU951398A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для генерирования кодов заданного веса | 1985 |

|

SU1275413A1 |

ЛОГИЧЕСКИЙ АНАЛИЗАТОР, содержащий счетчик, блок усилителей, первый и второй блоки памяти, блок управления, причем информационный вход счетчика является входом .анализируемых сигналов анализатора,вход разрешения записи счетчика соединен с одноименным выходом блока усилителей, счетньй вход счетчика соединен с тактовым выходом блока управления , а выход счетчика - с адресными входами первого и второго блоков памяти, информационные входы которых и вход задания состояния блока управления соединены с первым информационным выходом блока усилителей, выходы управления режимами работы этого блока соединены с одно 1менными входами блока управления, вход разрешения приема информации блока усилителей соединен с одноименным выходом блока управления, группа входов режимов работы, первый информационный вход и второй информационный выход блока усилителей являются соответственно информационными входами и выходом анализатора, отличающийся тем, что, с целью расширения области применения путем обеспечения возможности обнаружения заданной последовательности кодов из входного потока, в него введены третий и четвертый блоки памяти, регистр адреса, первый, второй и .третий блоки ключей, коммутатор, первьй, второй и третий блоки памяти последовательностей, первый и второй блоки памяти обратной связи, первьм, второй, третий и четвертый i блоки элементов повторителей, причем адресные входы третьего и четверто(Л го блоков памяти соединены с выходами счетчика, входы данных третьего и четвертого блоков памяти соединены с первым информационньм выходом блока усилителей, вход записи первого, ; второго, третьего и четвертого блоков памяти связаны с первым выходом ,строба записи в память блока управления, выходы первого, второго, третьего и четвертого блоков памяти соединены с входами соответствующих ел блоков элементов повторителей и с первым, вторым, третьим к четвертым 00 информационными входами коммутатора, управляющий вход которого соединен с выходом разрешения передачи блока управления, а выход коммутатора соединен с вторым информационным- входом блока усилителей, выход строба записи адреса блока управления соединен с тактовым входом регистра адреса, а выход этого регистра - с адрес ными входами первого, второго и третьего блоков памяти последова

1

Изобретение относится к вычислительной технике, а именно к устройствам контроля и диагностики ЭВМ.

Целью изобретения является расширение области применения путем обеспечения возможности обнаружения заданной последовательности кодов из входного потока.

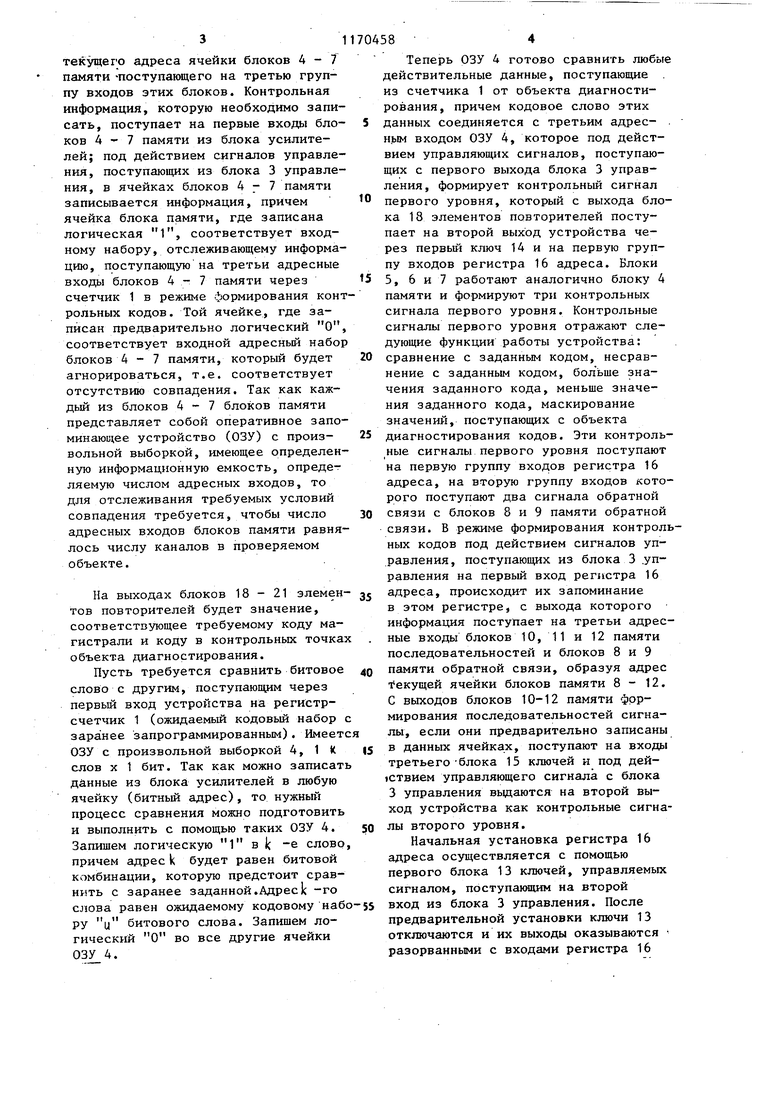

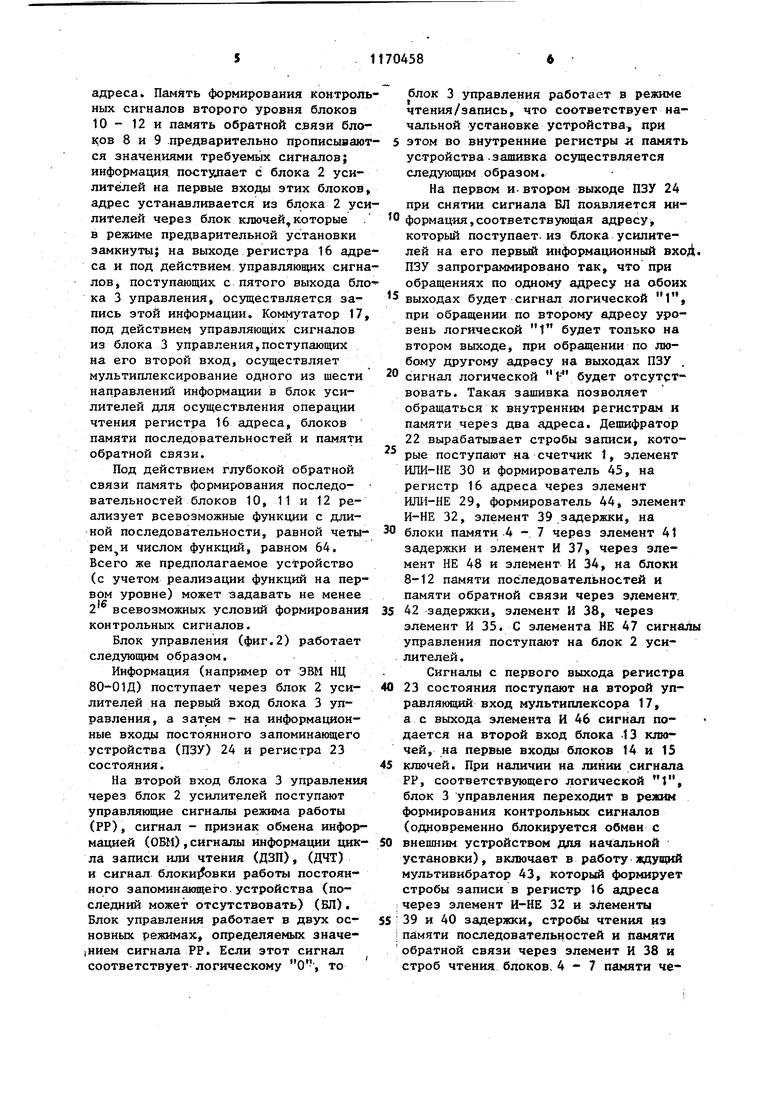

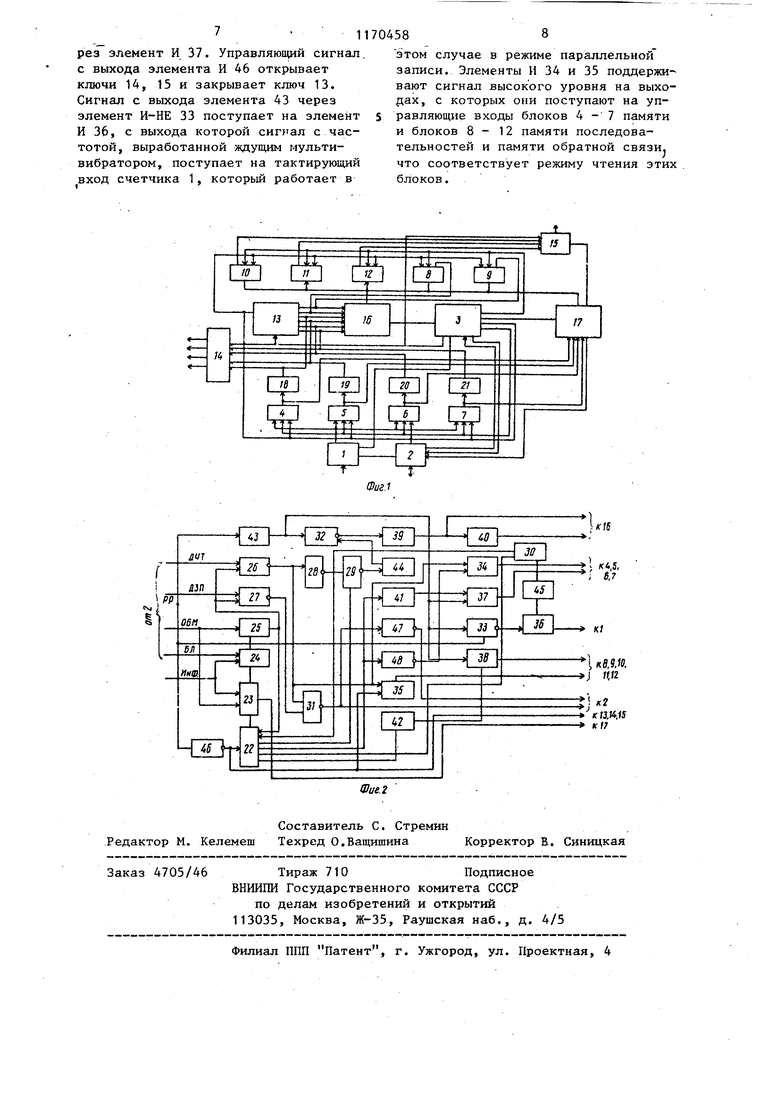

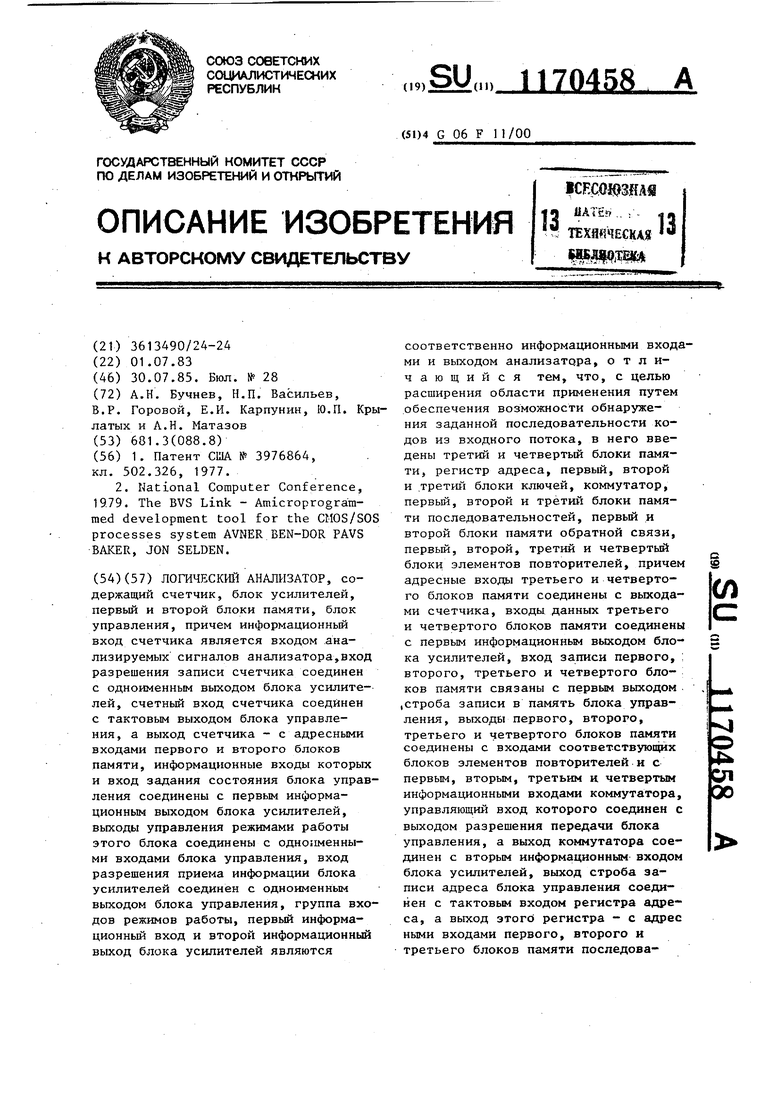

На фиг. 1 представлена блок-схема устройства логического анализатора; на фиг.2 - функциональная схема блок управления логического анализатора.

Логический анализатор содержит счетчик 1, блок 2 усилителей, блок 3 управления, четыре блока 4-7 памяти, два блока 8 и 9 памяти обратной связи, три блока 10, 11 и 12 памяти последовательностей, три блока 13, 14 и 15 ключей, регистр 16 адреса, коммутатор 17, четыре блока 18 - 21 элементов повторителей.

Блок 3 управления содержит дешифратор 22, регистр 23, блок 24 постоянной памяти, триггер 25, элемент ИЛИ-НЕ 26 и 27, элемент 28, элементы ИЛИ-НЕ 29, 30 и 31, элементы И-НЕ 32 и 33, элементы И 34 - 38, элементы 39 - 42 задержки, мультивибратор 43, формирователи 44 и 45 одиночных импульсов, элементы НЕ 46, 47 и 48. Одна из реализаций формирователя импульсов и элементов задержки дана ниже.

Формирователи 44 и 45 импульсов в блоке 3 управления представляют собой последовательно соединенные дифференциальную цепочку и инвертор как пороговый элемент; элементы 39 42 задержки представляют собой последовательно соединенные элементы НЕ,

интегрирующую цепочку и еще один элемент НЕ.

Блоки 4-12 представляют собой любые статические оперативные запоминающие устройства с произвольной выборкой при их обычном включении. Коммутатор 17 реализован по схеме Один из N (N - число информацион ных входов).;

Блоки ключей представляют собой любые ключевые схемы на несколько разрядов. В данном устройстве это схемы 2И-НЕ с открытым коллектором, которые объединяются первыми входами и

служат в качестве строба разрешения. На вторые входы схем 2И-НЕ заведены информационные сигналы.

Счетчик представляет собой двоичный счетчик, работающий в зависимое-

ти от управляющих сигналов в режиме счета и в режиме параллельной записи. Блок усилителей представляет собой логические схемы (в .частности это 2И-НЕ), позволяющие нагружать их несколькими входами.

Устройство работает следуюпрш образом.

В режиме подготовки устройства, к работе счетчик 1 работает в счетном

режиме под действием управляющих сигналов, один из которых, тактирукяций сигнал, поступает из блока 3 управления, другой - с пульта переключателей, который подключается к входам выходам блока 2 усилителей, задает в каком режиме работать счетчику t (в режиме счет или в режиме параллельной записи).

Под действием управляющих сигналов счетчик 1 устанавливает значение 3 текущего адреса ячейки блоков 4-7 памяти -поступающего на третью группу входов этих блоков. Контрольная информация, которую необходимо запи сать, поступает на первые входы бло ков 4-7 памяти из блока усилителей; под действием сигналов управле ния, поступающих из блока 3 управле ния, в ячейках блоков 4-7 памяти записывается информация, причем ячейка блока памяти, где записана логическая 1, соответствует входному набору, отслеживающему информа цию, поступающую на третьи адресные входы блоков 4-7 памяти через счетчик 1 в режиме Формирования кон рольных кодов. Той ячейке, где записан предварительно логический О соответствует входной адресный набо блоков 4 - 7 памяти, который будет агнорироваться, т.е. соответствует отсутствию совпадения. Так как каждьш из блоков 4-7 блоков памяти представляет собой оперативное запо минающее устройство (ОЗУ) с произвольной выборкой, имеющее определен ную информационную емкость, опредегляемую числом адресных входов, то для отслеживания требуемых условий совпадения требуется, чтобы число адресных входов блоков памяти равня лось числу каналов в проверяемом объекте. На выходах блоков 18-21 элемен тов повторителей будет значение, соответствующее требуемому коду магистрали и коду в контрольных точка объекта диагностирования. Пусть требуется сравнить битовое слово с другт, поступающим через первый вход устройства на регистрсчетчик 1 (ожидаемый кодовый набор заранее запрограммированным). Имеет ОЗУ с произвольной выборкой 4, 1 К слов X 1 бит. Так как можно записат данные из блока усилителей в любую ячейку (битный адрес), то нужный процесс сравнения можно подготовить и выполнить с помощью таких ОЗУ 4. Запишем логическую 1 в k -е слово причем адрес k будет равен битовой комбинации, которую предстоит сравнить с заранее заданной.Адресk -го слова равен ожидаемому кодовому наб ру и битового слова. Запишем логический О во все другие ячейки ОЗУ 4. 584 Теперь ОЗУ 4 готово сравнить любые действительные данные, поступающие . из счетчика 1 от объекта диагностирования, причем кодовое слово этих данных соединяется с третьим адрес- . н.ым входом ОЗУ 4, которое под действием управляющих сигналов, поступающих с первого выхода блока 3 управления, формирует контрольный сигнал первого уровня, который с выхода блока 18 элементов повторителей поступает на второй выход устройства через первый ключ 14 и на первую группу входов регистра 16 адреса. Блоки 5, 6 и 7 работают аналогично блоку 4 памяти и формируют три контрольных сигнала первого уровня. Контрольные сигналы первого уровня отражают следующие функции работы устройства: сравнение с заданным кодом, несравнение с заданным кодом, больше значения заданного кода, меньше значения заданного кода, маскирование значений, поступающих с объекта диагностирования кодов. Эти контрольные сигналы первого уровня поступают на первую группу входов регистра 16 адреса, на вторую группу входов которого поступают два сигнала обратной связи с блоков 8 и 9 памяти обратной связи. В режиме формирования контрольных кодов под действием сигналов управления, поступающих из блока 3 .управления на первый вход регистра 16 адреса, происходит их запоминание в этом регистре, с выхода которого информация поступает на третьи адресные входы блоков 10, 11 и 12 памяти последовательностей и блоков 8 и 9 памяти обратной связи, образуя адрес текущей ячейки блоков памяти 8 - 12. С выходов блоков 10-12 памяти формирования последовательностей сигналы, если они предварительно записаны в данных ячейках, поступают на входы третьего блока 15 ключей и под действием управляющего сигнала с блока 3 управления выдаются на второй выход устройства как контрольные сигналы второго уровня. Начальная установка регистра 16 адреса осуществляется с помощью первого блока 13 ключей, управляемых сигналом, поступающим на второй вход из блока 3 управления. После предварительной установки ключи 13 отключаются и их выходы оказываются разорванными с входами регистра 16

адреса. Память фop fиpoвaния контрольных сигналов второго уровня блоков 10 - 12 и память обратной связи блок.ов 8 и 9 предварительно прописываются значениями требуемьпс сигналов; информация пост5шает с блока 2 усилителей на первые входы этих блоков, адрес устанавливается из блока 2 усилителей через блок ключей,которые в режиме предварительной установки замкнуты; на выходе регистра 16 адреса и под действием управляющих сигналов, поступающих с пятого выхода блока 3 управления, осуществляется запись этой информации. Коммутатор 17, под действием управляющих сигналов из блока 3 управления,поступающих на его второй вход, осуществляет мультиплексирование одного из шести направлений информации в блок усилителей для осуществления операции чтения регистра 16 адреса, блоков памяти последовательностей и памяти обратной связи.

Под действием глубокой обратной связи память формирования последовательностей блоков 10, 11 и 12 реализует всевозможные функции с длиной последовательности, равной четырем и числом функций, равном 64. Всего же предполагаемое устройство (с учетом реализации функций на первом уровне) может задавать не менее 2 всевозможных условий формирования контрольных сигналов.

Блок управления (фиг.2) работает следующим образом.

Информация (например от ЭВМ НЦ 80-01Д) поступает через блок 2 усилителей на первый вход блока 3 управления, а затем на информационные входы постоянного запоминаницего устройства (ПЗУ) 24 и регистра 23 состояния.

На второй вход блока 3 управления через блок 2 усилителей поступают управляющие сигналы режима работы (РР), сигнал - признак обмена информацией (ОБМ),сигналы информации цикла записи или чтения (ДЗП), (ДЧТ) и сигнал блоки вки работы постоянного запоминающего.устройства (последний может отсутствовать) (БЛ), Блок управления работает в двух основных режимах, определяемых значе,нием сигнала PP. Если этот сигнал соответствует логическому О, то

блок 3 управления работает в режиме чтения/запись, что соответствует начальной установке устройства, при

5 этом во внутренние регистры я память устройства-зашивка осуществляется следующим образом.

На первом и- втором выходе ПЗУ 24 при снятии сигнала БЛ появляется ин0 формация,соответствующая адресу который поступает, из блока усилителей на его первый информационный вхоД. ПЗУ запрограммировано так, что при обращениях по одному адресу на обоих

5 выходах будет сигнал логической 1, при обращении по второму адресу уровень логической 1 будет только на втором выходе, при обращении по любому другому адресу на выходах ПЗУ . 20 сигнал логической i будет отсутствовать. Такая зашивка позволяет обращаться к внутренним регистрам и памяти через два адреса. Дешифратор 22 вырабатывает стробы записи, которые поступают на счетчик 1, элемент ИЛИ-НЕ 30 и формирователь 45, на регистр 16 адреса через элемент RTUi-HE 29, формирователь 44, элемент И-НЕ 32, элемент 39 задержки, на

30 блоки памяти 4 - 7 через элемент 41 задержки и элемент И 37, через элемент НЕ 48 и элемент И 34, на блоки 8-12 памяти последовательностей и памяти обратной связи через элемент.

5 42 задержки, элемент И 38, через

элемент И 35. С элемента НЕ 47 сигналы управления поступают на блок 2 усилителей.

Сигналы с первого выхода регистра

0 23 состояния поступают на второй управляюЕ ий вход мультиплексора 17, а с выхода элемента И 46 сигнал подается на второй вход блока -13 ключей, на первые входы блоков 14 и 15

5 ключей. При наличии на линии сигнала РР, соответствующего логической 1, блок 3 управления переходит в режим формирования контрольных сигналов (одновременно блокируется обмен с

O внешним устройством для начальной установки), включает в работу ждущий мультивибратор 43, который формирует стробы записи в регистр 16 адреса :через элемент И-НЕ 32 и элементы

5 39 и 40 задержки, стробы чтения из I памяти последовательностей и памяти обратной связи через элемент И 38 и строб чтения блоков, 4 - 7 памяти че7 1 рез элемент И 37. Управляющий сигнал с выхода элемента И 46 открывает ключи 14, 15 и закрывает ключ 13. Сигнал с выхода элемента 43 через элемент И-НЕ 33 поступает на элемент И 36, с выхода которой сигнал с частотой, выработанной ждущим мультивибратором, поступает на тактирующий вход счетчика 1, который работает в

Е

m m m

704588

этом случае в режиме параллельной записи. Элементы И 34 и 35 поддерживают сигнал высокого уровня на выходах, с которых они поступают на управляющие входы блоков 4 - 7 памяти и блоков 8-12 памяти последовательностей и памяти обратной связи, что соответствует режиму чтения этих блоков.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3976864, кл | |||

| Мерная кружка для жидких тел | 1914 |

|

SU502A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| National Computer Conference, 19.79 | |||

| The BVS Link - Amicroprogramraed development tool for the CMOS/SOS processes system AVNER BEN-DOR PAVS BAKER, JON SELDEN. | |||

Авторы

Даты

1985-07-30—Публикация

1983-07-01—Подача