входы счетчиков адреса соединены с третьими выходами блока управления, четвертый выход блока сопряжения подключен к входам регистров конечного адреса, выходы которых через блок сравнения подключены к второму входу блока управления, выходы счетчиков адреса подключены к другим входам блока сравнения и к входам соответствующих дешифраторов, выходы которых подключены к входам блока стробирования, выходы блока элементов I-I подключепы к последовательно соединенным дополнительным блокам элементов И, прп этом другие выходы остальных блоков памяти подключены к вторым входам соответствующих дополнительных блоков элементов И, третьи входы которых соединены с выходом блока стробпрованпя.

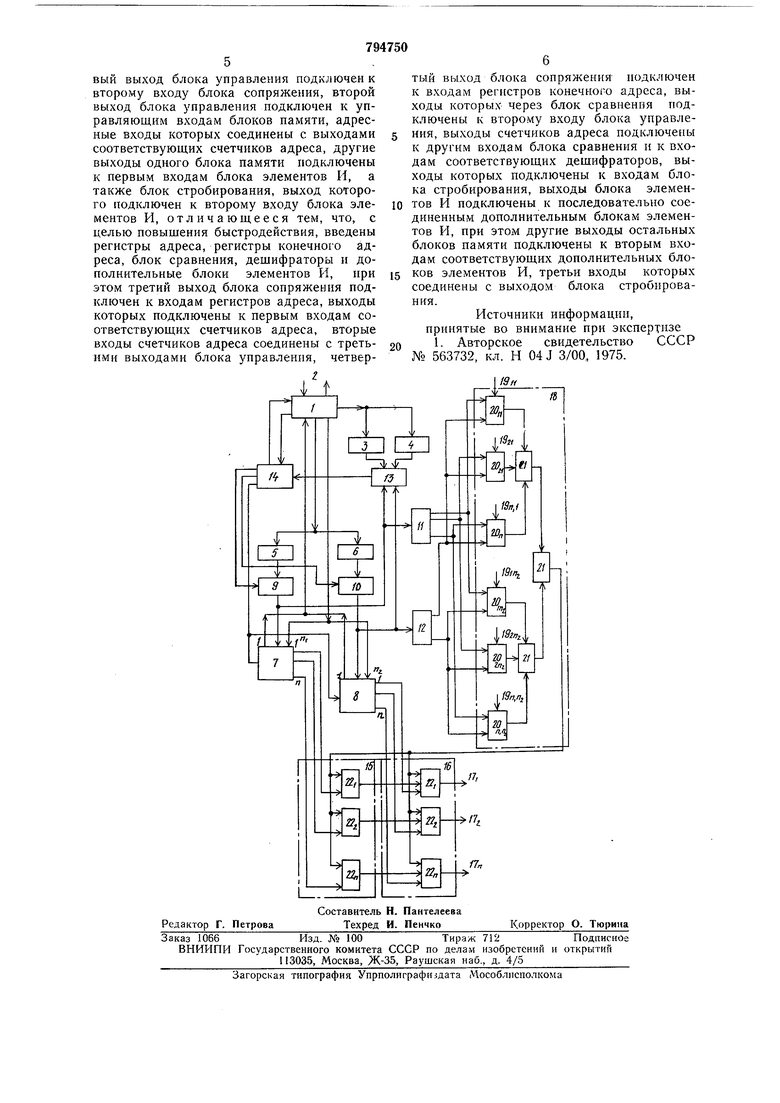

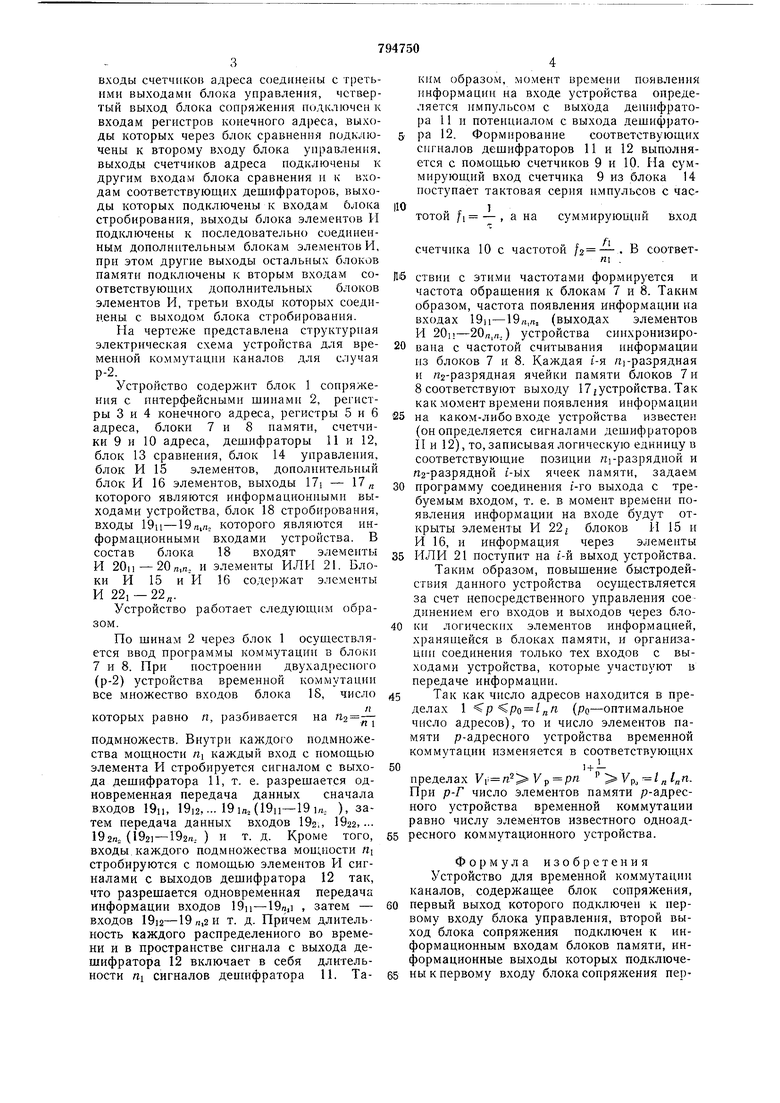

На чертеже представлена структурная электрическая схема устройства для времеппой коммутации каналов для случая р-2.

Устройство содержит блок 1 соиряжения с интерфейсными шинами 2, регистры 3 и 4 конечного адреса, регистры 5 и 6 адреса, блоки 7 и 8 иамяти, счетчики 9 и 10 адреса, дешифраторы 11 и 12, блок 13 сравнения, блок 14 управлеиия, блок И 15 элементов, дополнительный блок И 16 элементов, выходы 17i - 17„ которого являются информационными выходами устройства, блок 18 стробирования, входы 19ii-19п я, которого являются информационными входами устройства. В состав блока 18 входят элементы И 20ii -20„,„, и элементы ИЛИ 21. Блоки И 15 и И 16 соде1)жат элементы И 22, - 22„.

Устройство работает следующим образом.

По шинам 2 через блок 1 осуществляется ввод программы коммутации в блок 7 и 8. При построении двухадресного (р-2) устройства временной коммутации все множество входов блока 18, число

которых равно п, разбивается

на П2 подмножеств. Внутри каждого подмножества мощности rti каждый вход с помощью элемента И стробируется сигналом с выхода дешифратора 11, т. е. разрешается одновременная передача данных сначала входов 19ii, 19i2,... 19i/j,,(19ii-19in, ), затем передача данных входов Ша., 1922, -. 19 2п. (1921-192/1, ) и т. д. Кроме того, входы каждого подмножества мощности ni стробируются с помощью элементов И сигналами с выходов дешифратора 12 так, что разрешается одновременная передача информации входов Шц-19n,i , затем - входов 19)2-19«,2Ц т. д. Причем длительность каждого распределенного во времени и в пространстве сигнала с выхода дешифратора 12 включает в себя длительности «1 сигналов дешифратора 11. ТаКИМ образом, момент времени появления информации на входе устройства определяется импульсом с выхода дешифратора 11 и потенциалом с выхода дешифратора 12. Формирование соответствующих сигналов дешифраторов 11 и 12 выполняется с помощью счетчиков 9 ц 10. На суммирующий вход счетчика 9 из блока 14 поступает тактовая серия импульсов с час110„, 1

тотои /1 - , а на суммирующий вход

счетчика 10 с частотой . В соответт .

Пб ствии с этими частотами формируется и частота обращения к блокам 7 н 8. Таким образом, частота появления информации на входах 19)1-19я,лг (выходах элементов И 20 1-20я,л,) устройства синхронизирована с частотой считывания информации из блоков 7 и 8. Каждая i-я Л)-разрядная и И2-разрядная ячейки памяти блоков 7 и 8 соответствуют выходу Пгустройства. Так как момент времени появления информации на каком-либо входе устройства известен (он определяется сигналами дещифраторов II и 12), то, записывая логическую единицу в соответствующие позиции Л -разрядной и П2-разрядной t-bix ячеек памяти, задаем программу соединения i-ro выхода с требуемым входом, т. е. в момент времени появления информации на входе будут открыты элементы И 22 блоков И 15 и И 16, и информация через элементы

35 ИЛИ 21 поступит на i-й выход устройства. Таким образом, повыщение быстродействия данного устройства осуществляется за счет непосредственного управления соединением его входов и выходов через блоки логических элементов информацией, храняи1ейся в блоках памяти, и организации соединения только тех входов с выходами устройства, которые участвуют в передаче информации.

Так как число адресов находится в пределах 1 р я« (ро-оптимальное число адресов), то и число элементов памяти р-адресного устройства временной коммутации изменяется в соответствующих

+ Г пределах Ур /„/„п.

При р-Г число элементов памяти р-адресного устройства временной коммутации равно числу элементов известного одноад5 ресного коммутационного устройства.

Формула изобретения Устройство для временной коммутации каналов, содержащее блок сопряжения, первый выход которого подключен к первому входу блока управления, второй выход блока сопряжения подключен к информационным входам блоков памяти, информационные выходы которых подключены к первому входу блока сопряжения пер

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1988 |

|

SU1513438A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1986 |

|

SU1396147A1 |

| Цифровое коммутационное устройство | 1985 |

|

SU1378088A1 |

| Устройство для обмена информацией | 1974 |

|

SU732848A1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Микропрограммное устройство управления | 1988 |

|

SU1564621A1 |

| Устройство для сопряжения ЭВМ в вычислительной системе с децентрализованным арбитром магистрали | 1984 |

|

SU1291997A1 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

| Устройство ввода информации в ЭВМ | 1988 |

|

SU1562896A2 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1508227A1 |

Авторы

Даты

1981-01-07—Публикация

1979-01-05—Подача