Изобретение относится к вычислительной технике и может быть использовано при создании широкого класса средств: устройств ввода-вывода, аппаратуры сопряжения, измерительной и бытовой техники.

Цель изобретения - повышение быстройдействия устройства при мно- гофункционал. ном использовании разрядов блока памяти микрокоманд и синхронизации признаков условий.

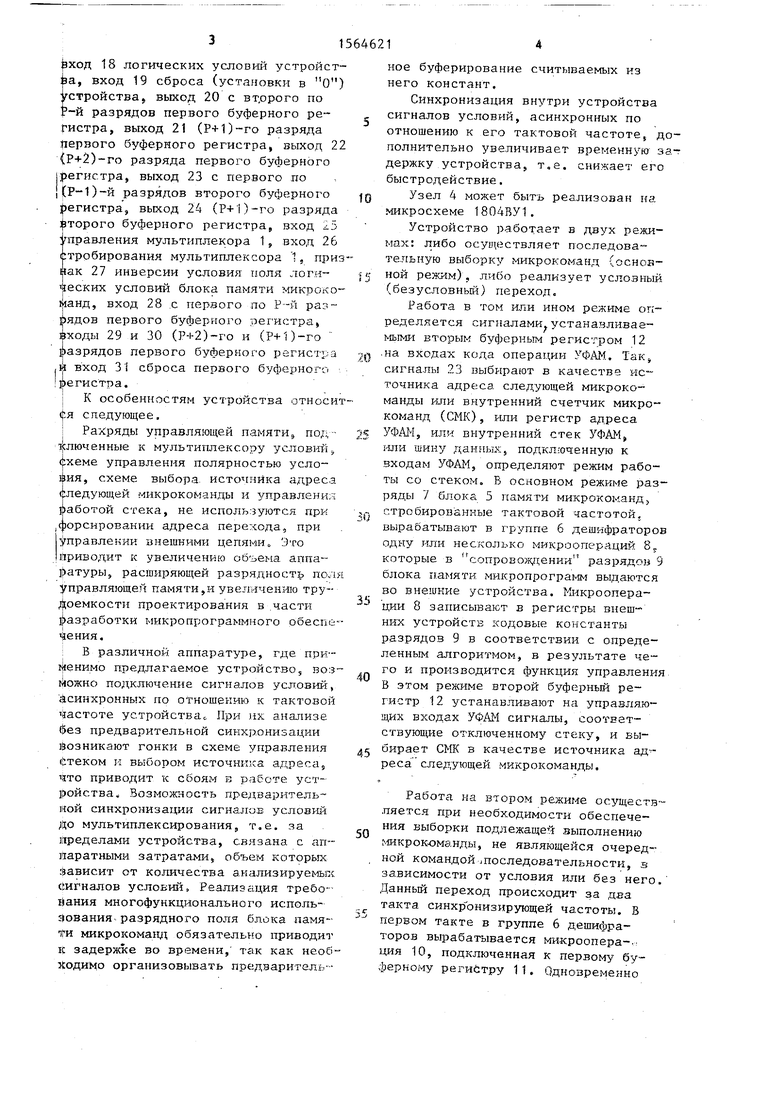

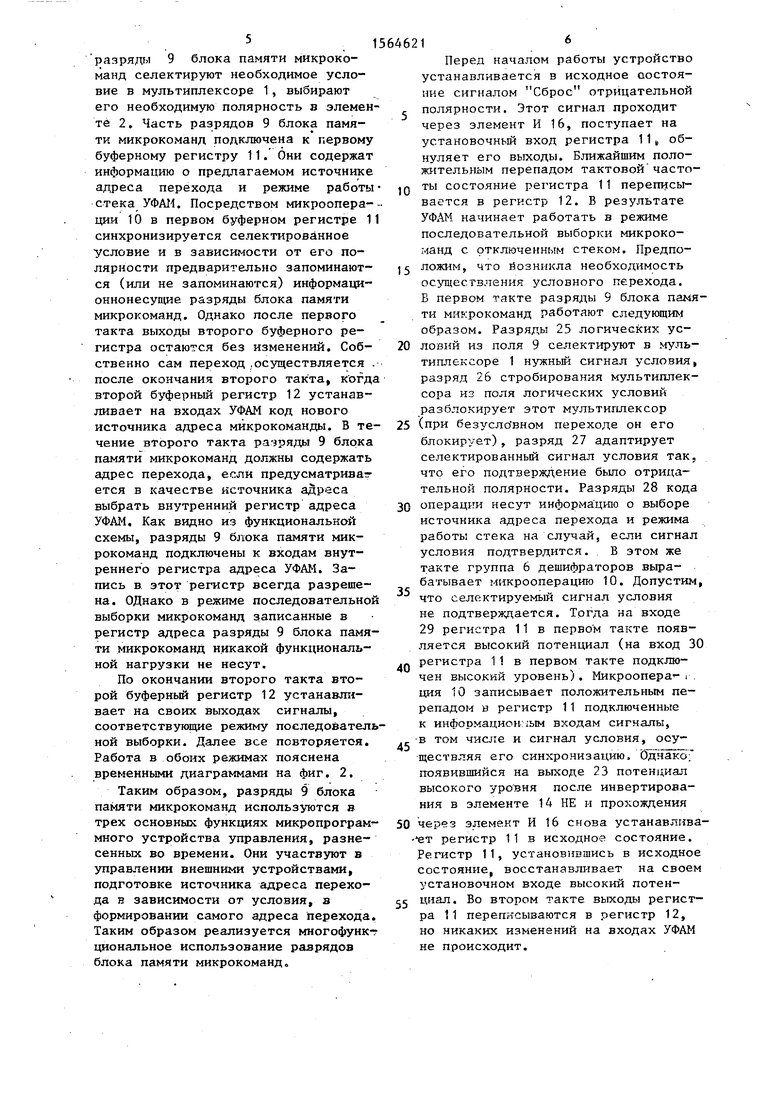

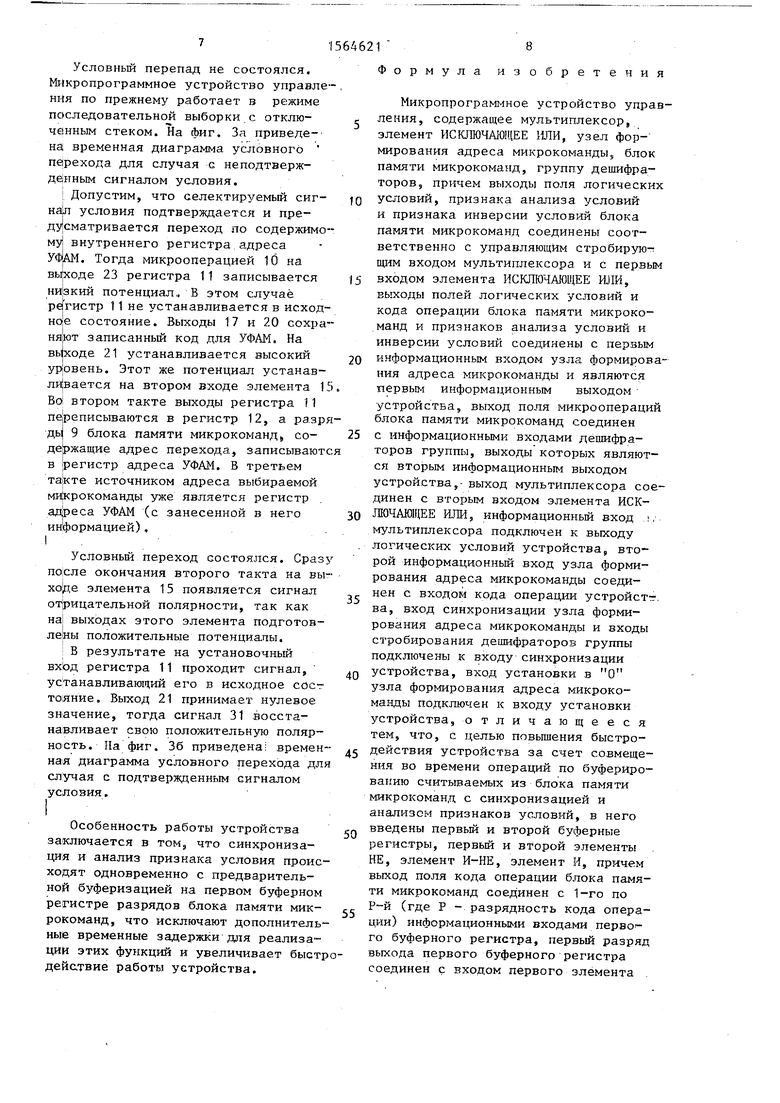

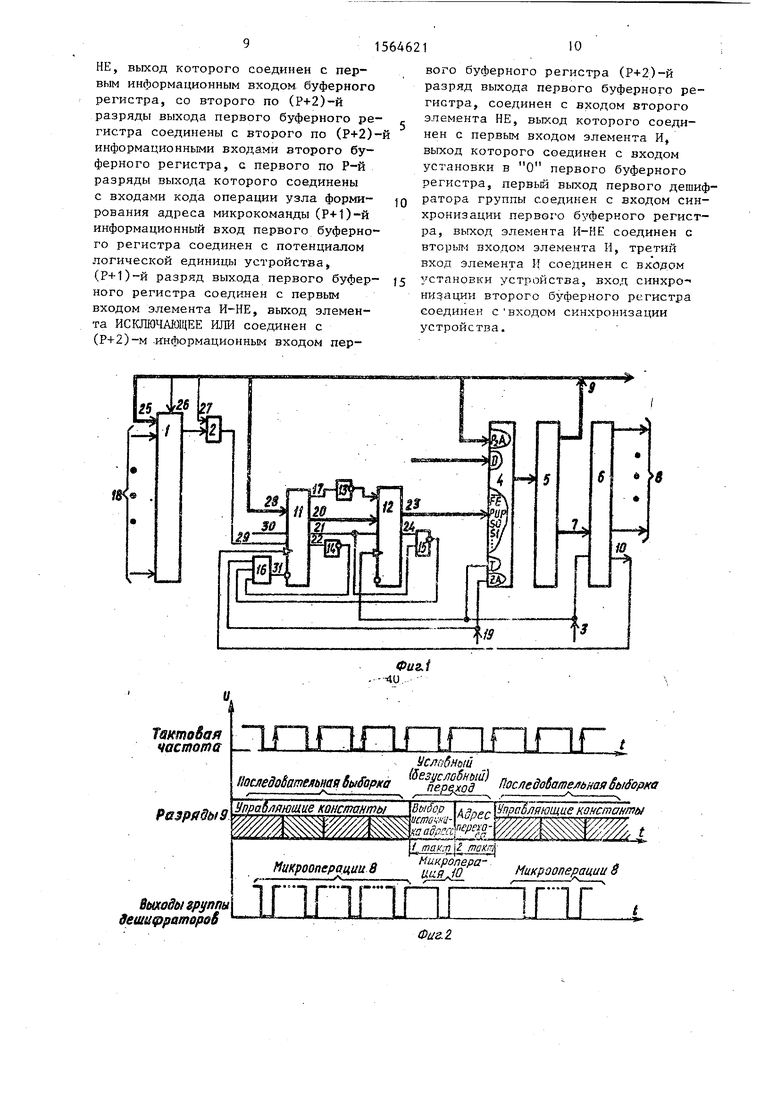

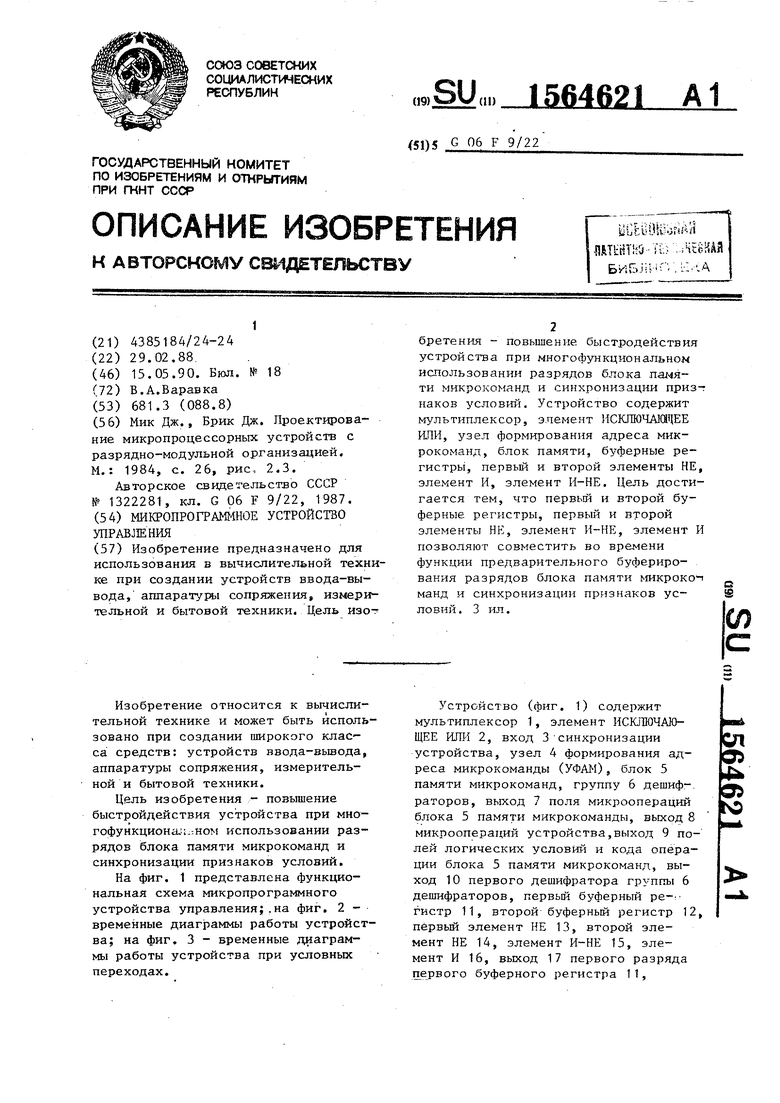

На фиг. 1 представлена функциональная схема микропрограммного устройства управления;.на фиг. 2 - временные диаграммы работы устройства; на фиг. 3 - временные диаграммы работы устройства при условных переходах.

Устройство (фиг. 1) содержит мультиплексор 1, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, вход 3 синхронизации устройства, узел 4 формирования адреса микрокоманды (УФАМ), блок 5 памяти микрокоманд, группу 6 дешифраторов, выход 7 поля микроопераций блока 5 памяти микрокоманды, выход 8 микроопераций устройства,выход 9 полей логических условий и кода операции блока 5 памяти микрокоманд, выход 10 первого дешифратора группы 6 дешифраторов, первый буферный регистр 11, второй буферный регистр 12, первый элемент НЕ 13, второй элемент НЕ 14, элемент И-НЕ 15, элемент И 16, выход 17 первого разряда первого буферного регистра 11,

:зход 18 логических условий устройства, вход 19 сброса (установки в О) устройства, выход 20 с вт.орого по -й разрядов первого буферного регистра, выход 21 (Р-Н)-го разряда Первого буферного регистра, выход 22 (Р+2)-го разряда первого буферного (регистра, выход 23 с первого по (Р-1)-й разрядов второго буферного йегистра, выход 24 (Р+)-го разряда второго буферного регистра, вход ±5 управления мультиплекора 1, вход 26 стробирования мультиплексора 1, признак 27 инверсии условия поля логических условий блока памяти микооко- :анд, вход 28 с первого по -п раз- Ядов первого буферного регистра,

:ХОДЫ 29 И 30 (Р + 2)-ГО И (Р+1)-ГО

азрядов первого буферного регистр а

вход 31 сброса первого буферного егистра.

К особенностям устройства относи фя спедующее,

Рахряды управляющей памяти под - т)слюченные к мультиплексору условий, Ьсеме управления полярностью уело- зшя, схеме выбора источника адреса следующей микрокоманды и управлени.: работой стека, не используются при ,оорсировании адреса перехода, при управлении внешними цепями Это приводит к увеличению объема аппаратуры, расширяющей разрядность лол управляющей памяти,и увеличению тру-- $оемкости проектирования в части разработки микропрограммного обеспечения.

В различной аппаратуре, где применимо предлагаемое устройство, возможно подключение сигналов условий, асинхронных по отношению к тактовой частоте устройства При их анализе фез предварительной синхронизации возникают гонки в схеме управления стеком и выбором источника адреса, что приводит к сбоям п работе устройства Возможность предварительной синхронизации сигналов условий до мультиплексирования, т.е. за мределами устройства, связана с аппаратными затратами, объем которых зависит от количества анализируемых сигналов условий, Реализация требования многофункционального использования разрядного поля блока памяти микрокоманд обязательно приводит к задержке во времени, так как необходимо организовывать лредваритель-

0

с

5

0

5

0

ное буферирование считываемых из него констант.

Синхронизация внутри устройства сигналов условий, асинхронных по отношению к его тактовой частоте, дополнительно увеличивает временную задержку устройства, т.е. снижает его быстродействие.

Узел 4 может быть реализован на микросхеме 1804ВУ1.

Устройство работает в двух режимах: либо осуществляет последовательную выборку микрокоманд (основной режим), либо реализует условный (безусловный) переход.

Работа в том или ином режиме определяется сигналами.устанавливаемыми вторым буферным регистром 12 на входах кода операции УФАМ. Так сигналы 23 выбирают в качестве источника адреса следующей микрокоманды или внутренний счетчик микрокоманд (СМК), или регистр адреса УФАМ, или внутренний стек УФАМ, или шину данных, подключенную к входам УФАМ, определяют режим работы со стеком. В основном режиме разряды 7 блока 5 памяти микрокоманд, стробированные тактовой частотой, вырабатывают в группе 6 дешифраторов одну или несколько микроопераций 8,; которые в сопровождении разрядов 9 блока памяти микропрограмм выдаются во внешние устройства. Микрооперации 8 записывают в регистры внешних устройств кодовые константы разрядов 9 в соответствии с определенным алгоритмом, в результате чего и производится функция управления В этом режиме второй буферный регистр 12 устанавливают на управляющих входах УФАМ сигналы, соответствующие отключенному стеку, и выбирает СМК в качестве источника адреса следующей микрокоманды.

Работа па втором режиме осуществляется при необходимости обеспечения выборки подлежащей выполнению микрокоманды, не являющейся очередной командой последовательности, в зависимости от условия или без него. Данный переход происходит за два такта синхронизирующей частоты. В первом такте в группе 6 дешифраторов вырабатывается микроопера-, ция 10, подключенная к первому буферному регистру 11. Одновременно

разряды 9 блока памяти микрокоманд селектируют необходимое условие в мультиплексоре 1, выбирают его необходимую полярность в элементе 2. Часть разрядов 9 блока памяти микрокоманд подключена к первому буферному регистру 11. Они содержат информацию о предлагаемом источнике адреса перехода и режиме работы стека УФАМ. Посредством микрооперации 10 в первом буферном регистре 1 синхронизируется селектированное условие и в зависимости от его полярности предварительно запоминаются (или не запоминаются) информаци- оннонесущие разряды блока памяти микрокоманд. Однако после первого такта выходы второго буферного регистра остаются без изменений. Собственно сам переход .осуществляется . после окончания второго такта, когда второй буферный регистр 12 устанавливает на входах УФАМ код нового источника адреса микрокоманды. В течение второго такта рачряды 9 блока памяти микрокоманд должны содержать адрес перехода, если предусматривав ется в качестве источника адреса выбрать внутренний регистр адреса УФАМ. Как видно из функциональной схемы, разряды 9 блока памяти микрокоманд подключены к входам внутреннего регистра адреса УФАМ. Запись в этот регистр всегда разрешена. ОДнако в режиме последовательной выборки микрокоманд записанные в регистр адреса разряды 9 блока памяти микрокоманд никакой функциональной нагрузки не несут.

По окончании второго такта второй буферный регистр 12 устанавливает на своих выходах сигналы, соответствующие режиму последовательной выборки. Далее все повторяется. Работа в обоих режимах пояснена временными диаграммами на фиг. 2.

Таким образом, разряды 9 блока памяти микрокоманд используются в трех основных функциях микропрограммного устройства управления, разнесенных во времени. Они участвуют в управлении внешними устройствами, подготовке источника адреса перехода в зависимости от условия, в формировании самого адреса перехода. Таким образом реализуется многофункт циональное использование разрядов блока памяти микрокоманд

0

Перед началом работы устройство устанавливается в исходное состояние сигналом Сброс отрицательной полярности. Этот сигнал проходит через элемент И 16, поступает на установочный вход регистра 11 обнуляет его выходы. Ближайшим положительным перепадом тактовой частоты состояние регистра 11 переписывается в регистр 12. В результате УФАМ начинает работать в режиме последовательной выборки микрокоманд с отключенным стеком. Предпо- 5 ложим, что возникла необходимость осуществления условного перехода. Б первом такте разряды 9 блока памяти микрокоманд работают следующим образом. Разряды 25 логических ус- 0 ловий из поля 9 селектируют в мультиплексоре 1 нужный сигнал условия, разряд 26 стробирования мультиплексора из поля логических условий разблокирует этот мультиплексор 5 (при безусловном переходе он его блокирует), разряд 27 адаптирует селектированный сигнал условия так, что его подтверждение было отрицательной полярности. Разряды 28 кода 0 операции несут информацию о выборе источника адреса перехода и режима работы стека на случай, если сигнал условия подтвердится. В этом же такте группа 6 дешифраторов вырабатывает микрооперацию 10. Допустим, что селектируемый сигнал условия не подтверждается. Тогда на входе 29 регистра 11 в первом такте появляется высокий потенциал (на вход 30 регистра 11 в первом такте подключен высокий уровень) . Микроопера - i ция 10 записывает положительным перепадом в регистр 11 подключенные к информацией 1ым входам сигналы, в том числе и сигнал условия, осуществляя его синхронизацию, Однако. появившийся на выходе 23 потенциал высокого уро вня после инвертирования в элементе 14 НЕ и прохождения элемент И 16 снова устанавливает регистр 11 в исходное состояние. Регистр 11, установившись в исходное состояние, восстанавливает на своем установочном входе высокий потенциал. Во втором такте выходы регистра 11 переписываются в регистр 12, но никаких изменений на входах УФАМ не происходит.

5

0

5

0

5

Условный перепад не состоялся. Микропрограммное устройство управления по прежнему работает в режиме последовательной выборки с отклю- чанным стеком. На фиг. За приведена временная диаграмма условного перехода для случая с неподтвержденным сигналом условия.

Допустим, что селектируемый сиг- на|л условия подтверждается и пре- ду сматривается переход по содержимому внутреннего регистра адреса УФАМ. Тогда микрооперацией 10 на вцходе 23 регистра 11 записывается низкий потенциал., В этом случае регистр 11 не устанавливается в исходной состояние. Выходы 17 и 20 сохра-- ня,ют записанный код для УФАМ. На вь|ходе 21 устанавливается высокий уровень. Этот же потенциал устанавливается на втором входе элемента 15 Во втором такте выходы регистра И переписываются в регистр 12, а разряды; 9 блока памяти микрокоманд, со- держащие адрес перехода, записываютс в регистр адреса УФАМ. В третьем такте источником адреса выбираемой микрокоманды уже является регистр адреса УФАМ (с занесенной в него информацией). I

Условный переход состоялся. Сразу после окончания второго такта на вы- элемента 15 появляется сигнал отрицательной полярности, так как H3i выходах этого элемента подготовлены положительные потенциапы.

В результате на установочный вход регистра 11 проходит сигнал, устанавливающий его в исходное состояние. Выход 21 принимает нулевое значение, тогда сигнал 31 восстанавливает свою положительную полярность. На фиг. 36 приведена времен- ная диаграмма условного перехода для случая с подтвержденным сигналом условия.

Особенность работы устройства заключается в том, что синхронизация и анализ признака условия происходят одновременно с предварительной буферизацией на первом буферном регистре разрядов блока памяти мик- рокоманд, что исключают дополнительные временные задержки для реализации этих функций и увеличивает быстрдействие работы устройства.

0 5 0

д 5

0 е

5

Формула изобретения

Микропрограммное устройство управления, содержащее мультиплексор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, узел формирования адреса микрокоманды, блок памяти микрокоманд, группу дешифраторов, причем выходы поля логических условий, признака анализа условий и признака инверсии условий блока памяти микрокоманд соединены соответственно с управляющим стробирую- щим входом мультиплексора и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы полей логических условий и кода операции блока памяти микрокоманд и признаков анализа условий и инверсии условий соединены с первым информационным входом узла формирования адреса микрокоманды и являются первым информационным выходом устройства, выход поля микроопераций блока памяти микрокоманд соединен с информационными входами дешифраторов группы, выходы которых являются вторым информационным выходом устройства,- выход мультиплексора соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, информационный вход , мультиплексора подключен к выходу логических условий устройства, второй информационный вход узла формирования адреса микрокоманды соединен с входом кода операции устройст-г ва, вход синхронизации узла формирования адреса микрокоманды и входы стробирования дешифраторов группы подключены к входу синхронизации устройства, вход установки в О узла формирования адреса микрокоманды подключен к входу установки устройства, отличающееся тем, что, с целью повышения быстродействия устройства за счет совмещения во времени операций по буфериро- ванию считываемых из блока памяти микрокоманд с синхронизацией и анализом признаков условий, в него введены первый и второй буферные регистры, первый и второй элементы НЕ, элемент И-НЕ, элемент И, причем выход поля кода операции блока памяти микрокоманд соединен с 1-го по (где Р - разрядность кода операции) информационными входами первого буферного регистра, первый разряд выхода первого буферного регистра соединен с входом первого элемента

НЕ, выход которого соединен с первым информационным входом буферного регистра, со второго по (Р+2)-й разряды выхода первого буферного ре- гистра соединены с второго по (Р+2)информационными входами второго буферного регистра, с первого по Р-й разряды выхода которого соединены с входами кода операции узла форми- рования адреса микрокоманды (Р+1)-й информационный вход первого буферного регистра соединен с потенциалом логической единицы устройства, (Р+1)-й разряд выхода первого буфер- ного регистра соединен с первым входом элемента И-НЕ, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с (Р+2)-м информационным входом первого буферного регистра (Р+2)-й разряд выхода первого буферного регистра, соединен с входом второго элемента НЕ, выход которого соединен с первым входом элемента И выход которого соединен с входом установки в О первого буферного регистра, первьй выход первого дешифратора группы соединен с входом синхронизации первого буферного регистра, выход элемента И-НЕ соединен с вторым входом элемента И, третий вход элемента И соединен с входом установки устройства, вход синхро- низ.ации второго буферного регистра соединен с входом синхронизации устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1183964A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1636845A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

Изобретение предназначено для использования в вычислительной технике при создании устройств ввода-вывода, аппаратуры сопряжения, измерительной и бытовой техники. Цель изобретения - повышение быстродействия устройства при многофункциональном использовании разрядов блока памяти микрокоманд и синхронизации признаков условий. Устройство содержит мультиплексор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, узел формирования адреса микрокоманд, блок памяти, буферные регистры, первый и второй элементы НЕ, элемент И, элемент И-НЕ. Цель достигается тем, что первый и второй буферные регистры, первый и второй элементы НЕ, элемент И-НЕ, элемент И позволяют совместить во времени функции предварительного буферирования разрядов блока памяти микрокоманд и синхронизации признаков условий. 3 ил.

kri f t

±26 W

rf-lh

т

И

1L W

-

Ё

JЈ-

W

Тактовая частота -

ЛОЕДПЕИ

/// Ч 1, J .

Разряды 9

ijSM..

I Wltbff И « 0

1 Г 11-I - 1

Выходы gpynnul И U U L дешифраторов и- I-J-- « -«-

Микрооперации 8№я°ЮРа Микрооперации S

Фиг 2.

9

и

2S

ШКШ

#,

$-I

Фи&.1

-40

ijSM..

Фиг 2.

| Мик Дж., Брик Дж | |||

| Проектирование микропроцессорных устройств с разрядно-модульной организацией | |||

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1322281A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-15—Публикация

1988-02-29—Подача