Предлагаемое изобретение относится к области вычислительной техники и предназначено для использования в системах контроля и диагностики цифровых вычислительных устройств.

Известно устройство тестового контроля (см. А.С. №1425682, М. кл. G06F 11/26 БИ №35, 1988 г.), содержащее блок сопряжения, блок управления, n входных регистров, n регистров маски входов/выходов, n регистров маски входов, n блоков памяти, n коммутаторов первой группы, n блоков сравнения, n регистров результата, n коммутаторов второй группы, n выходных коммутаторов, n триггеров сбоя, элемент ИЛИ.

Недостатком данного устройства является отсутствие возможности оперативного переключения выводов контроля устройства с передачи тестовой информации на прием ответной реакции, что затрудняет проверку узлов с двунаправленными шинами.

Из известных технических решений наиболее близким по технической сущности к заявляемому объекту является устройство тестового контроля (см. АС №1691842, М. кл. G06F 11/26, БИ №42, 1991 г.), содержащее блок сопряжения, блок управления, n входных регистров, n регистров маски входов/выходов, n регистров маски входов, n блоков памяти, первую группу n коммутаторов с тремя состояниями на выходах, n блоков сравнения, n регистров результата, вторую группу n коммутаторов, n выходных коммутаторов, n триггеров сбоя, элемент ИЛИ, n управляющих регистров, n групп элементов ИЛИ, n групп элементов И, причем группа информационных выходов i-го (где i=1, …, n) блока памяти соединена с первой группой информационных входов i-го блока сравнения и группой информационных входов i-го коммутатора первой группы, группа выходов которого соединена с i-й группой выходов устройства для подключения к проверяемому узлу и группой информационных входов i-го коммутатора второй группы, группа выходов которого соединена со второй группой информационных входов i-го блока сравнения и группой информационных входов i-го регистра результата, группа адресных входов i-го блока памяти соединена с группой адресных выходов с тремя состояниями блока сопряжения и группой адресных выходов с тремя состояниями блока управления, выход записи строки теста блока сопряжения соединен со входом записи i-го блока памяти, группа информационных выходов i-го входного регистра соединена с группой информационных входов i-го блока памяти, i-го регистра маски входов и i-го регистра маски входов/выходов, группа выходов которого соединена с группой управляющих входов i-го коммутатора второй группы, группа выходов i-го регистра результата соединена с группой информационных входов i-го выходного коммутатора, управляющий вход которого соединен с i-м выходом группы выходов выдачи результата блока сопряжения, вход записи i-го регистра маски входов соединен с выходом записи маски входов блока сопряжения, вход записи i-го регистра маски входов/выходов соединен с выходом записи маски входов/выходов блока сопряжения, вход записи i-го входного регистра соединен с i-м выходом группы стробирующих выходов блока сопряжения, вход установки нуля i-го входного регистра соединен с выходом установки в ноль блока сопряжения, инверсный выход i-го блока сравнения соединен с информационным входом i-го триггера сбоя, прямой выход которого соединен с i-м входом группы входов обнаружения сбоев блока управления, вход установки нуля i-го триггера сбоя соединен с выходом элемента ИЛИ, тактирующий вход i-го триггера сбоя и вход записи i-го регистра результата соединены с выходом стробирования блока управления, выход установки начального адреса блока сопряжения соединен со входом записи адреса блока управления, выход чтения состояния блока сопряжения соединен со входом чтения состояния блока управления, выход чтения адреса блока сопряжения соединен со входом чтения адреса блока управления, выход чтения сбоев блока сопряжения соединен со входом чтения сбоев блока управления, выход сброса триггера сбоя блока сопряжения соединен с первым входом элемента ИЛИ, выход пуска блока сопряжения соединен со входом пуска блока управления, выход блокировки адреса блока управления соединен со входом блокировки адреса блока сопряжения, первый управляющий вход блока сопряжения подключен ко входу записи устройства, второй управляющий вход блока сопряжения подключен ко входу чтения устройства, группа входов адреса блока сопряжения соединена с входной шиной адреса устройства, входы установки в ноль i-го регистра маски входов, i-го регистра маски входов/выходов, i-го регистра результата, вход сброса блока управления, второй вход элемента ИЛИ соединены со входом сброса устройства, группа информационных входов i-го входного регистра, группа информационных входов/выходов блока управления, группа информационных входов блока сопряжения, группа информационных выходов i-го выходного коммутатора соединены с входной двунаправленной шиной данных устройства, группа информационных выходов i-го входного регистра соединена с группой информационных входов i-го управляющего регистра, j-й инверсный выход которого (где j=l, …, m, m - разрядность двунаправленной шины данных) соединен с первым входом j-го элемента ИЛИ i-й группы элементов ИЛИ, выход которого соединен с первым входом j-го элемента И i-й группы элементов И, группа выходов которой соединена с группой входов i-го коммутатора первой группы, j-й выход i-го регистра маски входов соединен со вторым входом j-го элемента И i-ой группы элементов И, второй вход j-го элемента ИЛИ i-ой группы элементов ИЛИ соединен с выходом управления направлением передачи информации блока управления, вход записи i-го управляющего регистра соединен с выходом записи маски двунаправленных выводов блока сопряжения, первый выход управления записью блока сопряжения соединен со входом записи первого интервала блока управления, второй выход управления записью блока сопряжения соединен со входом записи второго интервала блока управления, вход установки в ноль i-го управляющего регистра соединен со входом сброса устройства.

Основным недостатком данного устройства является отсутствие возможности независимого оперативного переключения различных групп двунаправленных выводов контроля устройства с передачи тестовой информации на прием ответной реакции с произвольной дискретностью переключения, что затрудняет проверку узлов с несколькими группами двунаправленных линий передачи/приема информации.

Целью изобретения является расширение функциональных возможностей за счет обеспечения возможности независимого оперативного переключения различных групп двунаправленных выводов контроля устройства с передачи тестовой информации на прием ответной реакции с произвольной дискретностью переключения.

Поставленная цель достигается тем, что в известное устройство, содержащее блок сопряжения, блок управления, n входных регистров, n регистров маски входов/выходов, n регистров маски входов, n блоков памяти, первую группу n коммутаторов с тремя состояниями на выходах, n блоков сравнения, n регистров результата, вторую группу n коммутаторов, n выходных коммутаторов, n триггеров сбоя, элемент ИЛИ, n управляющих регистров, причем группа адресных входов i-го (где i=1, 2, …, n) блока памяти соединена с группой адресных выходов с тремя состояниями блока сопряжения и группой двунаправленных адресных входов/выходов блока управления, выход записи строки теста блока сопряжения соединен со входом записи i-го блока памяти, группа информационных выходов i-го входного регистра соединена с группой информационных входов i-го блока памяти и i-го регистра маски входов/выходов, группа выходов которого соединена с группой управляющих входов i-го коммутатора второй группы, группа выходов i-го регистра результата соединена с группой информационных входов i-го выходного коммутатора, управляющий вход которого соединен с i-м выходом группы выходов выдачи результата блока сопряжения, вход записи i-го регистра маски входов/выходов соединен с выходом записи маски входов/выходов блока сопряжения, вход записи i-го входного регистра соединен с i-м выходом группы стробирующих выходов блока сопряжения, вход установки нуля i-го входного регистра соединен с выходом установки в ноль блока сопряжения, инверсный выход i-го блока сравнения соединен с информационным входом i-го триггера сбоя, прямой выход которого соединен с i-ым входом группы входов обнаружения сбоев блока управления, вход установки нуля i-го триггера сбоя соединен с выходом элемента ИЛИ, тактирующий вход i-го триггера сбоя и вход записи i-го регистра результата соединены с выходом стробирования результата блока управления, выход установки начального адреса блока сопряжения соединен со входом записи адреса блока управления, выход чтения состояния блока сопряжения соединен со входом чтения состояния блока управления, выход чтения адреса блока сопряжения соединен со входом чтения адреса блока управления, выход чтения сбоев блока сопряжения соединен со входом чтения сбоев блока управления, выход сброса триггера сбоя блока сопряжения соединен с первым входом элемента ИЛИ, выход пуска блока сопряжения соединен со входом пуска блока управления, выход блокировки адреса блока управления соединен со входом блокировки адреса блока сопряжения, первый управляющий вход блока сопряжения подключен ко входу записи устройства, второй управляющий вход блока сопряжения подключен ко входу чтения устройства, группа входов адреса блока сопряжения соединена с входной шиной адреса устройства, входы установки в ноль i-го регистра маски входов, i-го регистра маски входов/выходов, i-го регистра результата, i-го управляющего регистра, вход сброса блока управления, второй вход элемента ИЛИ соединены со входом сброса устройства, группа информационных входов i-го входного регистра, группа информационных входов/выходов блока управления, группа информационных входов блока сопряжения, группа информационных выходов i-го выходного коммутатора соединены с входной двунаправленной шиной данных устройства, группа выходов с тремя состояниями i-го коммутатора первой группы соединена с i-й группой двунаправленных выходов контроля устройства для подключения к проверяемому узлу и группой информационных входов i-го коммутатора второй группы, группа выходов которого соединена со первой группой информационных входов i-го блока сравнения и группой информационных входов i-го регистра результата, дополнительно введен регистр теста, причем группа информационных выходов i-го блока памяти соединена с группой информационных входов i-го регистра маски входов и с группой информационных входов i-го регистра теста, группа информационных выходов которого соединена со второй группой информационных входов i-го блока сравнения и с группой информационных входов i-го коммутатора первой группы, группа управляющих входов которого соединена с группой информационных выходов i-го управляющего регистра, группа информационных входов которого соединена с группой информационных выходов i-го регистра маски входов, вход разрешения записи i-го регистра маски входов соединен с выходом признака маски блока управления, вход разрешения записи i-го регистра теста и вход разрешения записи i-го управляющего регистра соединены с выходом признака теста блока управления, тактовый вход i-го регистра маски входов, тактовый вход i-го регистра теста и тактовый вход i-го управляющего регистра соединены с выходом строба записи блока управления, вход установки в ноль i-го регистра теста подключен ко входу сброса устройства, первый управляющий вход блока управления подключен к выходу установки в ноль блока сопряжения, выход записи строки теста которого подключен также ко входу записи строки теста блока управления, второй управляющий вход которого соединен с (n+1)-м выходом группы стробирующих выходов блока сопряжения.

Кроме того, блок сопряжения содержит дешифратор записи, дешифратор чтения, регистр адреса ячейки памяти, коммутатор с тремя состояниями на выходах, причем стробирующий вход дешифратора записи соединен с первым управляющим входом блока сопряжения, стробирующий вход дешифратора чтения соединен с вторым управляющим входом блока сопряжения, группы управляющих входов дешифратора записи и дешифратора чтения соединены с группой входов адреса блока сопряжения, группа информационных входов регистра адреса ячейки памяти соединена с группой информационных входов блока сопряжения, группа выходов регистра адреса ячейки памяти соединена с группой информационных входов коммутатора, управляющий вход которого соединен со входом блокировки адреса блока сопряжения, первая группа из n+1 выходов дешифратора записи соединена с группой стробирующих выходов блока сопряжения, (n+2)-й выход дешифратора записи соединен с выходом пуска блока сопряжения, (n+3)-й выход - с выходом установки начального адреса блока сопряжения, (n+4)-й выход - с выходом установки в ноль блока сопряжения, (n+5)-й выход - с выходом сброса триггера сбоя блока сопряжения, (n+6)-й выход - с выходом записи строки теста блока сопряжения, (n+7)-й выход - с выходом записи маски входов/выходов блока сопряжения, (n+8)-й выход - со входом параллельной записи регистра адреса ячейки памяти, группа выходов с тремя состояниями коммутатора соединена с группой адресных выходов с тремя состояниями блока сопряжения, первая группа из n выходов дешифратора чтения соединена с группой выходов выдачи результата блока сопряжения, (n+1)-й выход дешифратора чтения - с выходом чтения состояния блока сопряжения, (n+2)-й выход - с выходом чтения адреса блока сопряжения, (n+3)-й выход - с выходом чтения сбоев блока сопряжения.

Кроме того, блок управления содержит генератор тактовых импульсов, элемент И, два элемента НЕ, RS-триггер пуска, четыре коммутатора, элемент задержки, регистр адреса, счетчик адреса, элемент ИЛИ-НЕ, два элемента ИЛИ, одноразрядный буферный регистр, память признаков, причем выход генератора тактовых импульсов соединен с первым входом элемента И, прямой выход RS-триггера пуска соединен с первым информационным входом первого коммутатора, а также с управляющим входом второго коммутатора и вторым входом элемента И, выход которого соединен со входом параллельной записи регистра адреса и через первый элемент НЕ - с вычитающим входом счетчика адреса, выходом строба записи блока управления и со входом элемента задержки, выход которого соединен с выходом стробирования результата блока управления, группа выходов счетчика адреса соединена с группой информационных входов регистра адреса и группой входов элемента ИЛИ-НЕ, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ и вторым информационным входом первого коммутатора, выход первого элемента ИЛИ соединен со входом установки нуля RS-триггера пуска, группа выходов регистра адреса соединена с группами информационных входов второго и третьего коммутатора, группа выходов с тремя состояниями первого, третьего и четвертого коммутаторов соединены с группой информационных входов счетчика адреса и группой информационных входов/выходов блока управления, первый вход/выход из группы информационных входов/выходов блока управления подключен также к информационному входу одноразрядного буферного регистра, выход которого соединен с информационным входом памяти признаков, группа адресных входов которой соединена с группой выходов с тремя состояниями второго коммутатора и группой двунаправленных адресных входов/выходов блока управления, информационный выход памяти признаков соединен с выходом признака маски блока управления и через второй элемент НЕ - с выходом признака теста блока управления, управляющий вход памяти признаков соединен со входом записи строки теста блока управления, вход установки нуля одноразрядного буферного регистра соединен с первым управляющим входом блока управления, вход записи одноразрядного буферного регистра соединен со вторым управляющим входом блока управления, вход параллельной записи счетчика адреса соединен со входом записи адреса блока управления, вход установки в единичное состояние RS-триггера пуска соединен со входом пуска блока управления, третий вход первого элемента ИЛИ соединен со входом сброса блока управления, управляющий вход первого коммутатора соединен со входом чтения состояния блока управления, группа входов обнаружения сбоев блока управления соединена с группой входов второго элемента ИЛИ и группой информационных входов четвертого коммутатора, управляющий вход которого соединен со входом чтения сбоев блока управления, управляющий вход третьего коммутатора соединен со входом чтения адреса блока управления, инверсный выход RS-триггера пуска соединен с выходом блокировки адреса блока управления.

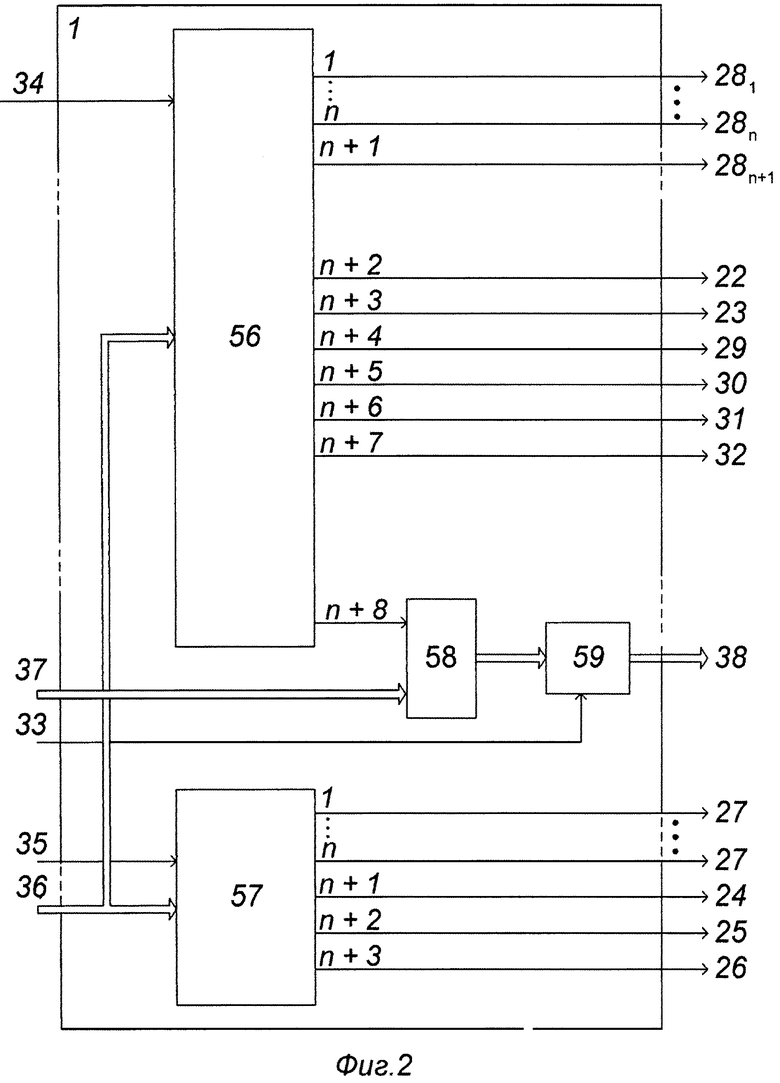

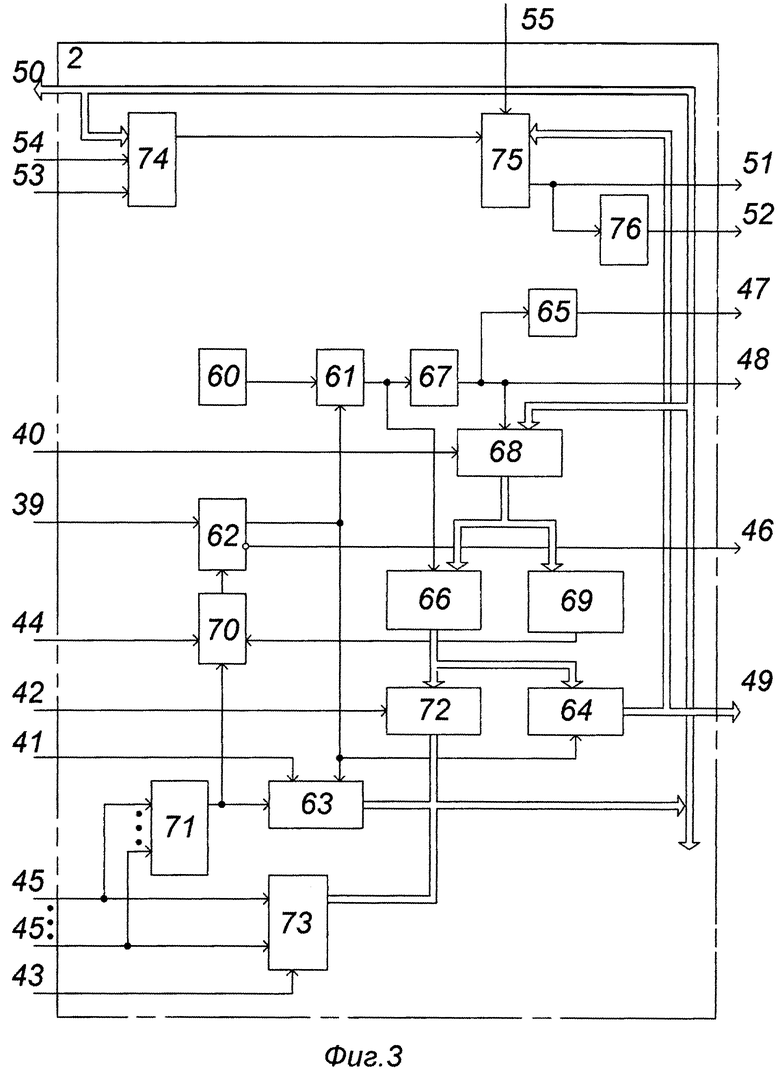

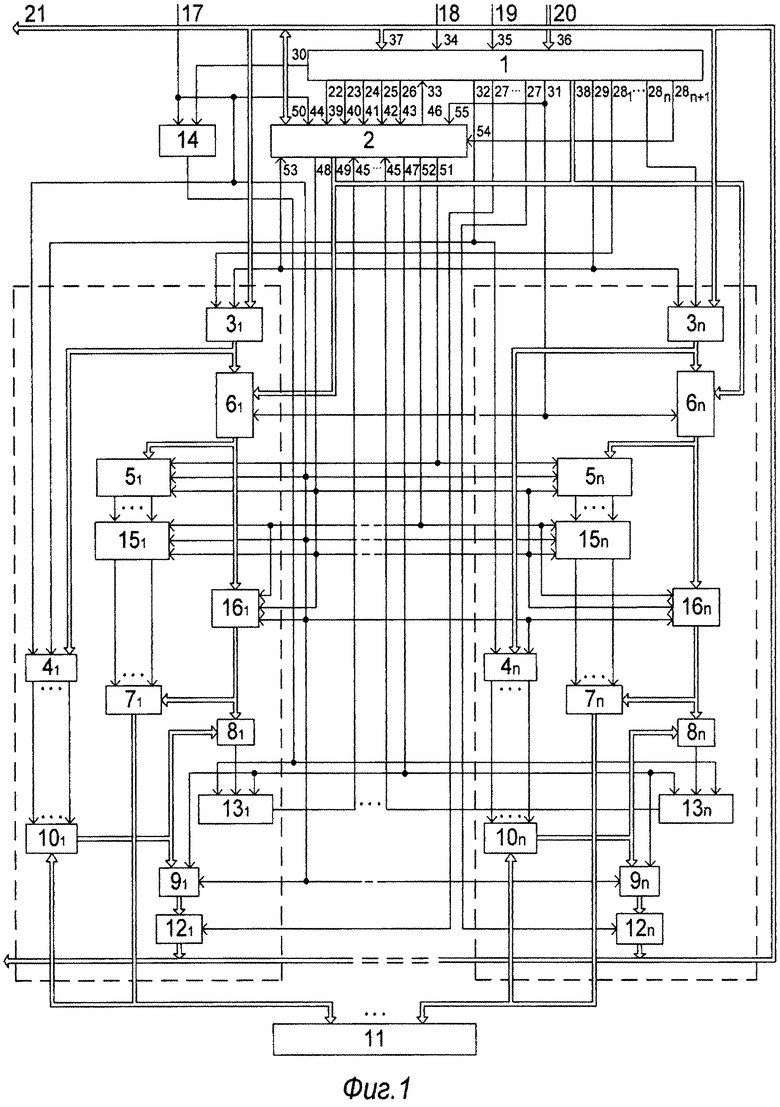

Предлагаемое устройство поясняется прилагаемыми чертежами, где на фиг. 1 приведена структурная схема устройства тестового контроля; на фиг. 2 - структурная схема блока сопряжения; на фиг. 3 - структурная схема блока управления. Показанный на фиг. 1 проверяемый узел в состав устройства не входит, а приведен для пояснения описания.

Устройство тестового контроля (УТК) содержит блок 1 сопряжения, блок 2 управления, n входных регистров 3, n регистров 4 маски входов/выходов, n регистров 5 маски входов, n блоков 6 памяти, первую группу n коммутаторов 7, n блоков 8 сравнения, n регистров 9 результата, вторую группу n коммутаторов 10, проверяемый узел 11, n выходных коммутаторов 12, n триггеров 13 сбоя, элемент ИЛИ 14, n управляющих регистров 15, n регистров 16 теста, вход 17 сброса устройства, вход 18 записи и вход 19 чтения устройства, входную шину 20 адреса и входную двунаправленную шину 21 данных устройства, выход 22 пуска блока 1 сопряжения, выход 23 установки начального адреса блока 1 сопряжения, выход 24 чтения состояния блока 1 сопряжения, выход 25 чтения адреса блока 1 сопряжения, выход 26 чтения сбоев блока 1 сопряжения, группу выходов 27 выдачи результата блока 1 сопряжения, группу стробирующих выходов 28 блока 1 сопряжения, выход 29 установки в ноль блока 1 сопряжения, выход 30 сброса триггера сбоя блока 1 сопряжения, выход 31 записи строки теста блока 1 сопряжения, выход 32 записи маски входов/выходов блока 1 сопряжения, вход 33 блокировки адреса блока 1 сопряжения, первый 34 и второй 35 управляющие входы блока 1 сопряжения, группу входов 36 адреса блока 1 сопряжения, группу информационных входов 37 блока 1 сопряжения, группу адресных выходов 38 с тремя состояниями блока 1 сопряжения, а также вход 39 пуска блока 2 управления, вход 40 записи адреса блока 2 управления, вход 41 чтения состояния блока 2 управления, вход 42 чтения адреса блока 2 управления, вход 43 чтения сбоев блока 2 управления, вход 44 сброса блока 2 управления, группу входов 45 обнаружения сбоев блока 2 управления, выход 46 блокировки адреса блока 2 управления, выход 47 стробирования результата блока 2 управления, выход 48 строба записи блока 2 управления, группу двунаправленных адресных входов/выходов 49 блока 2 управления, группу информационных входов/выходов 50 блока 2 управления, выход 51 признака маски блока 2 управления, выход 52 признака теста блока 2 управления, первый 53 и второй 54 управляющие входы блока 2 управления, вход 55 записи строки теста блока 2 управления.

Блок 1 сопряжения состоит из дешифратора 56 записи, дешифратора 57 чтения, регистра 58 адреса ячейки памяти и коммутатора 59 с тремя состояниями на выходах.

Блок 2 управления содержит генератор 60 тактовых импульсов, элемент И 61, RS-триггер 62 пуска, первый 63 и второй 64 коммутаторы, элемент 65 задержки, регистр 66 адреса, первый элемент НЕ 67, счетчик 68 адреса, элемент ИЛИ-НЕ 69, первый 70 и второй 71 элементы ИЛИ, третий 72 и четвертый 73 коммутаторы, одноразрядный буферный регистр 74, память 75 признаков, а также второй элемент НЕ 76.

Устройство работает следующим образом.

Перед началом работы УТК устанавливается в исходное состояние. Для этого через вход 17 устройства подается сигнал сброса, который поступает на входы установки в ноль всех регистров 41-4n, 51-5n, 91-9n, 151-15n, 161-16n и устанавливает их в исходное состояние, пройдя через вход 44 блока 2 и через первый элемент ИЛИ 70, устанавливает в нулевое состояние триггер 62 пуска, и, пройдя через элемент ИЛИ 14, устанавливает в нулевое состояние триггеры 131-13n сбоя.

УТК работает в трех режимах: режим I - загрузка; режим II - тестирование; режим III - анализ результатов тестирования.

Режим загрузки включает следующие операции:

1. Установка входных регистров 31-3n и одноразрядного буферного регистра 74 блока 2 в исходное состояние;

2. Формирование маски контролируемых выводов проверяемого узла во входных регистрах 31-3n и перезапись этой маски в регистры 41-4n маски входов/выходов;

3. Подцикл формирования строки тестовой информации во входных регистрах 31-3n и в одноразрядном буферном регистре 74 блока 2 и перезапись сформированной строки тестовой информации по заданному адресу в блоки памяти 61-6n и в память 75 признаков блока 2 соответственно;

4. Загрузка необходимой информации в блок 2 управления.

Рассмотрим выполнение этих операций.

1. Установка входных регистров 31-3n и одноразрядного буферного регистра 74 блока управления в исходное состояние осуществляется следующим образом.

Через группу входов 36 адреса блока 1 с входной шины 20 адреса устройства на управляющие входы дешифратора 56 поступает адрес команды «Установка в ноль входных регистров», и при поступлении сигнала «Запись» со входа 18 записи устройства через вход 34 блока 1 на стробирующий вход дешифратора 56 выдается с выхода 29 блока 1 сигнал установка в ноль, который поступает на входы установки в ноль входных регистров 31-3n и через вход 53 блока 2 на вход установки в ноль буферного регистра 74 блока 2, устанавливая их в нулевое состояние.

2. Формирование маски контролируемых выводов проверяемого узла во входных регистрах 31-3n и перезапись этой маски в регистры 41-4n маски входов/выходов осуществляется следующим образом.

По входной шине 21 данных устройства поступает m-разрядный фрагмент (где m - разрядность входной шины данных УТК) I-разрядной маски контролируемых выводов проверяемого узла (где I=m×n) и устанавливается на информационных входах входных регистров 31-3n. Запись происходит по сигналу, поступающему с соответствующего выхода группы выходов 28 блока 1 в тот входной регистр 31-3n, адрес которого выставлен на входах дешифратора 56 блока 1 через группу входов 36 адреса с шины 20 адреса устройства при поступлении сигнала «Запись» на стробирующий вход дешифратора 56 через вход 34 блока 1 с входа 18 устройства. Описанный процесс загрузки фрагментов строки во входные регистры повторяется n раз, где n - число входных регистров. В результате сформированная I-разрядная строка информации, представляющая собой управляющую информацию (маску) об используемых выводах проверяемого узла 11 («1» - контролируемые входы/выходы; «0» - остальные выводы), устанавливается на информационных входах регистров 41-4n маски входов/выходов. Затем на управляющие входы дешифратора 56 через группу входов 36 адреса с шины 20 адреса устройства поступает адрес команды «Запись маски входов/выходов», и при поступлении на стробирующий вход дешифратора 56 через первый управляющий вход 34 блока 1 со входа 18 устройства сигнала «Запись» на выходе 32 блока 1 появится сигнал «Запись маски входов/выходов», при поступлении которого на вход параллельной записи регистров 41-4n в указанные регистры записывается управляющая информация с выходов входных регистров 31-3n.

3. Подцикл формирования строки тестовой информации во входных регистрах 31-3n и в одноразрядном буферном регистре 74 блока 2 и перезапись сформированной строки тестовой информации по заданному адресу в блоки памяти 61-6n и в память 75 признаков блока 2 соответственно осуществляется следующим образом.

По шине 21 данных устройства поступает m-разрядный фрагмент (I+1)-разрядной строки тестовой информации и устанавливается на информационных входах входных регистров 31-3n и буферного регистра 74 блока 2. Запись происходит по сигналу, вырабатываемому при поступлении сигнала «Запись» на стробирующий вход дешифратора 56 через вход 34 блока 1 со входа 18 устройства и поступающему с соответствующего выхода группы выходов 28 блока 1 в тот регистр (31-3n или 74), адрес которого выставлен на управляющие входы дешифратора 56 блока 1 через группу входов 36 адреса с шины 20 адреса устройства. Описанный процесс загрузки фрагментов строки тестовой информации во входные регистры 31-3n и буферный регистр 74 повторяется (n+1) раз, при этом за n тактов в регистры 31-3n запишется n×m разрядов, представляющих собой строку теста (тестовые воздействия для выводов, являющихся входами проверяемого узла, и эталонные значения для выводов, являющихся контролируемыми выходами этого узла) или маску входов проверяемого узла 11, а в (n+1) такте в буферный регистр 74 запишется признак, определяющий какая информация (строка теста или маска) записана во входные регистры 31-3n. В результате сформированная в регистрах 31-3n и буферном регистре 74 (I+1)-разрядная строка тестовой информации устанавливается на информационных входах блоков 61-6n памяти и памяти 75 признаков соответственно для записи в ячейки памяти с определенным адресом.

Для этого по входной шине 21 данных устройства поступает адрес r-й ячейки памяти (где r ∈ {1, 2, …, kмакс}, kмакс - максимальное количество строк в тесте) и через группу входов 37 блока 1 устанавливается на информационных входах регистра 58. По шине 20 адреса через группу входов 36 адреса блока 1 поступает на дешифратор 56 адрес команды «Запись адреса ячейки памяти» и при поступлении сигнала «Запись» через вход 34 блока 1 на (n+8)-м выходе дешифраторе 56 появляется сигнал, при поступлении которого на вход параллельной записи регистра 58 в этот регистр произойдет запись адреса r-й ячейки памяти. С выходов регистра 58 адрес r-й ячейки памяти через коммутатор 59, разблокированный высоким уровнем сигнала с инверсного выхода триггера 62 блока 2 (поступающим через выход 46 блокировки адреса блока 2 и вход 33 блока 1 на управляющий вход этого коммутатора), подается через группу адресных выходов 38 блока 1 на группу адресных входов блоков 61-6n памяти и через группу адресных входов/выходов 49 блока 2 на группу адресных входов памяти 75 признаков блока 2 (выходы коммутатора 64 при этом переведены в высокоимпедансное состояние низким уровнем сигнала с единичного выхода триггера 62 блока 2).

Запись строки тестовой информации из входных регистров 31-3n и буферного регистра 74 в блоки 61-6n памяти и в память 75 признаков соответственно осуществляется по команде «Запись строки теста», при выполнении которой с (n+6)-го выхода дешифратора 56 через выход 31 блока 1 поступает на вход записи блоков 61-6n памяти и через вход 55 блока 2 на вход записи памяти 75 признаков сигнал записи, по которому осуществляется запись информации в r-ю ячейку памяти блоков 61-6n памяти и памяти 75 признаков.

Описанные процессы формирования строки тестовой информации во входных регистрах 31-3n и буферном регистре 74 с последующей перезаписью ее в блоки 61-6n памяти и в память 75 признаков соответственно производится kмакс раз.

4. Режим I завершается загрузкой адреса начала теста в счетчик 68 адреса блока 2 управления по команде «Установка начального адреса», при выполнении которой адрес начала теста с шины 21 данных через группу входов/выходов 50 блока 2 записывается в данный счетчик 68 при поступлении сигнала записи с (n+3)-го выхода дешифратора 56 через выход 23 блока 1 и вход 40 блока 2 на вход параллельной записи счетчика 68.

На этом режим загрузки завершается.

Режим тестирования (режим II) задается подачей команды «Пуск», при поступлении которой вырабатывается сигнал на (n+2)-м выходе дешифратора 56, который через выход 22 блока 1, вход 39 блока 2 поступает на S-вход RS-триггера 62 пуска, устанавливая его в единичное состояние. Появление нулевого потенциала с инверсного выхода триггера 62 пуска через выход 46 блока 2 и вход 33 блока 1 на управляющем входе коммутатора 59 блока 1 переводит его выходы в высокоимпедансное состояние, блокируя поступление адреса ячейки памяти из блока 1.

Единичный потенциал с прямого выхода триггера 62 разрешает прохождение тактовых импульсов с выхода генератора 60 тактовых импульсов через элемент И 61 на вход параллельной записи регистра 66 адреса. По переднему фронту первого тактового импульса, пришедшего на вход параллельной записи регистра 66, адрес начала теста переписывается с выходов счетчика 68 адреса в регистр 66 адреса, с выходов которого через второй коммутатор 64 (передача информации через него разрешена единичным потенциалом с прямого выхода триггера 62 пуска, поступающим на управляющий вход этого коммутатора) поступает на адресные входы памяти 75 признаков и через группу адресных входов/выходов 49 блока 2 - на адресные входы блоков 61-6n памяти. Происходит считывание (сигнал записи снят) значения первой строки тестовой информации. При этом тестовая информация с выходов блоков 61-6п памяти поступит на информационные входы регистров 51-5n маски входов и регистров 161-16n теста, а с выхода памяти 75 признаков через выход 51 признака маски - на вход разрешения записи регистров 51-5n маски входов и через элемент НЕ 76 и выход 52 признака теста - на вход разрешения записи управляющих регистров 151-15n и вход разрешения записи регистров 161-16n теста. В результате, если считанная информация является маской входов проверяемого узла, то на выходе памяти 75 признаков будет единичный сигнал, который поступит как разрешающий сигнал на вход разрешения записи регистров 51-5n маски входов, и по заднему фронту тактового импульса, проинвертированного на элементе НЕ 67, и поступившего через выход 48 строба записи блока 2 на тактовые входы регистров 51-5n, 151-15n, 161-16n, тестовая информация с выходов блоков 61-6n памяти запишется в регистры 51-5n маски входов как управляющая информация. Если же считанная информация является очередной строкой теста, то на выходе памяти 75 признаков будет нулевой сигнал, который, проинвертировавшись на элементе НЕ 76, поступит единичным сигналом на входы разрешения записи управляющих регистров 151-15n и регистров 161-16n теста и по поступившему заднему фронту тактового импульса с выхода 48 строба записи блока 2 в управляющие регистры 151-15n будет перезаписана новая маска входов (или подтверждена ранее установленная) с выходов регистров 51-5n маски входов, а в регистры 161-16n теста одновременно будет записана с выходов блоков 61-6n памяти очередная строка теста, которая через коммутаторы 71-7n, управляемые маской входов с выходов регистров 151-15n (все выводы проверяемого узла, являющиеся в текущем тесте входами (включая и двунаправленные выводы), определены как входы записью «1» в соответствующие разряды регистров 151-15n), поступит в качестве текущего тестового воздействия на входы проверяемого узла 11.

С выходов проверяемого узла 11 через коммутаторы 101-10n реакция проверяемого узла 11 на поступившее тестовое воздействие поступит на первую группу входов блоков 81-8n сравнения и на информационные входы регистров 91-9n результата.

Результаты сравнения («0» - если сбой, т.е. несравнение; «1» - в противном случае) с инверсных выходов блоков 81-8n сравнения поступают на информационные входы триггеров 131-13n сбоя. Запись в D-триггеры 131-l3n результата сравнения и в регистры 91-9n результата реакции проверяемого узла 11 происходит по переднему фронту тактового импульса, поступающего с выхода 47 блока 2 на тактирующие входы D-триггеров 131-13n сбоя и входы параллельной записи регистров 91-9n результата, и задержанного на элементе 65 задержки на величину τ, причем τ≤Т/2 (где Т=1/f; f - частота работы УТК). Величина τ определяется как сумма задержек при прохождении информации до проверяемого узла 11, при срабатывании проверяемого узла 11 и при прохождении реакции проверяемого узла 11 через коммутаторы 101-10n и блоки 81-8n сравнения. С выходов триггеров 131-13n сбоя сигналы «Сбой» поступают через группу входов 45 обнаружения сбоев на элемент ИЛИ 71 и группу информационных входов коммутатора 73 блока 2. Далее работа устройства определяется значениями сигналов «Сбой».

Если сигналы «Сбой» равны нулю, то работа устройства продолжается следующим образом.

По заднему фронту первого тактового импульса, поступающему через элемент НЕ 67 на вычитающий вход счетчика 68 адреса, его содержимое уменьшается на единицу. По переднему фронту следующего тактового импульса уменьшенное на единицу содержимое счетчика 68 переписывается в регистр 66 адреса, с выходов которого адрес следующей строки теста поступает через коммутатор 64 на адресные входы памяти 75 признаков и через группу входов/выходов 49 блока 2 - на адресные входы блоков 61-6n памяти. Происходит считывание следующей строки теста, которая в зависимости от считанного сигнала с памяти 75 признаков записывается либо в регистры 51-5n маски входов (при необходимости изменения этой маски, при этом тестовое воздействие не меняется), либо в регистры 161-16n теста в качестве информации следующего такта тестирования, при этом соответствующая этому тесту маска входов одновременно переписывается из регистров 51-5n маски входов в управляющие регистры 151-15n.

Описанный процесс тестирования продолжается до тех пор, пока содержимое счетчика 68 адреса не станет равным нулю (без сбоев прошел весь тест) или на выходе элемента ИЛИ 71 блока 2 не появится единичный потенциал (прошел сигнал «Сбой», т.е. обнаружено несоответствие результата эталону).

Если содержимое счетчика 68 адреса равно нулю, то на выходе элемента ИЛИ-НЕ 69 появляется единичный сигнал, который через элемент ИЛИ 70 поступает на вход установки в ноль RS-триггера 62 пуска и устанавливает его в нулевое состояние. Нулевой потенциал с прямого выхода триггера 62 пуска блокирует поступление тактовых импульсов через элемент И 61 и происходит «Останов» устройства.

«Останов» устройства происходит также при появлении единичного сигнала на выходе элемента ИЛИ 71, поступающего через элемент ИЛИ 70 на вход установки в ноль RS-триггера 62 пуска вследствие обнаруженного несоответствия результата тестирования эталонному значению.

Режим анализа результатов тестирования (режим III) начинается, когда в режиме тестирования триггер 62 пуска блока 2 устанавливается в нулевое состояние. Для анализа состояния устройства используется команда «Чтение состояния устройства», при выполнении которой адрес данной команды по входной шине 20 адреса через группу входов 36 блока 1 подается на дешифратор 57 чтения и при появлении сигнала «Чтение» на стробирующем входе данного дешифратора (через вход 35 блока 1 со входа 19 устройства), на (n+1)-м выходе дешифратора 57 вырабатывается сигнал, поступающий через выход 24 блока 1 и вход 41 блока 2 на управляющий вход коммутатора 63, с выхода которого через группу входов/выходов 50 блока 2 на шину 21 данных передается код состояния устройства. Код состояния содержит два разряда р[о], р[1], снимаемых с прямого выхода триггера 62 пуска (р[о]) и с выхода элемента ИЛИ 71 сборки всех сбоев устройства (р[1]). В зависимости от кода состояний (р[о] р[1]=00 - исходное состояние устройства; р[о] р[1]=10 - режим тестирования; р[о] р[1]=01 - останов по сбою; р[о] р[1]=11 - нет сброса триггера пуска) пользователь устройства может выполнять следующие действия.

Если после сброса устройства код состояния р[о] р[1]≠00, то устройство неисправно и его необходимо отремонтировать.

Если после подачи команды «Пуск» код состояния р[о] р[1]=10, то устройство находится в режиме тестирования и необходимо сделать перерыв на время тестирования, если же и после этого код состояния не изменился, то устройство неисправно. В противном случае, при р[о] р[1]=00, тестирование прошло успешно и необходимо загрузить следующий тест, а при р[о] р[1]=01 обнаружено несоответствие эталону реакции проверяемого узла 11 на входное воздействие и можно вывести необходимую для анализа неисправностей следующую контрольную информацию: адрес сбойной строки теста, фрагменты реакции проверяемого узла 11 на входное воздействие, источники сбоев.

Вывод адреса сбойной строки теста осуществляется по команде «Чтение регистра адреса», при выполнении которой с (n+2)-го выхода дешифратора 57 через выход 25 блока 1 и вход 42 блока 2 на управляющий вход коммутатора 72 подается сигнал, разрешающий передачу адреса сбойной строки теста с выходов регистра 66 адреса через данный коммутатор и группу входов/выходов 50 блока 2 на шину 21 данных.

Вывод информации об источниках всех сбоев (при условии, что n≤m) осуществляется по команде «Чтение сбоев», при выполнении которой с (n+3)-го выхода дешифратора 57 через выход 26 блока 1 и вход 43 блока 2 на управляющий вход коммутатора 73 подается сигнал, разрешающий передачу информации с прямых выходов D-триггеров 131-13n сбоев через данный коммутатор и группу входов/выходов 50 блока 2 на шину 21 данных устройства.

На основании анализа информации о сбоях (наличие «1» в i-м разряде означает, что информация о сбоях находится в i-м регистре 9 результата) пользователь может вывести фрагменты реакции проверяемого узла 11 на входное воздействие из тех регистров 9 результата, в которых обнаружен сбой. Вывод информации из i-го регистра 9 результата осуществляется по команде «Чтение i-го регистра результата», при выполнении которой с i-го выхода дешифратора 57 через i-й выход группы выходов 27 выдачи результата блока 1 на управляющий вход i-го коммутатора 12 подается сигнал, разрешающий передачу информации с выходов регистра 9j результата через данный коммутатор на шину 21 данных.

Пользователь диагностирует неисправности, устраняет ошибки и производит повторный прогон теста. Подобный итерационный процесс повторяется до устранения всех ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

Предлагаемое устройство относится к области вычислительной техники и может быть использовано в системах контроля и диагностики цифровых вычислительных устройств. Задачей заявляемого устройства является обеспечение возможности независимого оперативного переключения различных групп двунаправленных выводов контроля устройства с передачи тестовой информации на прием ответной реакции с произвольной дискретностью переключения, что позволит проводить тестовый контроль цифровых устройств с несколькими группами двунаправленных линий связи, в частности многопроцессорные системы. Технический результат достигается введением в устройство, содержащее блок сопряжения, блок управления, n входных регистров, n регистров маски входов/выходов, n регистров маски входов, n блоков памяти, первую группу n коммутаторов с тремя состояниями на выходах, n блоков сравнения, n регистров результата, вторую группу n коммутаторов, n выходных коммутаторов, n триггеров сбоя, элемент ИЛИ и n управляющих регистров, дополнительно n регистров теста с соответствующими связями, изменением связей блоков памяти, регистров маски входов, управляющих регистров и соответствующим изменением структуры блока управления устройства. 1 з.п. ф-лы, 3 ил.

1. Устройство тестового контроля, содержащее блок сопряжения, блок управления, n входных регистров, n регистров маски входов/выходов, n регистров маски входов, n блоков памяти, первую группу n коммутаторов с тремя состояниями на выходах, n блоков сравнения, n регистров результата, вторую группу n коммутаторов, n выходных коммутаторов, n триггеров сбоя, элемент ИЛИ, n управляющих регистров, причем группа адресных входов i-го (где i=1, 2, …, n) блока памяти соединена с группой адресных выходов с тремя состояниями блока сопряжения и группой двунаправленных адресных входов/выходов блока управления, выход записи строки теста блока сопряжения соединен со входом записи i-го блока памяти, группа информационных выходов i-го входного регистра соединена с группой информационных входов i-го блока памяти и i-го регистра маски входов/выходов, группа выходов которого соединена с группой управляющих входов i-го коммутатора второй группы, группа выходов i-го регистра результата соединена с группой информационных входов i-го выходного коммутатора, управляющий вход которого соединен с i-м выходом группы выходов выдачи результата блока сопряжения, вход записи i-го регистра маски входов/выходов соединен с выходом записи маски входов/выходов блока сопряжения, вход записи i-го входного регистра соединен с i-м выходом группы стробирующих выходов блока сопряжения, вход установки нуля i-го входного регистра соединен с выходом установки в ноль блока сопряжения, инверсный выход i-го блока сравнения соединен с информационным входом i-го триггера сбоя, прямой выход которого соединен с i-м входом группы входов обнаружения сбоев блока управления, вход установки нуля i-го триггера сбоя соединен с выходом элемента ИЛИ, тактирующий вход i-го триггера сбоя и вход записи i-го регистра результата соединены с выходом стробирования результата блока управления, выход установки начального адреса блока сопряжения соединен со входом записи адреса блока управления, выход чтения состояния блока сопряжения соединен со входом чтения состояния блока управления, выход чтения адреса блока сопряжения соединен со входом чтения адреса блока управления, выход чтения сбоев блока сопряжения соединен со входом чтения сбоев блока управления, выход сброса триггера сбоя блока сопряжения соединен с первым входом элемента ИЛИ, выход пуска блока сопряжения соединен со входом пуска блока управления, выход блокировки адреса блока управления соединен со входом блокировки адреса блока сопряжения, первый управляющий вход блока сопряжения подключен ко входу записи устройства, второй управляющий вход блока сопряжения подключен ко входу чтения устройства, группа входов адреса блока сопряжения соединена с входной шиной адреса устройства, входы установки в ноль i-го регистра маски входов, i-го регистра маски входов/выходов, i-го регистра результата, i-го управляющего регистра, вход сброса блока управления, второй вход элемента ИЛИ соединены со входом сброса устройства, группа информационных входов i-го входного регистра, группа информационных входов/выходов блока управления, группа информационных входов блока сопряжения, группа информационных выходов i-го выходного коммутатора соединены с входной двунаправленной шиной данных устройства, группа выходов с тремя состояниями i-го коммутатора первой группы соединена с i-й группой двунаправленных выходов контроля устройства для подключения к проверяемому узлу и группой информационных входов i-го коммутатора второй группы, группа выходов которого соединена с первой группой информационных входов i-го блока сравнения и группой информационных входов i-го регистра результата, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности независимого оперативного переключения различных групп двунаправленных выводов контроля устройства с передачи тестовой информации на прием ответной реакции с различной дискретностью переключения в него дополнительно введен регистр теста, причем группа информационных выходов i-го блока памяти соединена с группой информационных входов i-го регистра маски входов и с группой информационных входов i-го регистра теста, группа информационных выходов которого соединена со второй группой информационных входов i-го блока сравнения и с группой информационных входов i-го коммутатора первой группы, группа управляющих входов которого соединена с группой информационных выходов i-го управляющего регистра, группа информационных входов которого соединена с группой информационных выходов i-го регистра маски входов, вход разрешения записи i-го регистра маски входов соединен с выходом признака маски блока управления, вход разрешения записи i-го регистра теста и вход разрешения записи i-го управляющего регистра соединены с выходом признака теста блока управления, тактовый вход i-го регистра маски входов, тактовый вход i-го регистра теста и тактовый вход i-го управляющего регистра соединены с выходом строба записи блока управления, вход установки в ноль i-го регистра теста подключен ко входу сброса устройства, первый управляющий вход блока управления подключен к выходу установки в ноль блока сопряжения, выход записи строки теста которого подключен также ко входу записи строки теста блока управления, второй управляющий вход которого соединен с (n+1)-м выходом группы стробирующих выходов блока сопряжения.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит генератор тактовых импульсов, элемент И, два элемента НЕ, RS-триггер пуска, четыре коммутатора, элемент задержки, регистр адреса, счетчик адреса, элемент ИЛИ-НЕ, два элемента ИЛИ, одноразрядный буферный регистр, память признаков, причем выход генератора тактовых импульсов соединен с первым входом элемента И, прямой выход RS-триггера пуска соединен с первым информационным входом первого коммутатора, а также с управляющим входом второго коммутатора и вторым входом элемента И, выход которого соединен со входом параллельной записи регистра адреса и через первый элемент НЕ - с вычитающим входом счетчика адреса, выходом строба записи блока управления и со входом элемента задержки, выход которого соединен с выходом стробирования результата блока управления, группа выходов счетчика адреса соединена с группой информационных входов регистра адреса и группой входов элемента ИЛИ-НЕ, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ и вторым информационным входом первого коммутатора, выход первого элемента ИЛИ соединен со входом установки нуля RS-триггера пуска, группа выходов регистра адреса соединена с группами информационных входов второго и третьего коммутатора, группа выходов с тремя состояниями первого, третьего и четвертого коммутаторов соединены с группой информационных входов счетчика адреса и группой информационных входов/выходов блока управления, первый вход/выход из группы информационных входов/выходов блока управления подключен также к информационному входу одноразрядного буферного регистра, выход которого соединен с информационным входом памяти признаков, группа адресных входов которой соединена с группой выходов с тремя состояниями второго коммутатора и группой двунаправленных адресных входов/выходов блока управления, информационный выход памяти признаков соединен с выходом признака маски блока управления и через второй элемент НЕ - с выходом признака теста блока управления, управляющий вход памяти признаков соединен со входом записи строки теста блока управления, вход установки нуля одноразрядного буферного регистра соединен с первым управляющим входом блока управления, вход записи одноразрядного буферного регистра соединен со вторым управляющим входом блока управления, вход параллельной записи счетчика адреса соединен со входом записи адреса блока управления, вход установки в единичное состояние RS-триггера пуска соединен со входом пуска блока управления, третий вход первого элемента ИЛИ соединен со входом сброса блока управления, управляющий вход первого коммутатора соединен со входом чтения состояния блока управления, группа входов обнаружения сбоев блока управления соединена с группой входов второго элемента ИЛИ и группой информационных входов четвертого коммутатора, управляющий вход которого соединен со входом чтения сбоев блока управления, управляющий вход третьего коммутатора соединен со входом чтения адреса блока управления, инверсный выход RS-триггера пуска соединен с выходом блокировки адреса блока управления.

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| Приспособления для получения бортов и ребер жесткости на трубах из винипласта | 1958 |

|

SU141042A1 |

| Устройство для диагностирования цифровых блоков | 1988 |

|

SU1631546A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

Авторы

Даты

2015-10-20—Публикация

2014-12-25—Подача