СЛ

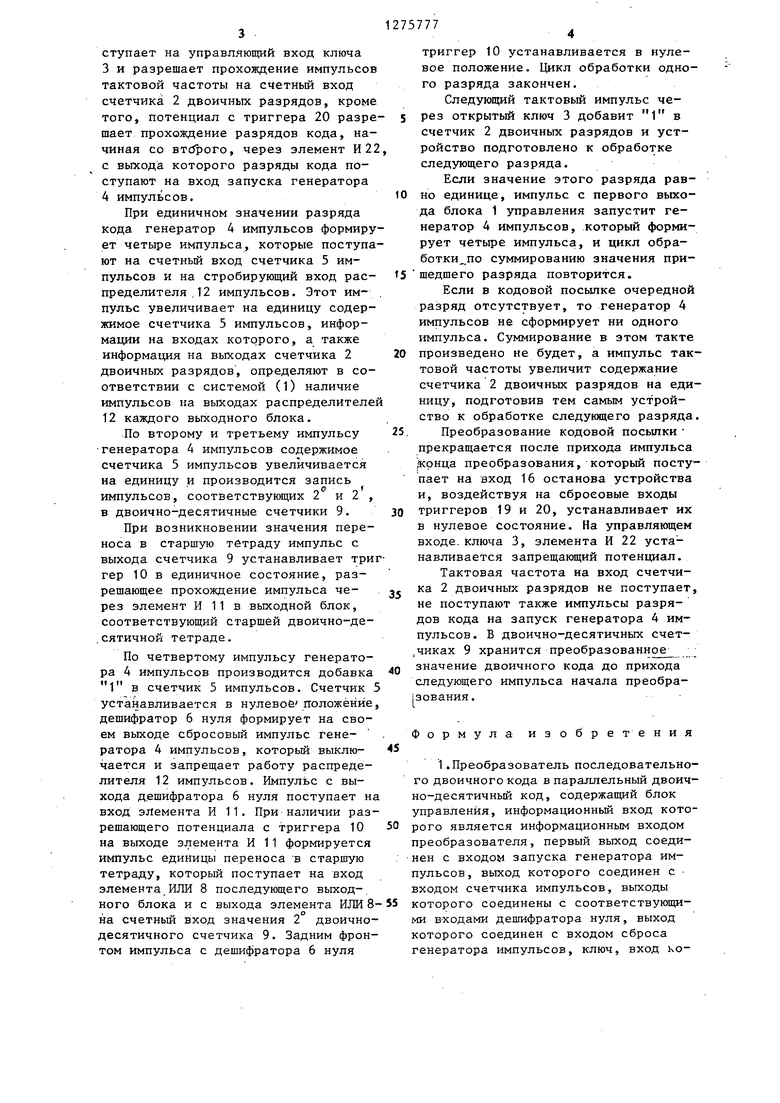

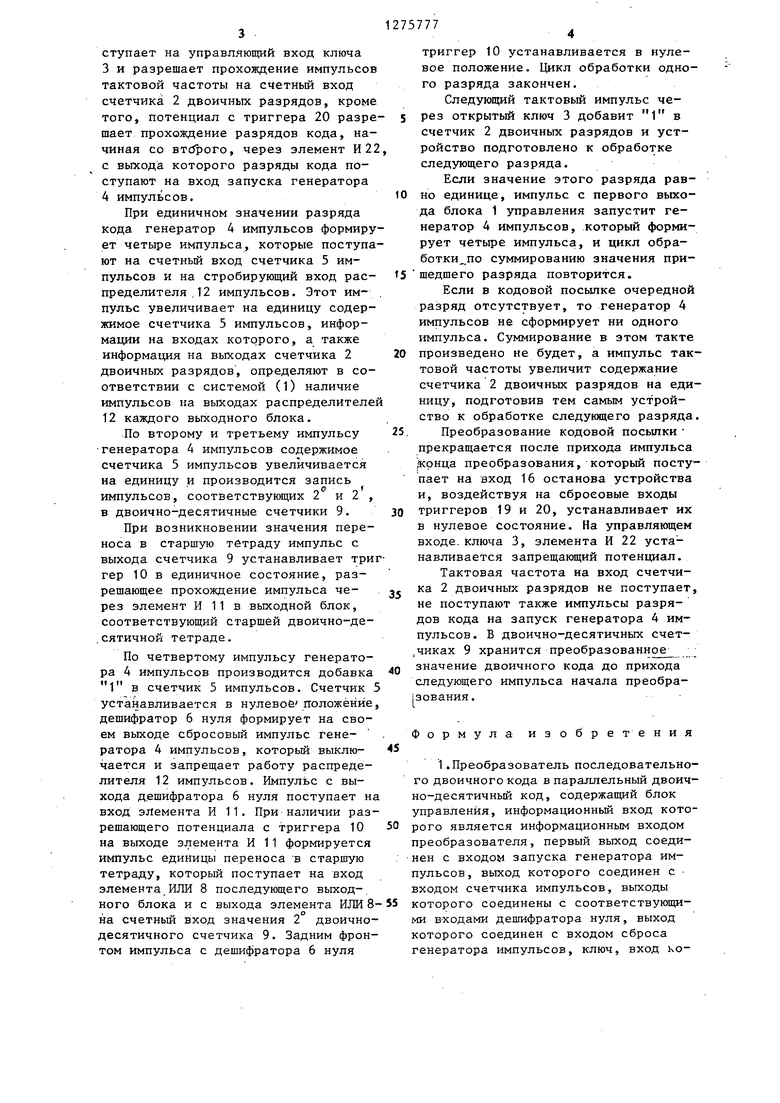

vj Изобретение относится к вычислительной технике и предназначено для преобразования последовательного дво ичного кода переменной длины в параллельн.ый двоично-десятичный код. Целью изобретения является повышение быстродействия и расвшрение об ласти применения преобразователя. На фиг. 1 представлена функциональная схема преобразователя последовательного двоичного кода в параллельный двоично-десятичный код; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - временные диаграммы входного сигнала и сигналов управления. Преобразователь последовательног двоичного кода в паралпельньй двоич но-десятичный код содержит блок 1 у равления, счетчик 2 двоичных разрядов, ключ 3, генератор 4 импульсов, счетчик 5 импульсов, дешифратор 6 нуля, выходные блоки 7, каждый из которых содержит элемент ИЛИ 8, дво ично-десятичный счетчик 9, триггер 10, элемент И 11, распределитель 12 импульсов. Кроме Того, на фиг. 1 обозначены вход 13 запуска, тактовый h информационный входы 14 и 15 соответственно и вход 16 останова. Блок 1 управления (фиг.2) содержит четыре триггера 17-20 и два эле мента И 21 к 22. Преобразователь работает следуюпщм образом. Преобразование входного кода осу ществляется путем накопления в двои но-десятичных счетчиках 9 эквивален двоичного числа. Накопление десятичных зквивален тов производится двоично-десятичным счетчиком 9 путем пересчета разнесе .ных во времени импульсов значений составляющих десятичного разряда. Значения десятичного разряда при вв де его -вдвс5ично-десятичный счетчи с 9 представлены в виде следующих сумм значений его составляющих 9(2 +2)+ ()+ (); 8(2°4-2М + (2°+2) 7(2°+2) + (2%2)+2°; 6(2°+2)+(2°+2); 5(2%2М+2 ; 4 2+2; ; ; . Составляющие 2° и 2 вводятся в счетчик 9 через первый и второй входы -соответственно за один такт, 2 вводится по переднему фронту импульса, 2 .-по заднему фронту этого же импульса . Обработка разряда двоичного кода производится за четьфе такта. Первые три такта - ввод составляющих десяг тичного разряда в двоично-десятичный счетчик 9, четвертый такт - ввод в счетчик 9 значения переноса. Формирование единицы переноса в старшую тетраду производится элементом И 11, первый вход которого соединен с вгзпсодом триггера 10, а второй вход - с выходом дешифратора 6 нуля. Разнесение во времени импульсов, подаваемых на входы двоично-десятичного счетчика 9, осуществляется в распределителе 12 импульсов, который может быть реализован на основе ИЛИ или ПЗУ. Импульс начала кода, поступающий на вход 13 запуска устанавливает в нулевое состояние счетчик 2 двоичных разрядов и двоично-десятичный счетчик 9 и, воздействуя на управляющий вход триггера 17, устанавливает его в единичное состояние. Импульсы тактовой частоты, тактовый вход 14 блока 1 управления, воздействуя на сбросовый вход триггера 17, устанавливают его в нулевое состояние. Задним фронтом импульса с триггера 17 триггер 18 устанавливается в единичное состояние, разрешая прохождение импульсов входного кода, поступающих на информационный вход 15 и первый вход элемента И 21, с выхода KOTopioro импульсы поступают на установочный вход триггера 19. При единичном значении первого разряда в кодовой посьшке триггер 19 устанавливается в единичное состояние, соответствующее обработке двоичного кода,,-поступающего младшими разрядами вперед. Выходной сигнал с триггера 19 поступает на первый вход распределителя 12 импульсов и выбирает программу преобразования кода. Одновременно триггер 18 задним фронтом своего импульса устанавливает триггер 20 в еди1 ичное состояние, соответствукнцее разрешению преобразования кодовой посылки. Выходной сигнал с триггера 20 поступает на управляющий вход ключа 3и разрешает прохождение импульсов тактовой частоты на счетный вход счетчика 2 двоичньгх разрядов, кроме того, потенциал с триггера 20 разре шает прохождение разрядов кода, начиная со втброго, через элемент И 2 с выхода которого разряды кода поступают на вход запуска генератора 4импульсов. При единичном значении разряда кода генератор 4 импульсов формиру ет четыре импульса, которые поступа ют на счетньй вход счетчика 5 импульсов и на стробирующий вход распределителя . 12 импульсов. Этот импульс увеличивает на единицу содержимое счетчика 5 импульсов, информации на входах которого, а также информация на выходах счетчика 2 двоичных разрядов, определяют в соответствии с системой (1) наличие импульсов на выходах распределителе 12 каждого выходного блока. По второму и третьему импульсу генератора 4 импульсов содержимое счетчика 5 импульсов увеличивается на единицу и производится запись импульсов, соответствующих 2 и 2 , в двоично-десятичные счетчики 9. При возникновении значения переноса в старшую тетраду импульс с выхода счетчика 9 устанавливает три гер 10 в единичное состояние, разрешающее прохождение импульса через элемент И 11 в выходной блок, соответствующий старшей двоично-де. сятичной тетраде. По четвертому импульсу генератора 4 импульсов производится добавка 1 в счетчик 5 импульсов. Счетчик устанавливается в нулевоеположение дешифратор 6 нуля формирует на своем выходе сбросовый импульс генератора 4 импульсов, который выключается и запрещает работу распределителя 12 импульсов. Импульс с выхода дешифратора 6 нуля поступает н вход элемента И 11. При наличии раз решающего потенциала с триггера 10 на выходе элемента И 11 формируется импульс единицы переноса в старшую тетраду, который поступает на вход элемента ИЛИ 8 последующего выход-. ного блока и с выхода элемента ИЛИ 8 на счетный вход значения 2 двоично десятичного счетчика 9. Задним фронтом импульса с дешифратора 6 нуля триггер 10 устанавливается в нулевое положение. Цикл обработки одного разряда закончен. Следующий тактовый импульс через открытый ключ 3 добавит 1 в счетчик 2 двоичных разрядов и устройство подготовлено к обработке следующего разряда. Если значение этого разряда равно единице, импульс с первого выхода блока 1 управления запустит генератор 4 импульсов, который формирует четыре импульса, и цикл обработки по суммированию значения пришедшего разряда повторится. Если в кодовой посылке очередной разряд отсутствует, то генератор 4 импульсов не сформирует ни одного импульса. Суммирование в этом такте произведено не будет, а импульс тактовой частоты увеличит содержание счетчика 2 двоичных разрядов на единицу, подготовив тем самым устройство к обработке следующего разряда. Преобразование кодовой посылки прекращается после прихода импульса рнца преобразования, который поступает на вход 16 останова устройства и, воздействуя на сбросовые входы триггеров 19 и 20, устанавливает их в нулевое состояние. На управляющем входе, ключа 3, элемента И 22 устанавливается запрещающий потенциал. Тактовая частота на вход счетчика 2 двоичных разрядов не поступает, не поступают также импульсы разрядов кода на запуск генератора 4 импульсов. В двоично-десятичных счетчиках 9 хранится преобразованное ; значение двоичного кода до прихода следующего импульса начала преобразования. ормула изобретения 1 .Преобразователь последовательноо двоичного кода в параллельный двоичо-десятичный код, содержащий блок правления, информационный вход котоого является информационным входом реобразователя, первый выход соедиен с входом запуска генератора имульсов, выход которого соединен с ходом счетчика импульсов, выходы оторого соединены с соответствующии входами дешифратора нуля, выход оторого соединен с входом сброса енератора импульсов, ключ, вход которого является тактовым входом преобразователя, выход ключа соединен со счетным входом счетчика двоичных разрядов, выходные блоки, каждьй из которых содержит элемент ИЛИ, отличающийся тем, что, с целью повьппения его быстродействия и расширения области применения,, в каждый выходной блок введены распределитель импульсов, триггер, эл гмент И и двоично-десятичный счетчик, разрядные вьпсоды которого являются соответствующими выходами устройства, выход переноса соединен с установочным входом триггера, выход .которого соединен с первым входом элемента И, первый выход распределителя импульсов соединен с первым входом эжзмента ИЛИ, выход которого соединен с входом младшего разряда двоично-деся тичного счетчика, выход второго разряда которого подключен к второму выходу распределителя импульсов, выход элементов И каждого выходного блока, кроме последнего, соединен с вторым входом элемента ИЛИ последующего выходного блока, второй выход блока управления соединен с управляющим входом ключа,третий выход блока управления соединен с первыми входами распределителей импульсов всйх выходньгх блоков, первый и второй выходы счетчика импульсов подключены соответственно к второму и третьему входам распределителей импульсов каж. дого выходного блока, выходы счетчика двоичных разрядов соединены с четвертыми входами распределителей импульсов всех выходных блоков, пятые входы которьк подключены к выходу генератора импульсов, второй вход

элемента И и вход сброса триггера каждого выходного блока подключен к выходу дешифратора нуля, входы сброса двоично-десятичных счетчиков всех выходных блоков и счетчика двоичных разрядов и вход запуска блока управления объединены и являются входом запуска преобразователя, вход останова блока управления является входом останова преобразователя, тактовый вход блока управления подключен к тактовому входу преобразователя.

2. Преобразователь по п. 1, отличающийся тем, что блок управления содержит триггеры, и элементы И, первые входы которых объединены и подключены к информационному входу блока управления, установочньщ вход первого триггера является входом запуска блока управления, выход первого триггера соединен с установочным входом второго триггера, прямой выход которого соединен с вторым входом первого элемента И, выход которого подключен к установочному входу третьего триггера, вход сброса которого соединен с входом сброса четвертого триггера и подключен к входу останова блока управления, входы сброса первого и второго триггеров объединены и являются тактовым входом блока управления, инверсный выход второго триггера подключен к установочному входу четвертого триггера, выход которого подключен к второму входу второго элемента И и являются вторым входом блока управления, выход второго элемента И и выход третьего триггера является соответственно первым и третьим выходами блока управления.

/4 /J о

/5

16

о

СОтСЮ тх

НИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный масштабированный код | 1978 |

|

SU767750A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU744546A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1983 |

|

SU1130858A1 |

Изобретение относится к вычислительной технике. Цель изобретенияповышение быстродействия и расшире- . ние области применения преобразов.ателя. Преобразователь содержит блок управления, ключ, счетчик двоичных разрядов, генератор импульсов, счетчик импул сов, дешифратор нуля, выходные блоки, каждый из которых содержит элемент ИЖ, двоично-десятичный счетчик, триггер, элемент И и распределитель импульсов, Введение распределителя, двоично-десятичного счетчика, триггера и элемента И позволяет расширить область приме нения устройства за счет обеспече ния возможности преобразования двоичного кода, ,поступающего как младшими, так и старшими разрядами вперед. 1 з.п. ф-лы, 3 ил. СЛ

fl

Us 2

«J f 5 /7

л г

/2

1

/

l

ш

IT

1/- /

f

v:

/f. 24fO

i

/ 24 J

:i 13

у/г

«inif(

r/J

t Ifln

и

щ

,№

i2..24W

L

1Ь

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый | 1979 |

|

SU842784A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

Авторы

Даты

1986-12-07—Публикация

1985-01-16—Подача