(54) ЦИФРОВОЙ ДЕМОДУЛЯТОР ЧАСТОТНОМАНИПУЛИРОВАННЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой демодулятор частотно- МАНипулиРОВАННыХ СигНАлОВ | 1979 |

|

SU815960A1 |

| Цифровой демодулятор частотно-манипулированных сигналов | 1982 |

|

SU1058083A1 |

| Цифровой демодулятор сигналовчАСТОТНОй ТЕлЕгРАфии | 1979 |

|

SU794764A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Система передачи и приема информации рекуррентными последовательностями | 1985 |

|

SU1338101A1 |

| Демодулятор сигналов с минимальной частотной манипуляцией | 1986 |

|

SU1354436A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| Устройство для передачи электрокардиосигнала по телефону | 1985 |

|

SU1286158A1 |

| Демодулятор сигналов с минимальной частотной манипуляцией | 1985 |

|

SU1261136A1 |

| Цифровой демодулятор сигналов | 1989 |

|

SU1589420A1 |

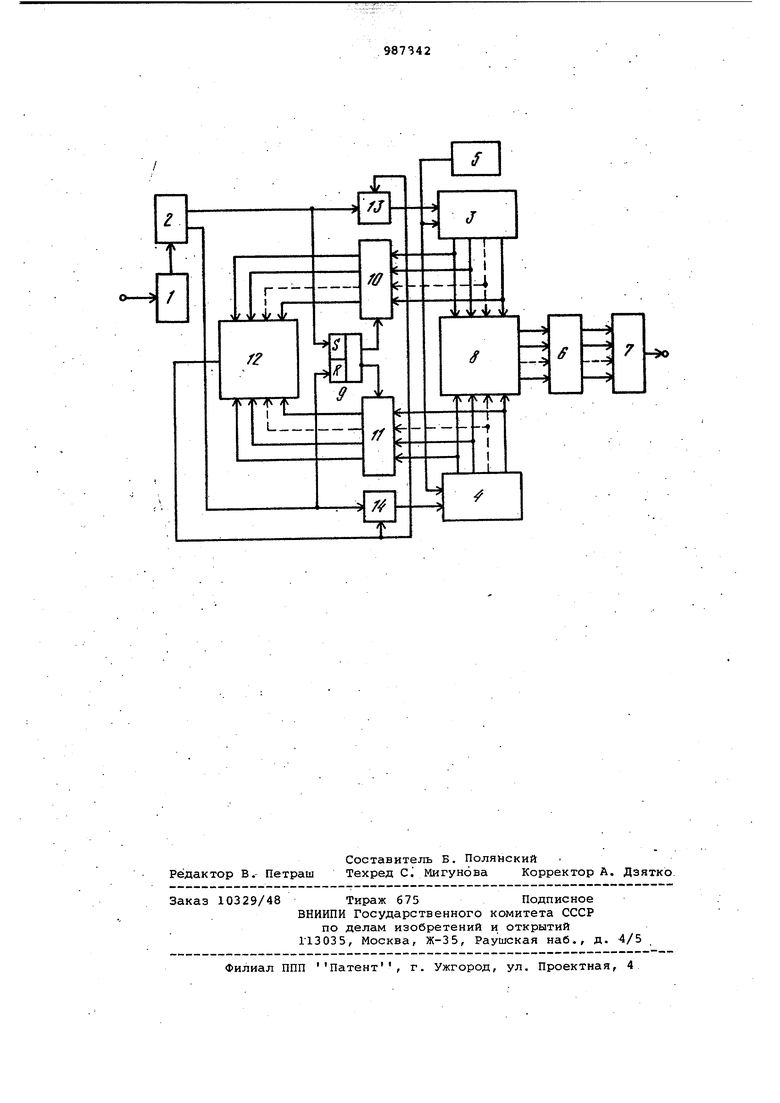

Изобретение относится к радиотех нике и может использоваться в устройствах передачи данных дискретной информации. По основному авт. св. № 815960 известен цифровой демодулятор частотнома Н ип улиров анных сигналов, соде ржащий последовательно соединенные формиЕзователь импульсов и коммутатор, выходы которого подключены к установочным входам делительной частоты, выходы которых соединены с выходом генератора опорной частоты, дешифратор, решающий блок и блок сравнения, выходы которого через дешифратор подключены к входам решающего блока, при этом входы блока сравнения соединены с выходами делителей частоты 1. Однако известный цифровой демодулятор имеет низкую помехоустойчивость Цель изобретения - повышение поме хоустойчивости путем исключения временных искажений. Для достижения поставленной цели известный цифровой демодулятор введе ны два элемента ИЛИ, дополнительный дешифратор, два блока ключей и SS-тр ггер, выходы которого подключены к управляющим входам блоков ключей, вй ходы которых соединены с входами до полнительного дешифратора, выход которого подключен к первым входам элементов ИЛИ, вторые входы которых соединены с выходами коммутатора и соответствуквдими входами PS-триггера/ при этом выходы элементов ИЛИ подключены к установочным входам делителей частоты, выходы которых соединены с сигнальными входами соответствующих блоков ключей. На чертеже представлена структурная электрическая схема предлагаемого цифрового дешифратора. Цифровой демодулятор частотно-манипулированных сигналов содержит формирователь 1 импульсов, коммутатор 2, первый и второй делители частоты 3 и 4 соответственно, генератор 5 опорной частоты, дешифратор 6, решающий блок 7, блок 8 сравнения, RS-триггер 9, первый. 10 и второй 11 блоки ключей, дополнительный дешифратор 12, первый 13 и второй 14 элементы ИЛИ. Демодулятор работает следующим образом. Частотно-манипулированный сигнал поступает на формирователь 1 импульсов, в котором формируются импульсы сброса по переходам входного сигнала через нуль..Коммутатор 2 осуществляет поочередно подачу импульсов сброса на установочные входы идентичных делителей Зй 4 частоты через элементы ИЛИ 13 и 14 и входы RS-триггера 9. Делители 3 и 4 частоты осуществляют деление частоты сигнала генератора 5 опорной частоты. При отсутствии имПульсов сброса делители 3 и 4 часто ты синхронноделят частоту сигнала ге нератора 5 опорной частоты и на выхо} дах разрядов делителей 3 и 4 частоты происходит синхронная смена разрядов числа. Блок 8 сравнения, например арифметическое устройство, осуществляет вычисление разности между числами. Нулевой результат сравнения посту пает в дешифратор б. При поступлении импульсов сброса с коммутатора 2 между числами на выходе счетчиковых делителей 3 и 4 час тоты за счет воздействия импульсов сброса устанавливается определенная разность, которая вычисляется в блоке . В сравнения и дешифрируется в програ мируемом дешифраторе б,а с помощью р шакедего блока 7 представляется в виде -значений разрядов принимаемой ком бинации. При постоянстве частоты на входе . Демодулятора сохраняется, постоянная разница между числами на выходах раз рядов счетчиковых делителей 3 и 4 частоты, а сами числа изменяются тол ко до определённого числа N, так как существует постоянная установка делителей 3 и 4 частоты в нулевое состояние. За счет поочередной подачи импуль сов сброса от коммутатора 2 на S- и S- входы HS-триггера 9 дополнительны дешифратор 12 поочередно подключается через соответствующий блок 10 или 11 ключей (в зависимости от состояни RS-триггера 9) к делителю частоты, установленному в нулевое состояние. Дешифруется дополнительным дешифрато ром число, на единицу большее предел ного числа для разрядов делителей 3 и 4 частотьз, т.е. состояние N+1 соот ветствующего делителя частоты. За счет этого и описанных выше переклю. чений дополнительного дешифратора 12 при наличии сигнала на входе демодулятора установка в нуль делителей 3 и 4 частоты производится только по импульсам от коммутатора 2. При окончании сигнала на входе оде мрдулятора числа на выходах разрядов делителей 3 и 4 частоты могут становиться больше N, но уже при числе N+1 на выходе.разрядов одного из делителей частоты дополнительным дешифратором 12 формируется импульс на его выходе, который через оба элемента ИЛИ 13 и 14 устанавливает оба делителя частоты в нулевое состояние, тем самым обеспечивая своевременное окончание формирования последнего разЬяда комбинации, завершакадий процесс передачи информации, и дальнейшую синхронную работу делителей 3 и 4 частоты. Таким образом, использование изобретения позволяет исключить временные искажения посылок последних разрядов комбинаций, завершакицих процесс передачи информации. Введенная принудительная установка цифрового демодулятора в исходное состояние увеличивает и помехоустойчивость, так как в этом случае искажения края посылки (отсутствие формирования импульса сброса на краю посылки) будут исправлены, за сЧет формирования его введенными узлами. Кроме того, расширяются функциональные возможности цифрового демодулятора, так как он обеспечивает безыскаженную работу в стартстопном и синхронном режимах передачи информации и не требует специальных устройств или оперативного вмешательства в процесс приема информации на этапе окончания приема. Формула изобретения Цифровой демодулятор частотно-манипулированных сигналов по авт. св. № 815960, .отличающийся тем, что,, с целью повышенияего помехоустойчивостипутем исключения временных искажений, в него введены два элемента ИЛИ, дополнительный дешифратор, два блока ключей и BS-триггер, выходы которого подключены к управляющим входам блоков ключей, выходы которых соединены с входами дополнительного дешифратора, выход которого подключен к первым входам элементов ИЛИ, вторые входы которых соединены с выходами коммутатора и соответствующими входами -триггера,, при этом выходы элементов ИЛИ подключены к установочным входам делителей частоты, выходы которых соединены с сигнальными входами соответствующих блоков ключей. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 815960, кл. Н 04 L 27/14, 1979 (прототип) .

Авторы

Даты

1983-01-07—Публикация

1981-07-13—Подача