Изобретение относится к вычислительной технике и может быть использовано при построении высоконадежной аппаратуры передачи данных.

Целью изобретения является повышение надежности и расширение области применения устройства за счет возможности использования в системах с контролем по четности или коду Хэмминга.

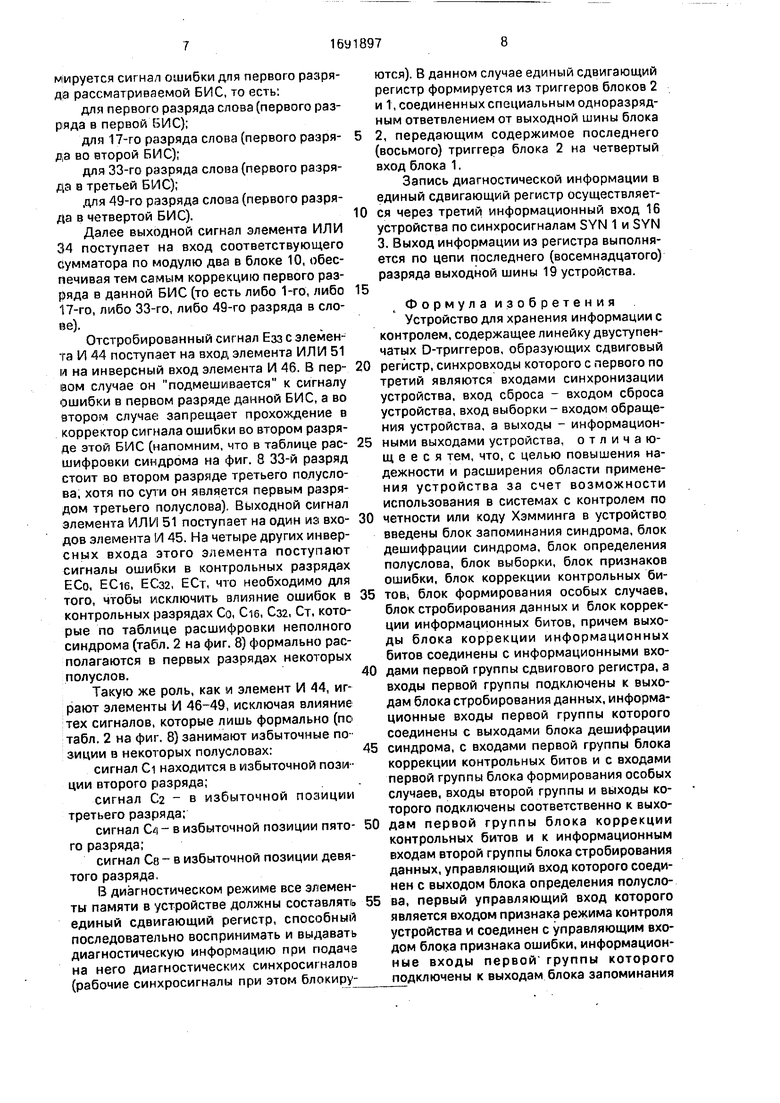

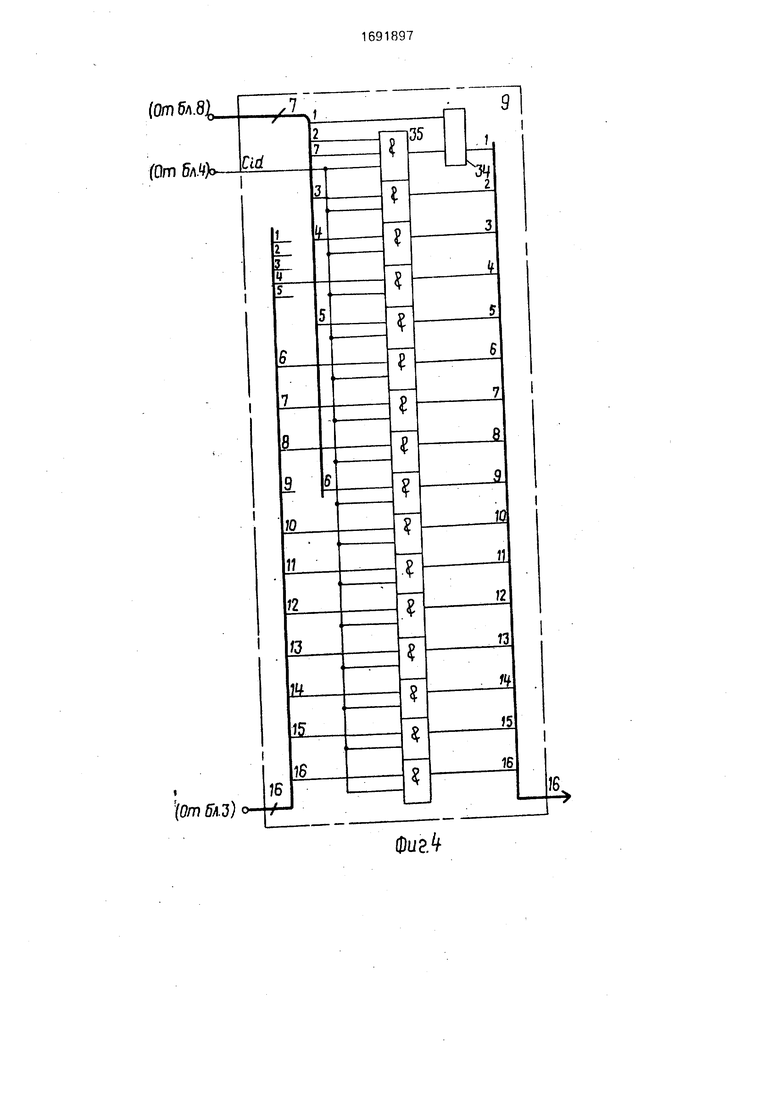

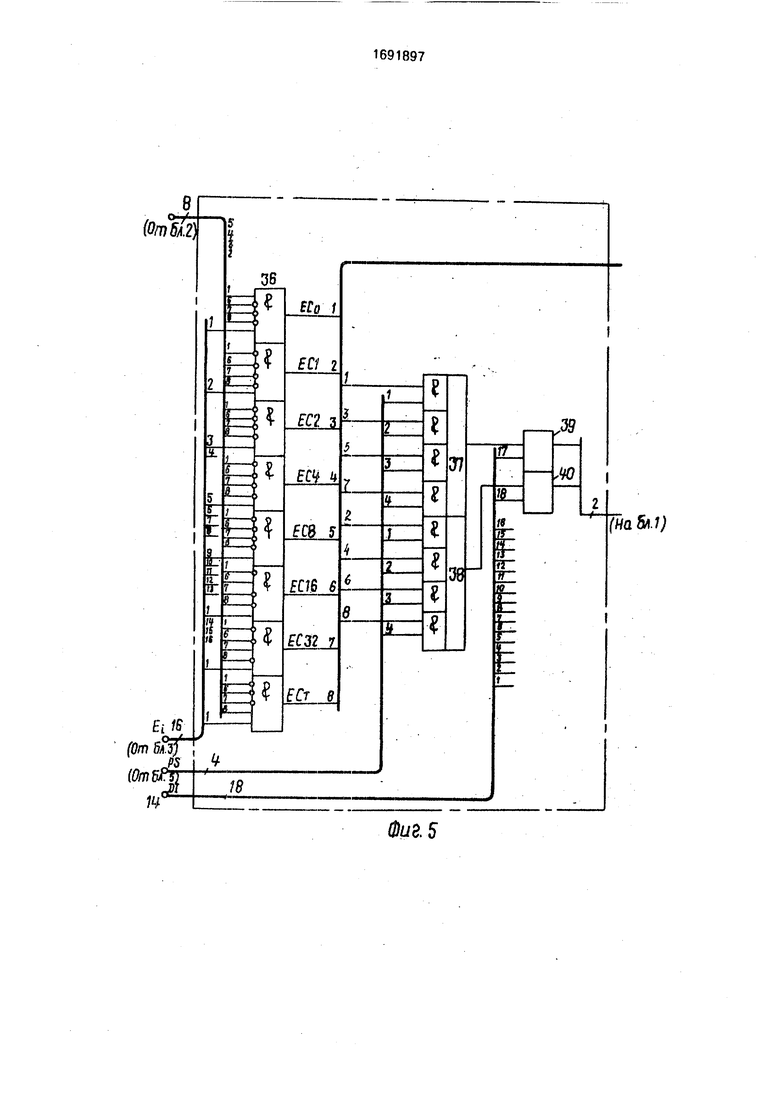

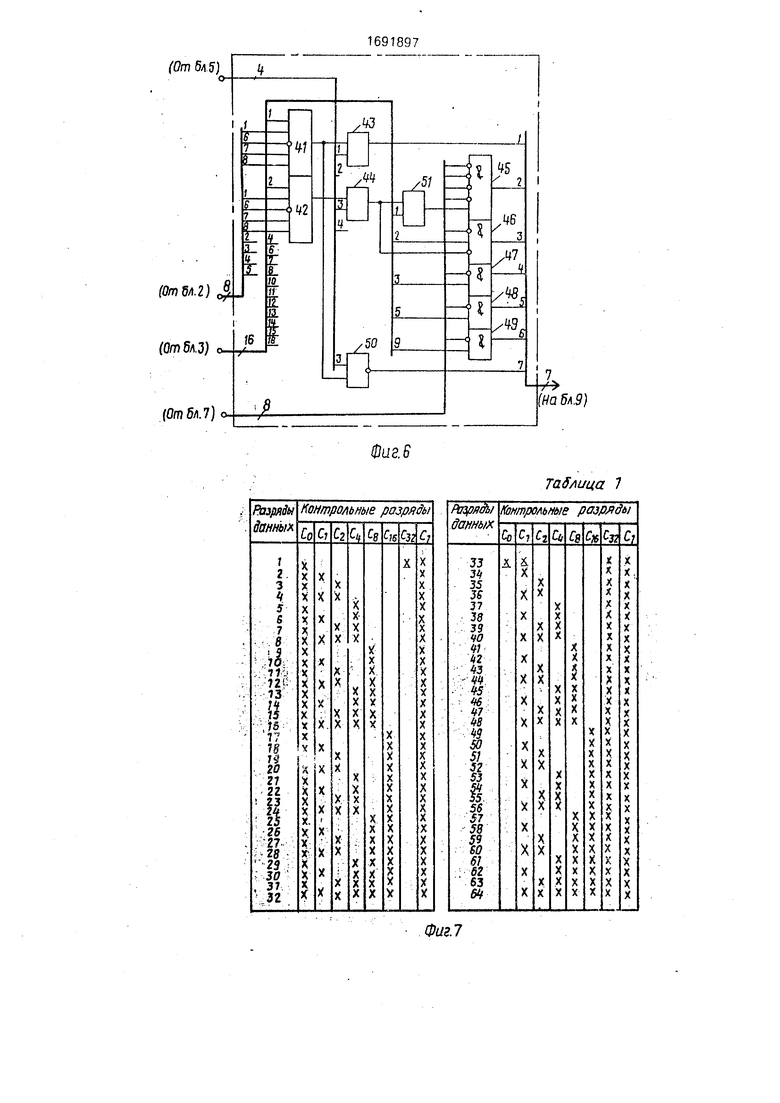

На фиг. 1 изображена структурная схема устройства для передачи информации с контролем; на фиг. 2 - схема блока определения полуслова: на фиг. 3 - схема блока признаков ошибки; на фиг. 4 - схема блока стробирования данных; на фиг. 5 - схема блока коррекции контрольных битов; на фиг. 6 - схема блока формирования особых

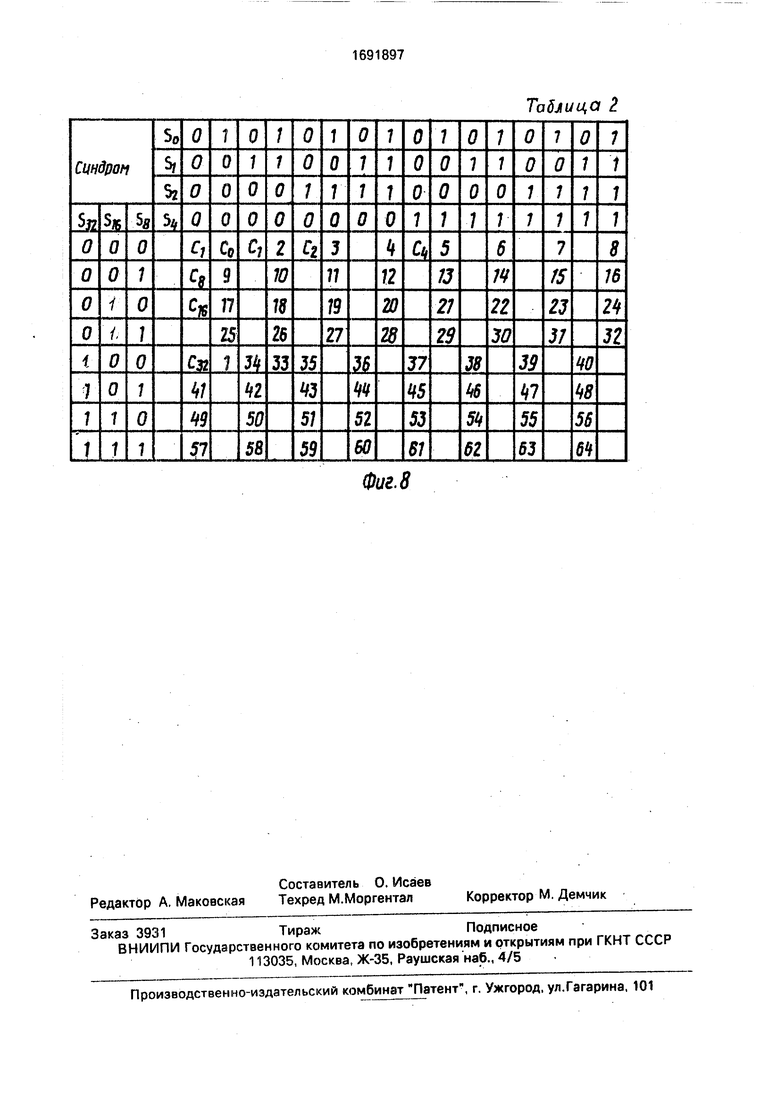

случаев; на фиг. 7 - таблица кодирования 64-разрядных слов; на фиг. 8 - таблица расшифровки синдрома.

Устройство (фиг. 1) содержит линейку двухступенчатых D-триггеров, образующих сдвиговый регистр 1, блок 2 запоминания синдрома, блок 3 дешифрации синдрома, блок 4 определения полуслова, блок 5 выборки, блок 6 признаков ошибки, блок 7 коррекции контрольных битов, блок 8 формирования особых случаев, блок 9 стробирования данных, блок 10 коррекции информационных битов.

На фиг. 1 также обозначены входы 11 синхронизации устройства (SYN), вход 12 сброса устройства (R); вход 13 обращения устройства (Е), информационные входы 14

Os

о

00

о VJ

устройства (D1) входы 15 синдрома устройства (S), диагностический вход 16 устройства (SD), вход 17 режима устройства (М), управляющие входы 18 устройства (L), информационные входы 19 устройства (D), выходы 20-22 признака ошибки устройства (ER 1, ER2, ER).

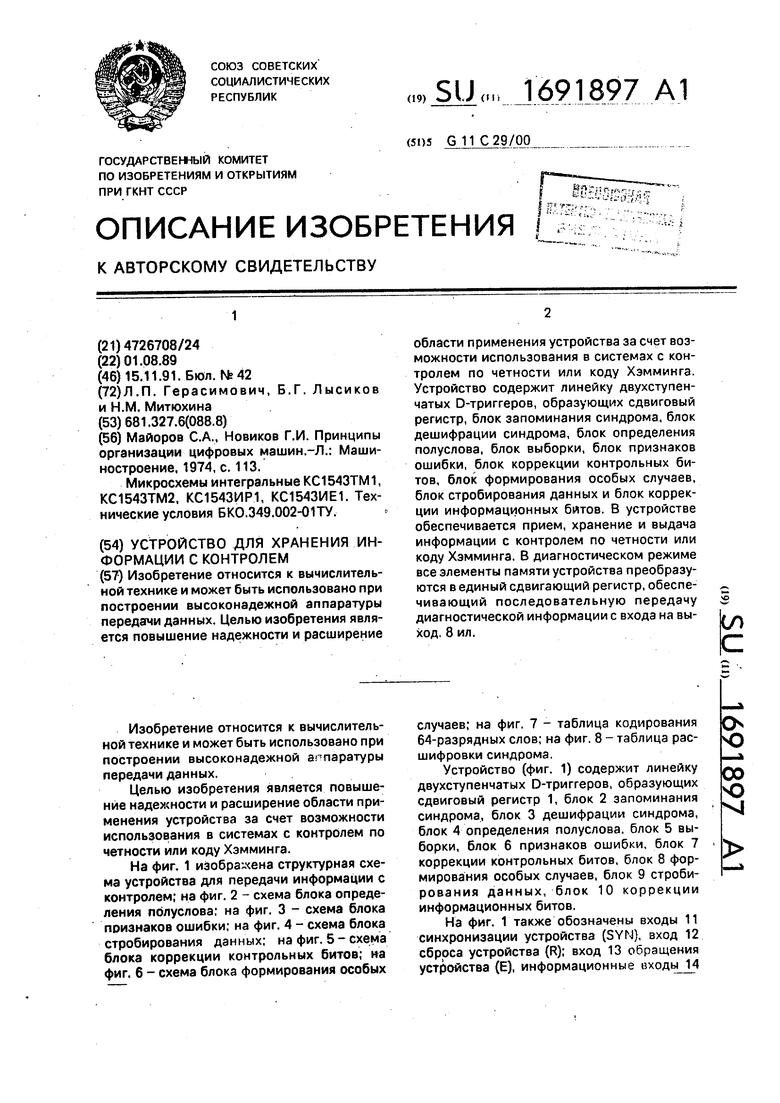

Блок 4 определения полуслова (фиг. 2) содержит сумматоры 23 и 24 по модулю два и элемент И 25.

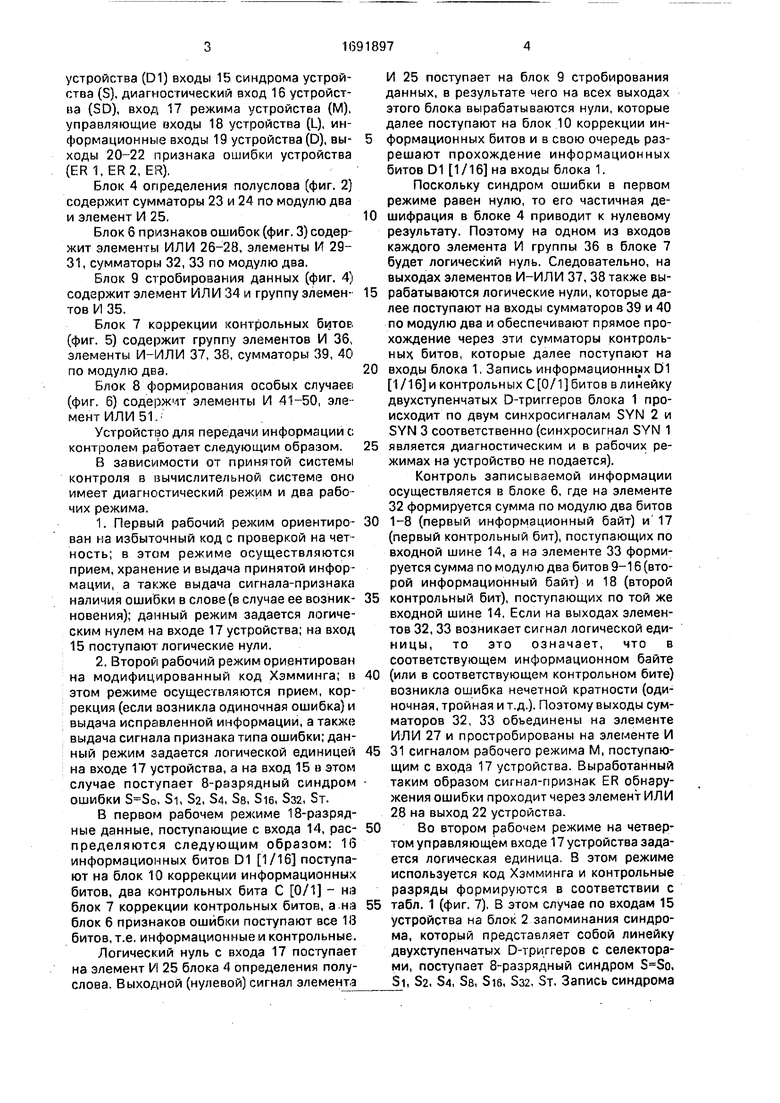

Блок 6 признаков ошибок (фиг. 3) содержит элементы ИЛИ 26-28, элементы И 29- 31, сумматоры 32, 33 по модулю два.

Блок 9 стробирования данных (фиг. 4) содержит элемент ИЛИ 34 и группу элементов И 35.

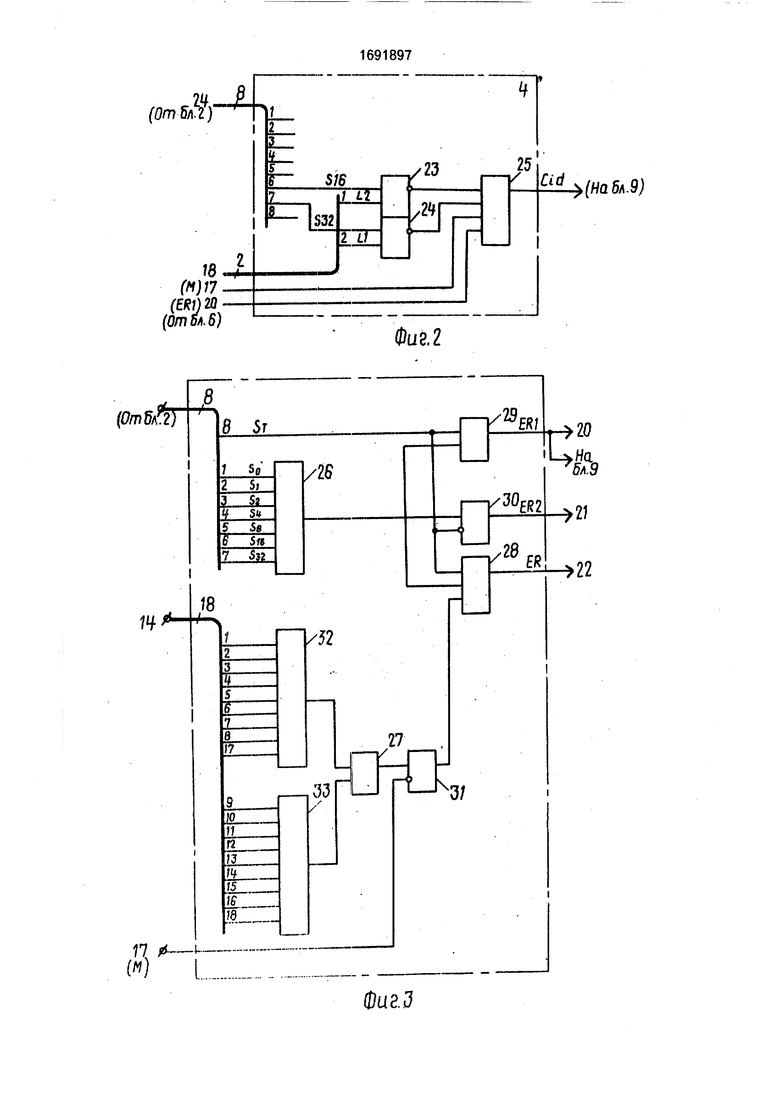

Блок 7 коррекции контрольных битов (фиг. 5) содержит группу элементов И 36, элементы И-ИЛИ 37, 38, сумматоры 39, 40 по модулю два.

Блок 8 формирования особых случаев (фиг, 6) содержит элементы И 41-50, элемент ИЛИ 51.

Устройство для передачи информации с контролем работает следующим образом.

В зависимости от принятой системы контроля в вычислительной системе оно имеет диагностический режим и два рабочих режима,

1.Первый рабочий режим ориентирован на избыточный код с проверкой на четность; в этом режиме осуществляются прием, хранение и выдача принятой информации, а также выдача сигнала-признака наличия ошибки в слове (в случае ее возникновения); данный режим задается логическим нулем на входе 17 устройства; на вход 15 поступают логические нули.

2.Второй рабочий режим ориентирован на модифицированный код Хэмминга; в этом режиме осуществляются прием, коррекция (если возникла одиночная ошибка) и выдача исправленной информации, а также выдача сигнала признака типа ошибки; данный режим задается логической единицей на входе 17 устройства, а на вход 15 в этом случае поступает 8-разрядный синдром ошибки , Si, 82, 84, Se, Sie, 832, ST.

В первом рабочем режиме 18-разрядные данные, поступающие с входа 14, распределяются следующим образом: 16 информационных битов D1 1/16 поступают на блок 10 коррекции информационных битов, два контрольных бита С 0/1 - на блок 7 коррекции контрольных битов, а на блок 6 признаков ошибки поступают все 18 битов, т.е. информационные и контрольные.

Логический нуль с входа 17 поступает на элемент И 25 блока 4 определения полуслова. Выходной (нулевой) сигнал элемента

И 25 поступает на блок 9 стробирования данных, в результате чего на всех выходах этого блока вырабатываются нули, которые далее поступают на блок 10 коррекции информационных битов и в свою очередь разрешают прохождение информационных битов D1 1/16 на входы блока 1.

Поскольку синдром ошибки в первом режиме равен нулю, то его частичная де0 шифрация в блоке 4 приводит к нулевому результату. Поэтому на одном из входов каждого элемента И группы 36 в блоке 7 будет логический нуль. Следовательно, на выходах элементов И-ИЛИ 37, 38 также вы5 рабатываются логические нули, которые далее поступают на входы сумматоров 39 и 40 по модулю два и обеспечивают прямое прохождение через эти сумматоры контрольных битов, которые далее поступают на

0 входы блока 1. Запись информационных D1 1/16 и контрольных С 0/1 битов в линейку двухступенчатых D-триггеров блока 1 происходит по двум синхросигналам SYN 2 и SYN 3 соответственно (синхросигнал SYN 1

5 является диагностическим и в рабочих режимах на устройство не подается).

Контроль записываемой информации осуществляется в блоке 6, где на элементе 32 формируется сумма по модулю два битов

0 1-8 (первый информационный байт) и 17 (первый контрольный бит), поступающих по входной шине 14, а на элементе 33 формируется сумма по модулю два битов 9-16 (второй информационный байт) и 18 (второй

5 контрольный бит), поступающих по той же входной шине 14. Если на выходах элементов 32, 33 возникает сигнал логической единицы, то это означает, что в соответствующем информационном байте

0 (или в соответствующем контрольном бите) возникла ошибка нечетной кратности (одиночная, тройная и т.д.). Поэтому выходы сумматоров 32, 33 объединены на элементе ИЛИ 27 и простробированы на элементе И

5 31 сигналом рабочего режима М, поступающим с входа 17 устройства. Выработанный таким образом сигнал-признак ER обнаружения ошибки проходит через элемент ИЛИ 28 на выход 22 устройства.

0 Во втором рабочем режиме на четвертом управляющем входе 17 устройства задается логическая единица. В этом режиме используется код Хэмминга и контрольные разряды формируются в соответствии с

5 табл. 1 (фиг. 7). В этом случае по входам 15 устройства на блок 2 запоминания синдрома, который представляет собой линейку двухступенчатых D-триггеров с селекторами, поступает 8-разрядный синдром , Si, Sa, SA, SB, Sie. 5з2, ST. Запись синдрома

происходит по двум синхросигналам SYN 2 и SYN 3. С выходов блока 2 биты синдрома Sie и 5з2 поступают на блок 4 определения ошибочного полуслова, на который также поступает 2-разрядный код с входа 18, оп- ределяющий позицию данной БИС. Блок А осуществляет сравнение двух 2-разрядных кодов на сумматорах 23, 24 и вырабатывает сигнал идентификации БИС с ошибочной входной информацией при их равен- стве; при их неравенстве вырабатывается сигнал , что говорит о том, что на данный БИС пришла безошибочная информация (за исключением так называемых особых случаев, о которых говорится не- сколько позже). Сигнал Cld формируется в результате объединения выходов сумматоров 23,24 по И на элементе И 25. При помощи двух других входов элемента И 25 сигнал Cld стробируется сигналом выбора рабоче- го режима М, приходящим на вход 17 устройства, и сигналом-признаком одиночной ошибки ERi, поступающим с первого выхода блока 6 и параллельно подающимся на выход 20 устройства.

Биты синдрома Si, 82, 84 и Ss с выхода блока 2 поступают на блок 3 дешифрации синдрома, где вырабатывается слово ошибки . E2Eie, локализующее ошибочный бит в рабочем полуслове. Весь 8-разрядный синдром , 81, 82, 84, Se, Sie, 832, 8т поступает на блок б признаков ошибки, где определяется тип ошибки по следующим логическим соотношениям:

(SoirSivS2vS4vS8vSi6 /S32)

ERi - сигнал-признак одиночной ошибки;

(SovSivS2vS4vSevS ) ER2 - сигнал-признак двойной ошибки;

ER STvSovSwS2vS4vS8 Si6vS32 ER - сигнал-признак любой обнаруженной ошибки (в том числе многократной).

Сигнал Cld поступает на вход блока 9 стробирования данных и разрешает (или не разрешает) слову ошибки Е пройти с выходов блока 9 на вход блока 1C коррекции информационных битов, где исправление ошибки осуществляется при помощи линейки двувходовых сумматоров по модулю два.

Далее откорректированная информация записывается в блок 1 двухступенчатых D-триггеров с селекторами по двум синхросигналам SYN 2 и SYN 3 соответственно.

Рассмотрим корректировку контрольных битов.

Расшифрованные биты Si, 82, 84, Se Синдрома (слово ошибки Е в рабочем полуслове) с выхода блока 3 поступают на группу элементов И 36 блока .7 коррекции контрольных битов, на которую также поступают биты So, Si6, 832, 8т синдрома (фиг. 5). Элементы И группы 36 фактически яплчются последней ступенью неполного дешифрато ра полного синдрома ошибки So, Si, 82. . Se, Si6, 832, ST, выявляющего ошибку в контрольных разрядах Со. Ci, Са, С4, Cs, Cie. Сзг. Ст в соответствии с табл. 2 на фиг. 8 и формирующего слово ошибки в контрольных разрядах , ECi, EC2, ЕС4, ECs, ECie, ЕСз2, ЕСт. Биты этого слова далее идут на селекторы, состоящие из элементов И-ИЛИ 37, 38. На эти же селекторы с блокз 5 поступают сигналы локализации БИС (PSj) На выход первого селектора может пройти один из сигналов ошибки ECo, ЕСа, ECs, ЕСз2, если данная БИС является первой, второй, третьей или четвертой соответственно. На выход второго селектора может пройти один из сигналов ошибки ECi, EC4. ECi6, ЕСт, если данная БИС является первой, второй, третьей или четвертой БИС соответственно. Далее пара выбранных сигналов ошибки поступает на корректор контрольных битов, состоящий из двух двувходовых сумматоров 39 и 40 по модулю два.

На другие входы этих элементов с входа 14 устройства подаются контрольные биты Со и Ci для первой БИС, С2 и С4 для второй БИС, Сз и Сю для третьей БИС, Сз2 и Ст для четвертой БИС, Откорректированная пара контрольных битов далее подается для хранения на блок 1.

Два разряда информации - 1 и 33-й (табл. 1) носят статус особых разрядов, так как они нарушают регулярность формирования контрольных битов. При работе с 64- разрядным словом возникает необходимость формирования сигналов ошибки для этих разрядов отдельно. Так, 1-й разряд в табл. 1 расшифровки синдромов находится на месте первого разряда, но не в своем, первом полуслове, а в третьем (табл. 2). Аналогичное положение с 33-м разрядом: в таблице расшифровки синдромов он находится в своем (третьем) полуслове, но не в первом, а во втором разряде. Следовательно, возникает необходимость выполнить полную дешифрацию полного синдрома для этих двух разрядов, Такая дешифрация выполняется в блоке 8 при помощи элементов И 41 и 42, вырабатывающих сигналы ошибки EI и Езз (фиг. б). Далее сигналы EI и Езз стробируются на элементах И 43,44 сигналами локализации БИС, поступающими с блока 5:

Отстробированный сигнал EI далее поступает на первый разряд 7-разрядной выходной шины блока 8, по которой поступает на элемент ИЛИ 34 блока 9 (фиг. л. В результате этого на выходе элемента ИЛИ 34 формируется сигнал ошибки для первого разряда рассматриваемой БИС, то есть:

для первого разряда слова (первого разряда в первой БИС);

для 17-го разряда слова (первого разряда во второй БИС);

для 33-го разряда слова (первого разряда в третьей БИС);

для 49-го разряда слова (первого разряда в четвертой БИС).

Далее выходной сигнал элемента ИЛИ 34 поступает на вход соответствующего сумматора по модулю два в блоке 10, обеспечивая тем самым коррекцию первого разряда в данной БИС (то есть либо 1-го, либо 17-го, либо 33-го, либо 49-го разряда в слове).

Отстробированный сигнал Езз с элемента И 44 поступает на вход элемента ИЛИ 51 и на инверсный вход элемента И 46. В первом случае он подмешивается к сигналу ошибки в первом разряде данной БИС, а во втором случае запрещает прохождение в корректор сигнала ошибки во втором разряде этой БИС (напомним, что в таблице расшифровки синдрома на фиг. 8 33-й разряд стоит во втором разряде третьего полуслова, хотя по сути он является первым разрядом третьего полуслова). Выходной сигнал элемента ИЛИ 51 поступает на один из входов элемента И 45. На четыре других инверсных входа этого элемента поступают сигналы ошибки в контрольных разрядах ECo, ECi6, ЕСз2, ЕСт, что необходимо для того, чтобы исключить влияние ошибок в контрольных разрядах Со, Cie, Сз2, Ст, которые по таблице расшифровки неполного синдрома (табл. 2 на фиг. 8) формально располагаются в первых разрядах некоторых полуслов.

Такую же роль, как и элемент И 44, играют элементы И 46-49, исключая влияние тех сигналов, которые лишь формально (по табл. 2 на фиг. 8) занимают избыточные позиции в некоторых полусловах:

сигнал Ci находится в избыточной позиции второго разряда;

сигнал С2 в избыточной позиции третьего разряда;

сигнал С4 - в избыточной позиции пятого разряда;

сигнал Се - в избыточной позиции девятого разряда.

В диагностическом режиме все элементы памяти в устройстве должны составлять единый сдвигающий регистр, способный последовательно воспринимать и выдавать диагностическую информацию при подаче на него диагностических синхросигналов (рабочие синхросигналы при этом блокируются). В данном случае единый сдвигающий регистр формируется из триггеров блоков 2 и 1, соединенных специальным одноразрядным ответвлением от выходной шины блока

2, передающим содержимое последнего (восьмого) триггера блока 2 на четвертый вход блока 1.

Запись диагностической информации в единый сдвигающий регистр осуществляет0 ся через третий информационный вход 16 устройства по синхросигналам SYN 1 и SYN 3. Выход информации из регистра выполняется по цепи последнего (восемнадцатого) разряда выходной шины 19 устройства.

5

Формула изобретения Устройство для хранения информации с контролем, содержащее линейку двуступен- чатых D-триггеров, образующих сдвиговый

0 регистр, синхровходы которого с первого по третий являются входами синхронизации устройства, вход сброса - входом сброса устройства, вход выборки - входом обращения устройства, а выходы - информацион5 ными выходами устройства, отличающееся тем, что, с целью повышения надежности и расширения области применения устройства за счет возможности использования в системах с контролем по

0 четности или коду Хэмминга в устройство введены блок запоминания синдрома, блок дешифрации синдрома, блок определения полуслова, блок выборки, блок признаков ошибки, блок коррекции контрольных би5 тов, блок формирования особых случаев, блок стробирования данных и блок коррекции информационных битов, причем выходы блока коррекции информационных битов соединены с информационными вхо0 дами первой группы сдвигового регистра, а входы первой группы подключены к выходам блока стробирования данных, информационные входы первой группы которого соединены с выходами блока дешифрации

5 синдрома, с входами первой группы блока коррекции контрольных битов и с входами первой группы блока формирования особых случаев, входы второй группы и выходы которого подключены соответственно к выхо0 дам первой группы блока коррекции контрольных битов и к информационным входам второй группы блока стробирования данных, управляющий вход которого соединен с выходом блока определения полусло5 ва, первый управляющий вход которого является входом признака режима контроля устройства и соединен с управляющим входом блока признака ошибки, информационные входы первой группы которого подключены к выходам блока запоминания

синдрома, синхровходы которого с первого по третий, а также входы выборки и сброса соединены с одноименными входами устройства, входы блока дешифрации синдрома, информационные входы первой группы блока определения полуслова, входы второй группы блока коррекции контрольных битов и входы третьей группы блока формирования особых случаев подключены к соответствующим выходам блока запоминания синдрома, информационные входы группы и информационный вход которого являются соответственно входами синдрома и диагностическим входом устройства, информационные входы второй группы блока определения полуслова являются управляющими входами устройства и соединены с входами блока выборки и с входами четвертой группы блока формирования особых случаев, информационные входы второй группы блока признака ошибки являются информационными входами устройства и

соединены с входами второй группы блока коррекции информационных битов, информационные входы третьей группы блока признака ошибки являются входами разрядов байтной четности устройства и подключены к входам третьей группы блока коррекции контрольных битов, входы четвертой группы которого соединены с выходами блока выборки, первый выход блока

признака ошибки подключен к второму управляющему входу блока определения полуслова и является первым выходом признака ошибки устройства, второй и третий выходы блока признака ошибки являются соответственно вторым и третьим выходами признака ошибки устройства, выходы второй группы блока коррекции контрольных битов подключены к информационным входам второй группы сдвигового регистра, один

выход блока запоминания синдрома соединен с последовательным информационным входом сдвигового регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1984 |

|

SU1249589A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Устройство для контроля и коррекции информации | 1980 |

|

SU940160A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Устройство для коррекции микрокоманд | 1984 |

|

SU1164709A1 |

| Устройство для обнаружения и коррекции ошибок | 1990 |

|

SU1783583A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| Устройство для контроля цифровых данных | 1985 |

|

SU1381718A1 |

| Запоминающее устройство | 1987 |

|

SU1481865A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высоконадежной аппаратуры передачи данных. Целью изобретения является повышение надежности и расширение области применения устройства за счет возможности использования в системах с контролем по четности или коду Хэмминга. Устройство содержит линейку двухступенчатых D-триггеров, образующих сдвиговый регистр, блок запоминания синдрома, блок дешифрации синдрома, блок определения полуслова, блок выборки, блок признаков ошибки, блок коррекции контрольных битов, блок формирования особых случаев, блок стробирования данных и блок коррекции информационных битов. В устройстве обеспечивается прием, хранение и выдача информации с контролем по четности или коду Хэмминга. В диагностическом режиме все элементы памяти устройства преобразуются в единый сдвигающий регистр, обеспе- чивающий последовательную передачу диагностической информации с входа на выход. 8 ил. СО с

Фиг.1

(От D/I.

W

(ft) 17 (EK1JMfa. 6)

(От

-(На6л.9)

Фиг. 2

фигЗ

(Огл5л.8 (От &vtyx

0m Ш)

Фиг

Фиг. 5

(От 5л 5)

(Отвлг) А

(ОтБлЗ) о(Отбл.7)

Ь

(НаблЭ)

Фиг.6

Тайлица 7

Таблица 2.

Фиг. 8

| Майоров С.А., Новиков Г.И | |||

| Принципы организации цифровых машин.-/.: Машиностроение, 1974, с | |||

| Способ обработки грубых шерстей на различных аппаратах для мериносовой шерсти | 1920 |

|

SU113A1 |

| Насос для откачивания жидкости из буровых скважин | 1923 |

|

SU1543A1 |

| Насос для откачивания жидкости из буровых скважин | 1923 |

|

SU1543A1 |

| Способ составления поездов | 1924 |

|

SU349A1 |

Авторы

Даты

1991-11-15—Публикация

1989-08-01—Подача