Изобретение относится к автомати ке и вычислительной технике и может быть использовано в арифметических устройствах, выполненных на базе мно оустойчивых элементов с фазоимпульсным представлением информаци в частности для умножения последова TeiibHocTH импульсов на множитель о О до 1. / Известно устройство для деления частоты с регулируемым коэффициентом деления, состоящее из частотно-импульсного вычитателя, счетчика, схемы сравнения, двух десятичных счетчиков , управляемых формирователей и схемы ИЛИ l3 . . Недостатком устройства является малый диапазон .изменения мнозйителя (1-0,1) и значительное возрастание объема оборудования и сложности построения схемы устройства при числе декад больше двух. Известен также перемножитель чис ла импульсов, содержащий счетнце степени, каждая из которых соответствует одному из положений запятой в Множителе, Каждая счетная ступень имеет один счетный выход и выход переноса. Счетные выходы и вход самой младшей счетной декады соединяются со входом селектора, который в зависимости от управляющего слова, соответствующего множителю, периодически при последовательном подключении ч-i счетных ступеней кодирующим устройством, соединенным с выходами, переноса, пропускают определенную часть входящих импульсов 2. Недостатком устройства является значительное увеличение объема оборудования при изменении коэффициента умножения более мелкими градациями. Наиболее близким по технической сущности является множительное устройство, содержащее сумматор и ячейки умножения в виде соединенных между собой счетчика импульсов, дешифратора с коммутатором, триггера управления и выходного Элемента И. Количество ячеек в множительном устройстве пропорционально числу значащих десятичных цифр коэффициента умножения. Дешифратор с коммутаторами реализует выделение nj-oro импульса из каждых десяти импульсов последовательности N . С момента появления 1-ого импульса входной последовательности N, определяющего rianajio процесса умножения на сумматор с элемента И начинают поступать первые импульсы, п, имПульс проходит через дешифратор на вход триггера и переводит его в состояние, соответствующее закрытию элемента И. Поступление импульсов на сумматор через вентиль прекращается. Десятый импульс приходит на выход счетчика, поступает на триггер и переводит его в состояние, соответствующее открытию элемента И. За каждый цикл на сумматор с вентиля проходит п импульсов.

Таким образом, первая ячейка выдает 0,1- п N импульсов.

Вторая ячейка начинает работать с момента прохождения каждого десятого импульса последовательности N. Работает аналогично первой ячейке и осуществляет выделение п, импульсов из каждых десяти импульсов последовательности 0,1- N 3j .

Недостатком устройства является большой объем оборудования.при большой разрядности множителя, что обусловливается использованием для каждой ячейки умножения дешифратора с коммутаторами.

Цель изобретения - сокращение оборудования.

Поставленная цель -достигается тем что в множительное устройство, содержсццее сумматор и ячейки умножения каждая из которых содержит выходной элемент И, триггер и счетчик, первый счетный вход которого соединен с первым входом выходного элемента И, второй вход которого соединен с выходом триггера той же ячейки умножения, выходы выходных элементов И всех ячеек .умножения соединены со входами сумматора, первый счетный вход счетчика первой ячейки умножения подключен к информационному входу устройства, выход счетчика каждой ячейки множения подключен к первому счетному входу счетчика последующей ячейки умножения, введен распределительный блок, а в каждую ячейку умножения - первый и второ1% элемен, ты И, первые входы которых соединены с выходом счетчика той же ячейки умножения, выход первого элемента И соединен со входом установки в 1 триггера той же ячейки умножения, выход второго элемента И соединен со входом установки в О того же триггера, вход распределительного блока соединен со вторым счетным входом счетчика каждой ячейки умножения и с входом опорной частоты устройства, нулевой выход распределительного блока соединен со вторым входом второго элемента И каждой умножения, второй вход первого элемента И каждой ячейки умножения подключен к выходу распределительного блока.

соответствующему цифре данного рачряда множителя.

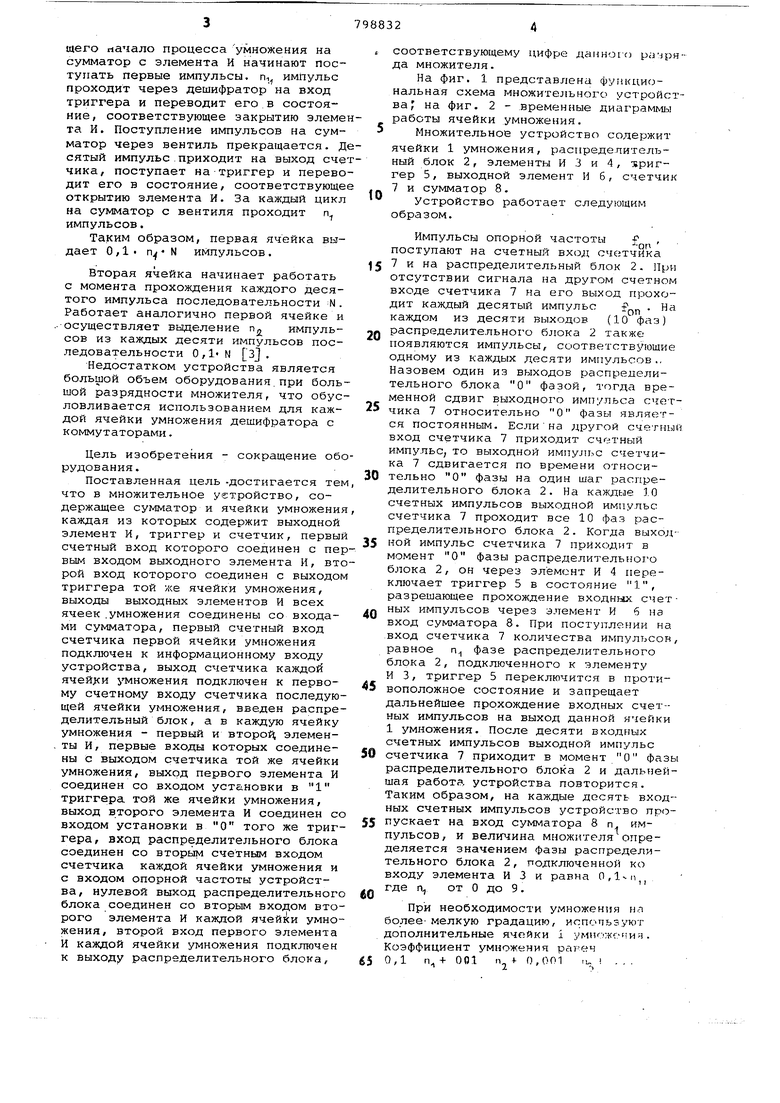

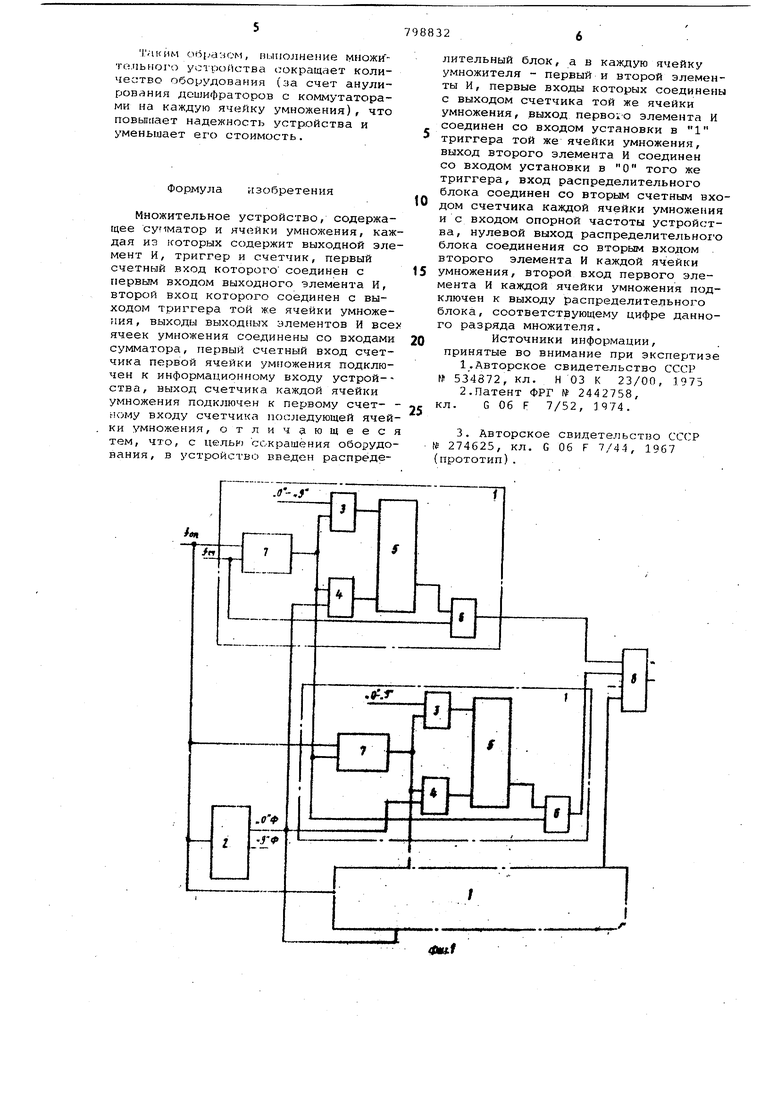

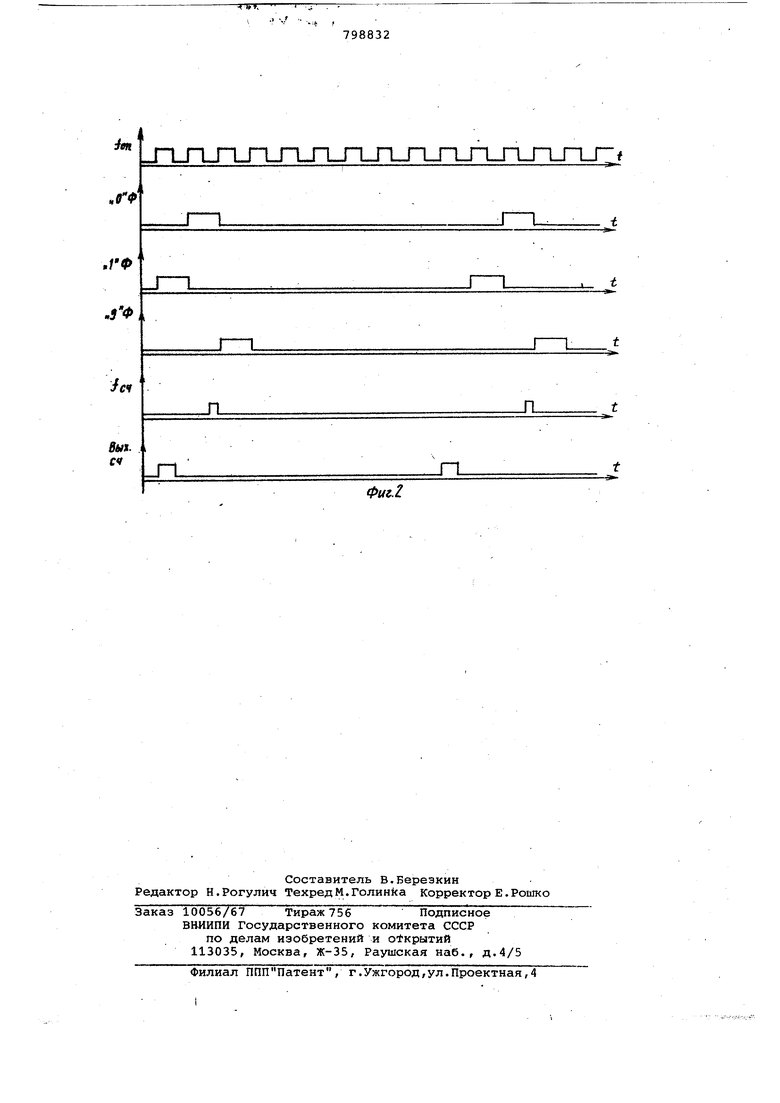

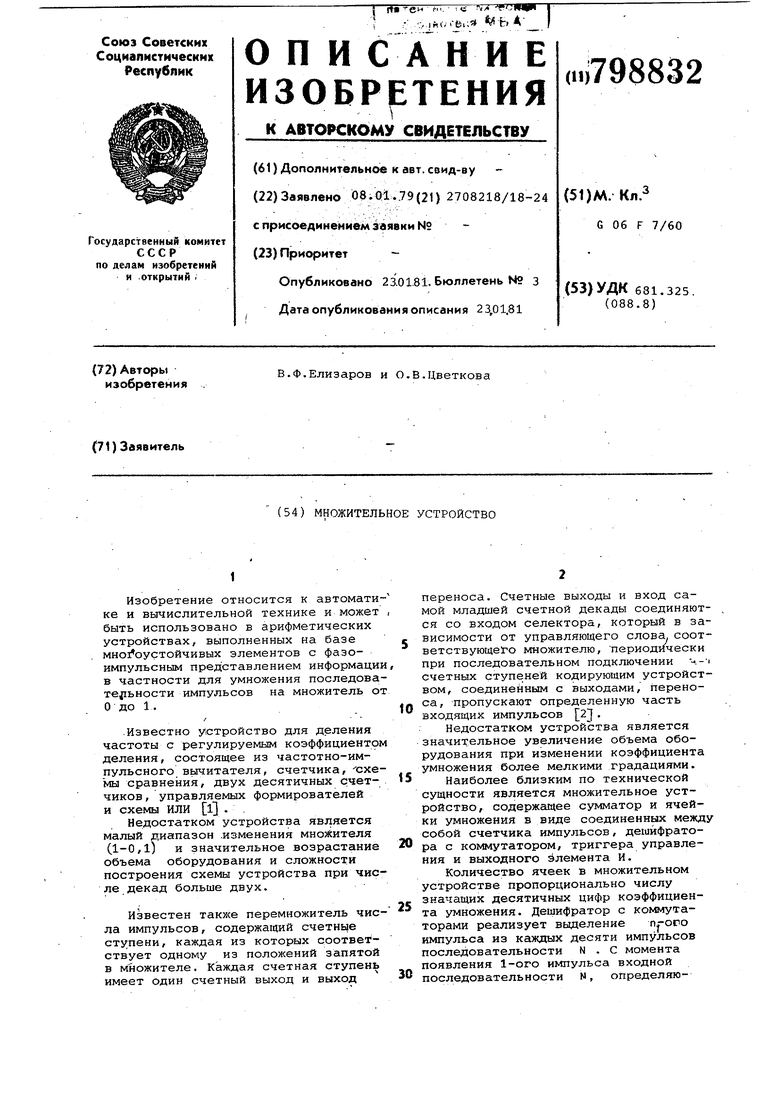

На фиг. 1 представлена функциональная схема множительного устройства; на фиг. 2 - .временные диаграмм.-) работы ячейки умножения.

Множительное устройство содержит ячейки 1 умножения, распределительный блок 2, элементы И 3 и 4, -вриггер 5, выходной э.пемент И 6, счетчик 7 и сумматор 8.

Устройство работает следующим образом.

Импульсы опорной частоты , поступают на счетный вход счегтчика 7 и на распределительный блок 2. При отсутствии сигнала на другом счетном входе счетчика 7 на его выход проходит каждый десятый импульс f . На каждом из десяти выходов (10 фаз) распределительного блока 2 также появляются импульсы, соответств ющие одному из каждых десяти импульсов., Назовем один из выходов распределительного блока О фазой, то.гда временной сдвиг выходного импульса счетчика 7 относительно О фазы является постоянным. Еслина другой счетный вход счетчика 7 приходит счетный импульс, то выходной импульс счетчика 7 сдвигается по времени относительно О фазы на один шаг распределительного блока 2. На каждьле 10 счетных импульсов выходной импульс счетчика 7 проходит все 10 фаз распределительного блока 2. Когда выхолг ной импульс счетчика 7 приходит в момент О фазы распределительного блока 2, он через элемент И 4 переключает триггер 5 в состояние 1, разрешающее прохождение входных счетных импульсов через элемент И б на вход сумматора 8. При поступлении на -ВХОД счетчика 7 количества импульсов, равное п., фазе распределительного блока 2, подключенного к элементу И 3, триггер 5 переключится в противоположное состояние и запрещает дальнейшее прохождение входных счетных импульсов на выход данной ячейки 1 умножения. После десяти входных счетных импульсов выходной импульс счетчика 7 приходит в момент О фазы распределительного блока 2 и дальнейшая работа устройства повторится. Таким образом, на каждые десять входных счетных импульсов устройство пропускает на вход сумматора 8 п. импульсов, и величина множителя определяется значением Фазы распределительного блока 2, подключенной ко входу элемента И 3 и равна 0,1-. где п, от О до 9.

При необходимости умножения нл более- мелкую градацию, испопьзуют дополнительные ячейки i умиожеиия. Коэффициент умножения рареч 0,1 п + 001 n,j - 0,001 ,1„ i ...

1аким oi5.d,JCM, выполнение множительного устройства сокращает количество оборудования (за счет анулирования дешифраторов с коммутаторами на каждую ячейку умножения), что повьлнает надежность устройства и уменьшает его стоимость.

Формула изобретения

Множительное устройство, содержащее супматор и ячейки умножения, каждая из которых содержит выходной элемент И, триггер и счетчик, первый счетный вход которого соединен с первым входом выходного элемента И, второй вхоц которого соединен с выходом триггера той же ячейки умножеяия, выход : ВЫХОДЕ1ЫХ элементов И всех ячеек умножения соединены со входами сумматора, первый счетный вход счетчика первой ячейки умножения подключен к информационному входу устрой-ства, выход счетчика каждой ячейки умножения подключен к первому счет- ному входу счетчика 1кх::ледующей ячейки умножения, отличающееся тем, что, с цельн) сокрашения оборудования, в устройство введен распределительный блок, а в каждую ячейку умножителя - первый и второй элементы И, первые входы которых соединены с выходом счетчика той же ячейки умножения, выход nepBOio элемента И соединен со входом установки в 1 триггера той же ячейки умножения, выход второго элемента И соединен со входом установки в О того же триггера, вход распределительного блока соединен со вторым счетньпи вхо0дом счетчика каждой ячейки умножения и с входом опорной частоты устройства, нулевой выход распределительного блока соединения со вторым входом второго элемента И каждой ячейки

5 умножения, второй вход первого элемента И каждой ячейки умножения подключен к выходу распределительного блока, соответствующему цифре данного разряда множителя.

Источники информации,

0 принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 534872, кл. Н 03 К 23/00, 1975

2.Патент ФРГ № 2442758, кл. G 06 F 7/52, 974.

5

3. Авторское свидетельство СССР № 274625, кл. G 06 F 7/44, 1967 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения симметричных составляющих напряжений трехфазной сети | 1990 |

|

SU1781642A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Специализированный процессор | 1981 |

|

SU1023339A1 |

| Устройство для определения вероятностного состояния дискретной системы | 1983 |

|

SU1164729A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Однородный спектро-коррелометр | 1981 |

|

SU970382A1 |

| Вычислительное устройство | 1980 |

|

SU1001090A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1982 |

|

SU1101835A1 |

.cV

-ГЧ

Гь

-

.1Ф ЗФ

JC4

П

Вых. сч

П

798832

п

Авторы

Даты

1981-01-23—Публикация

1979-01-08—Подача