Фиг. 1

Изобретение относится к вычисли- тельной технике и может быть использовано для решения задач обнаружения и определения направления на источ- ник излучения сигналов.

Цель изобретения - расширение функциональных возможностей устройства путем получения сигналов по лучам диаграммы направленности антен- кой решетки, на выходах приемников кот.орой формируются сигналы звукового давления и,градиента давления по трем ортогональным координатам,

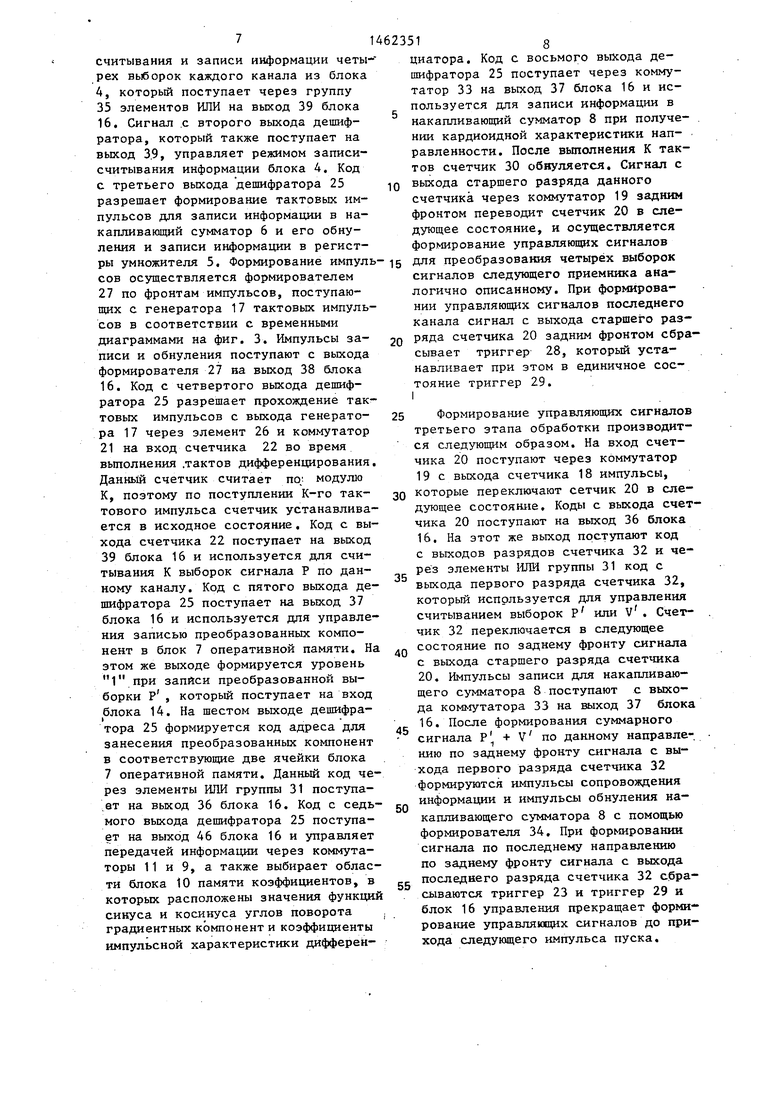

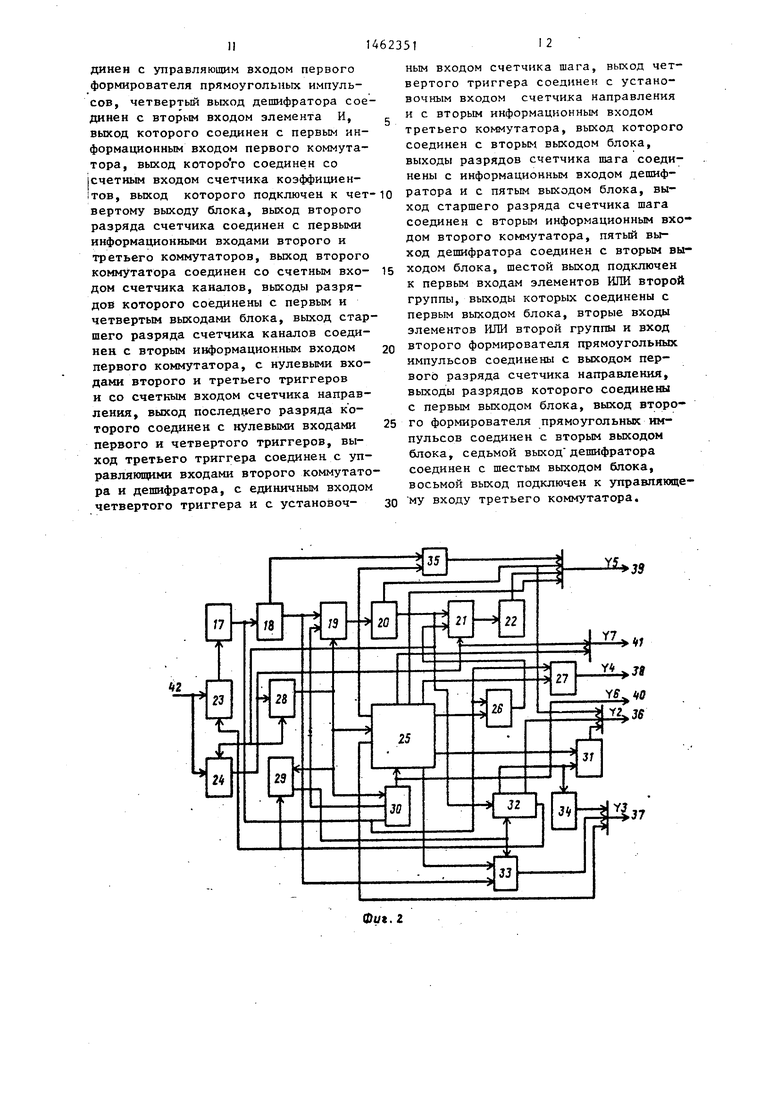

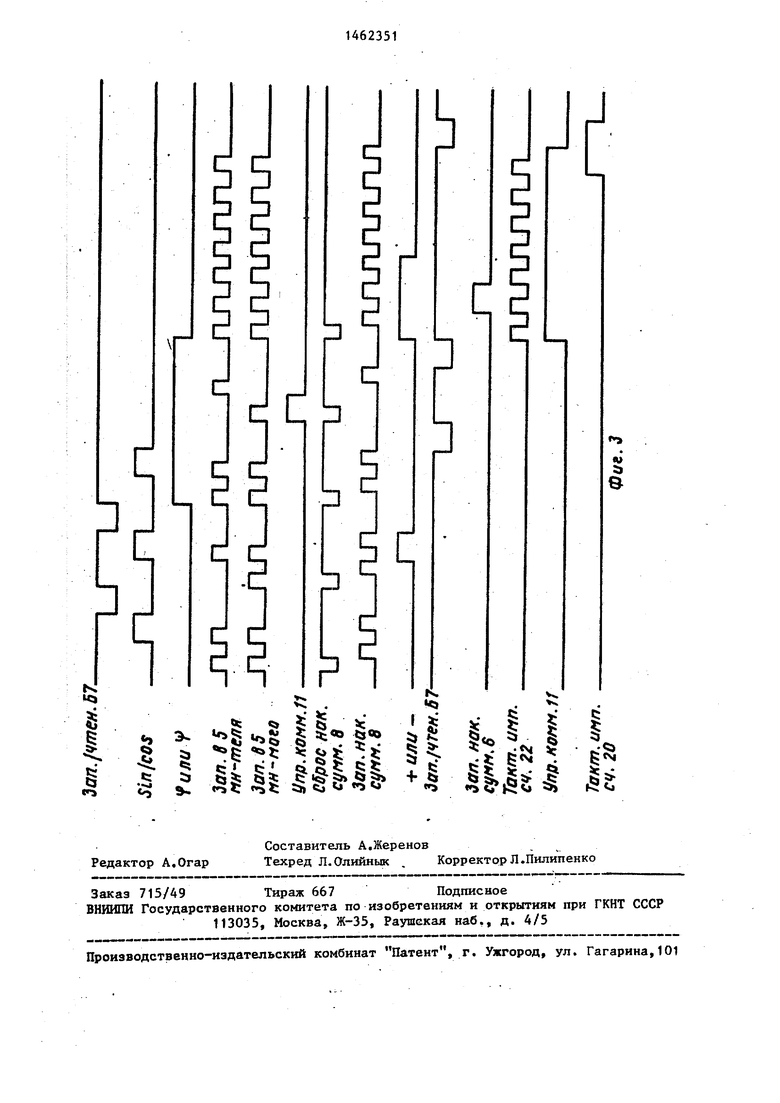

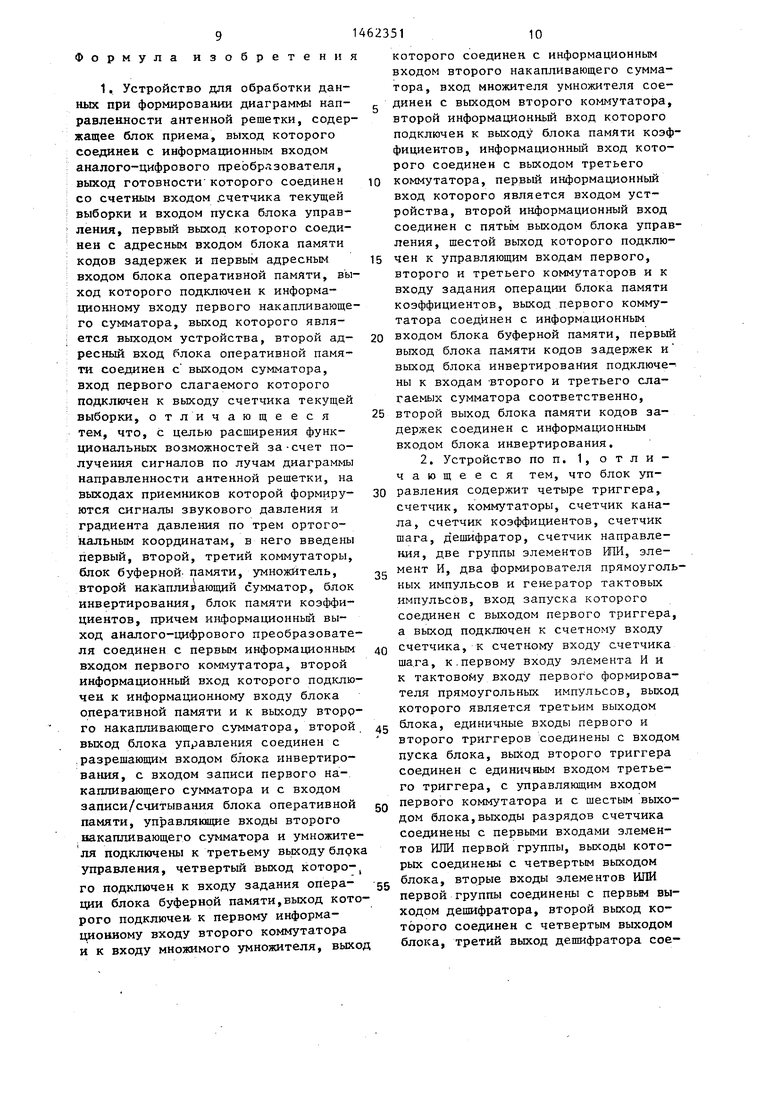

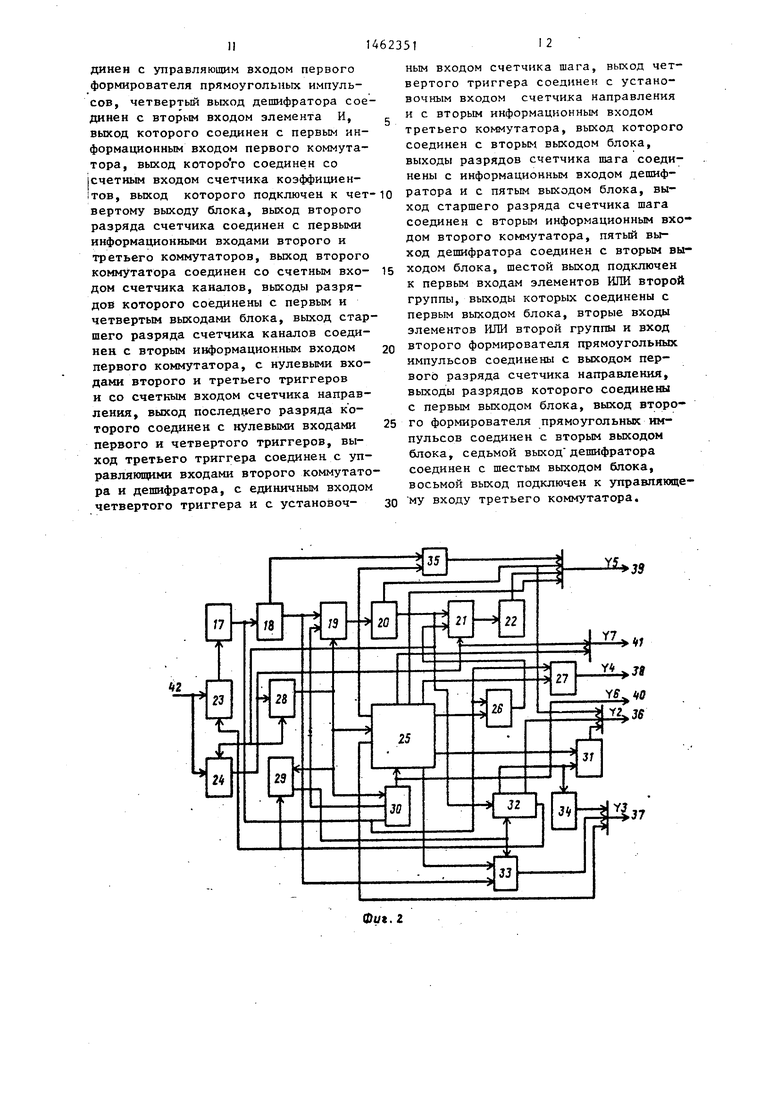

На фиг. 1 представлена схема уст ройства-, на фиг. 2 - схема блока управления; на фиг. 3 - временные ди- аграммы работы.

Устройство содержит блок 1 приема, аналого-цифровой преобразовател (АЦП) 2, коммутатор 3, блок 4 буферной памяти, умножитель 5, накапливающий сумматор 6, блок 7 оперативной памяти, накапливающий сумматор 8, коммутатор 9, блок 10 памяти коэ фициентов, коммутатор 11, блок 12 памяти кодов задержек, сумматор 13, блок 14 инвертирования, счетчик 15 текущей выборки, блок 16 управления генератор 17 тактовых импульсов, счетчик 18, коммутатор 19, счетчик 20 канала, коммутатор 21, счетчик 22 коэффициентов, триггеры 23 и 24, дешифратор 25, элемент И 26, формирователь 27 прямоугольных импульсов триггеры 28 и 29, счетчик 30 шага, группу 31 элементов ИЛИ, счетчик 32 направления, коммутатор 33, формирователь 34 прямоугольных импульсов группу 35 элементов ИЛИ, входы и вы ходы 36-41.

Устройство работает следующим образом.

Сигналы с выходов приемников аи- тенной решетки (Р - величина звукового давления на приемнике V,,, ,Vy , три ортогональные компоненты градиента давления приемника, i 1...М) поступают на входы АЦП 2, где дискретизируются и преобразуются в цифровую форму. Формирование сигналов по лучам диаграммы направленности антенной решетки с фазовек- торными элементами выполняется за три этапа.

Первый этап выполняется при поступлении импульса текущей выборки с выхода АЦП 2 на вход блока 16 управления и на вход счетчика 15, который переводится при этом в следующее состояние. Цифровые выборки сигналов с выхода АЦП последовательно поступают на информационный вход коммутатора 3 и с его выхода записы ваются в блок 4. После занесения четырех выборок с последнего фазовек- торного приемника антенной решетки устройство переходит на выполнение второго этапа обработки.

Во время второго этапа осуществляется преобразование сигналов согласно выражениям

X,V v

v,-

V,-,

Vx, Sin I/ + Vy; COS

V,,,- sin - Vx.-cos Ц; VJ( sin ц- + V cosM )

M

V

i: h(j)

V

vf

РДп - j).

0 5 | где V,-, 5 0

.i

Vl

0

p.

1

к

З д

-выборки сигналов градиента давления по осям X, Y, Z с приемника, i 1...М;

-выборка сигнала давления i приемникаi

-длина импульсной характеристики дифференциатора;

Cf - горизонтальный угол$ V - вертикальный угол-, h(j) - коэффициенты импульсной характеристики дифференциатора;

BCw) - кардиоидная характеристика направленности. Первоначально формируется характеристика направленности отдельных фазовекторных приемников путем поворота трехортогональных компонент градиента давления на углы / и i, , задаваемых по входу устройства. Данная операция выполняется за девять тактов.

Во время первого такта из блока 4 считывается KONOioHeHTa V,, которая записывается в регистр множимого умножителя 5. Одновременно из блока 10 памяти коэффициентов считьшают- ся значения функции sinl, которые поступают через коммутатор 11 на вход умножителя 5. Результат умножения с выхода умножителя 5 заносится в предварительно обнуленный накапливающий сумматор 6.

Во время второго такта из блоков 4 и 10 считываются соответственно компонента Vy, и значение функции cos Ц аналогично первому такту и результат умножения с выхода умножителя 5 суммируется с результатом умножения первого такта в накапливающем сумматоре 6.

Во время третьего такта преобра- зованная компонента V передается через коммутатор 3 и записывается в ячейку блока 4, где ранее находился код компоненты V у,.

Во время четвертого такта из бло- ка 10 памяти коэффициентов считывается значение функции sinif, которое через коммутатор 11 поступает на вход умножителя 5, где записывается в регистр множителя. В регистре мно- димого умножителя 5 в это время находится код компоненты V, , записанный во время второго такта, результа умножения вновь заносится в предварительно обнуленный накапливающий сум- матор 6.

Во время пятого такта осуществляется умножение V, на costf и результат умножения вычитается из кода, находящегося в сумматоре 6,

Во время шестого такта преобразованная компонента V(,, записывается в ячейку блока 4, в которой ранее находился код компоненты V, ,

Во время седьмого н восьмого так- тов вычисляется v , которое выполняется аналогично первым двум тактам, отличие заключается лишь в том, что из блока 10 памяти коэффициентов поступают значения sinti, cost, а из блока 4 считываются коды компонент

V x, , V,,.

Во время девятого такта код преобразованной компоненты V , заносит- .ся в первую ячейку блока 7 оператив- ной памяти. На первый адресный вход блока 7 оперативной памяти при этом поступает код номера канала, а на второй адресный вход - код текущей выборки, поступающий с вькода сумма- тора 13, на второй вход которого поступает нулевая информация с выхода блока 12 памяти кодов задержек и с выходов блока 14.

Во время следуюЕцих двух тактов определяется величина В. Во время десятого такта из блока 4 считывается преобразованная компонента V которая заносится в регистр множимого умножителя 5, Во время одиннадцатого такта из блока 4 считывается преобразованная компонента Vy, , которая через коммутатор 11 записывается в регистр множителя, результат умножения записывается в предварительно обнуленный на первом этапе обработки накапливающий сумматор 6.

Во время двенадцатого такта код с выхода накапливающего сумматора 6 записывается во вторую ячейку блока 7 оперативной памяти, с выхода которого поступает на вход накапливающего сумматора 8, где суммируется с предьщущим результатом.

Начиная с тринадцатого такта, в устройстве выполняется К тактов (К - длина импульсной характеристики дифференциатора) , во время которых осуществляется коррекция амплитудно- частотной характеристики и сдвиг фазы на 90° сигналов звукового давления Р. Такты работы дифференциатора вьшолняются следующим образом. С выхода 41 блока 16 управления на вхо блока 10 памяти коэффициентов поступает уровень 1, который выбирает область в памяти коэффициентов, в которой находятся коэффициенты импульсной характеристики дифференциатора, тот же уровень 1 поступает на управляющий вход коммутатора 9, подключая выход 40 блока 16 управле- ния через данный коммутатор к входу блока 10 памяти коэффициентов. С выхода 39 блока 16 поступают код адреса канала и коды адресов для считывания К выборок сигнала звукового давления Р первого приемника. С выхода блока 4 выборки Р записываются в регистр множимого умножителя 5. Одновременно на вход регистра множителя через коммутатор 11 поступают значения коэффициентов импульсной характеристики дифференциатора. В конце каждого такта результат умножения заносится в накапливающий сумматор 6, который перед первым тактом дифференцирования обнуляется. После выполнения К тактов дифференцирования преобразованная выборка сигнала Р заносится во вторую ячейку первого какала блока 7 оперативной памяти. На адресный вход данного блока с выхода сумматора 13 поступает код, равный сумме кода счетчика 15 и кода К/2-1, Запись со сдвигом выборки сигнала звукового давления Р производится для компенсации задержки сигналов при дифференцировании. Для формирования кода К/2 - 1 на вход блока 14 с выхода блока 16 поступает уровень 1, нулевая информация, поступающая с выхода блока 12, преобразуется на выходе блока 14 в код, состоящий из логических единиц. После занесения выборки Р. на адресный

вход блока 4 с выхода 39 блока управления поступает код адреса следующего канала и налинаются такты преобразования четырех выборок V, V,

обработки следующим образом. Импуль выборки, поступающий на вход блока 16, устанавливает триггеры 23 и 24 в единичное состояние.Уровень с выхода триггера 23 разрешает работу генератора 17, которьш вырабатывает при этом серию тактовых импульсов, поступающих на вход счетчика 18, на 10 его выходе последовательно появляют ся коды, по которым осуществляется запись четырех компонент сигналов каждого фазовекторного приемника.-- Код адреса с выхода счетчика 18 че

V-J, Р следующего канала, которые вы- 15 рез группу 35 элементов ИЖ поступолняются аналогично описа:нному. После окончания преобразования выборок последнего канала устройство переходит к третьему этапу обработки выборок сигналов антенной решетки. 20

Во время вьшолнения третьего этапа обработки осуществляется форкиро- вание выборок сигналов по лучам диаграммы направленности. Этап выполняется следующим образом. С выхода 36 25 . блока управления на блоки 12 и 7 поступают код адреса канала, и код номера направления. В блоке 12 находятся коды относительных задержек каналов для различных направлений зо прихода сигналов. На выходе сумматора 13 формируется код, равньй сумме кода на выходе счетчика 15 и выходного кода на выходе блока 12, По данному коду из блока 7 оперативной g памяти считывается одйа выборка из массива выборок сигналов данного канала. Код с выхода данного блока поступает на вход накапливающего сумматора 8, который перед формирова- 40 нием сигнала по каждому направлению общгляется. После считывания выборок сигнала звукового давления Р производится считывание преобразованной компоненты колебательной скорости 45 V для каждого канала. После считывания двух выборок сигналов последнего канала на выходе устройства формируется суммарный сигнал Р + + V по данному направлению и уст- 50 ройство переходит к формированию сигнала по следующему лучу диаграммы направленности. После формирования, сигнала по последнему лучу диаграммы направленности устройство переходит gg в режим ожидания до прихода следую- щего импульса выборки.

Блок 16 управления формирует управляющие сигналы для трех этапов

пает на выход 39 блока управления. Сигнал с выхода второго разряда сч чика 18 поступает через коммутатор 19 на вход Счетчика 20 каналов и задним фронтом устанавливает его в следующее состояние. На выход 39 блока 16 поступает код адреса сле дующего канала и происходит запись очередных четырех компо ьант в блок 4. После записи выборок последнего канала сигнал с выхода старщего ра ряда счетчика 20 задним фронтом ус танавливает триггер 24 в состояние О, что приводит к установке в ед ничное состояние триггера 28. Одно временно сигнал с выхода старшего разряда счетчика канала 20 через коммута тор 21 задним фронтом устанавливает в следующее состояние счетчик 22, код с выхода которого поступает таюке на выход 39 блока

Формирование управляющих сигналов для второго этапа обработки выполняется следующим образом. Уро

вень 1 с выхода триггера 28 пост па.ет на .установочный вход счетчика 30 и переводит его в счетный режим Формирование управляющих сигналов для преобразования компонент одно канала поясняется временными диаграммами, приведенными на фиг. 3. Один из участков временных диаграм соответствует операции поворота вы борок трех компонент градиента да ления Vx, V,,, Vj,, а другой - дифф ренцированию выборок сигнала звук вого давления Р, Выходной код сче чика 30 поступает на вход депшфра .тора 25, на выходе которого появл ются уровни 1, разрешающие форм рование управляющих сигналов для вьшолнения данного такта второго .этапа. На первом выходе дешифрато ра 25 формируется код адреса для

23516

обработки следующим образом. Импульс выборки, поступающий на вход блока 16, устанавливает триггеры 23 и 24 в единичное состояние.Уровень с выхода триггера 23 разрешает работу генератора 17, которьш вырабатывает при этом серию тактовых импульсов, поступающих на вход счетчика 18, на 10 его выходе последовательно появляются коды, по которым осуществляется запись четырех компонент сигналов каждого фазовекторного приемника.-- Код адреса с выхода счетчика 18 через группу 35 элементов ИЖ поступает на выход 39 блока управления. Сигнал с выхода второго разряда счетчика 18 поступает через коммутатор 19 на вход Счетчика 20 каналов и задним фронтом устанавливает его в следующее состояние. На выход 39 блока 16 поступает код адреса следующего канала и происходит запись очередных четырех компо ьант в блок 4. После записи выборок последнего канала сигнал с выхода старщего разряда счетчика 20 задним фронтом устанавливает триггер 24 в состояние О, что приводит к установке в единичное состояние триггера 28. Одновременно сигнал с выхода старшего разряда счетчика канала 20 через коммута тор 21 задним фронтом устанавливает в следующее состояние счетчик 22, код с выхода которого поступает таюке на выход 39 блока 16

Формирование управляющих сигналов для второго этапа обработки выполняется следующим образом. Уровень 1 с выхода триггера 28 посту па.ет на .установочный вход счетчика 30 и переводит его в счетный режим. Формирование управляющих сигналов для преобразования компонент одного канала поясняется временными диаграммами, приведенными на фиг. 3. Один из участков временных диаграмм соответствует операции поворота выборок трех компонент градиента давления Vx, V,,, Vj,, а другой - дифференцированию выборок сигнала звукового давления Р, Выходной код счет- чика 30 поступает на вход депшфра- .тора 25, на выходе которого появляются уровни 1, разрешающие формирование управляющих сигналов для вьшолнения данного такта второго .этапа. На первом выходе дешифратора 25 формируется код адреса для

считывания и записи информации четы рех выборок каждого канала из блока 4, который поступает через группу 35 элементов ИЛИ на выход 39 блока 16. Сигнал .с второго выхода дешифратора, который также поступает на выход 3.9, управляет режимом записи- считывания информации блока 4. Код с третьего выхода дешифратора 25 разрешает формирование тактовых импульсов для записи информации в накапливающий сумматор 6 и его обнуления и записи информации в регист10

циатора. Код с восьмого выхода дешифратора 25 поступает через коммутатор 33 на выход 37 блока 16 и используется для записи информации в накапливающий сумматор 8 при получе нии кардиоидной характеристики направленности. После вьтолнения К так тов счетчик 30 обнуляется. Сигнал с выхода старшего разряда данного счетчика через коммутатор 19 задним фронтом переводит счетчик 20 в следующее состояние, и осуществляется фор.мирование управляюпщх сигналов

ры умножителя 5. Формирование импуль-15 Для преобразования четырёх выборок

35

сов осуществляется формирователем 27 по фронтам импульсов, поступающих с генератора 17 тактовых импульсов в соответствии с временными диаграммами на фиг. 3. Импульсы за- 20 писи и обнуления поступают с выхода формирователя 27 на выход 38 блока 16. Код с четвертого выхода дешифратора 25 разрешает прохождение тактовых импульсов с выхода генерато- 25 ра 17 через элемент 26 и коммутатор 21 на вход счетчика 22 во время вьтолнения .тактов дифференцирования. Данный счетчик считает по; модулю К, поэтому по поступлении К-го так- зО тового импульса счетчик устанавливается в исходное состояние. Код с выхода счетчика 22 поступает на выход 39 блока 16 и используется для считывания К выборок сигнала Р по данному каналу. Код с пятого выхода дешифратора 25 поступает на выход 37 блока 16 и используется для управления записью преобразованных компонент в блок 7 оперативной памяти. На Q этом же выходе формируется уровень 1 при записи преобразованной выборки Р , который поступает на вход блока 14. На шестом вькоде дешифратора 25 формируется код адреса для 45 занесения преобразованных компонент в соответствующие две ячейки блока 7 оперативной памяти. Данный код через элементы ИЛИ группы 31 поступа- .ет на выход 36 блока 16. Код с седьмого выхода дешифратора 25 поступает на выход 46 блока 16 и управляет передачей информации через коммутаторы 11 и 9, а также выбирает области блока 10 памяти коэффициентов, в gg которых расположены значения функций синуса и косицуса углов поворота . градиентных компонент и коэффициенты импульсной характеристики дифференсигналов следующего приемника аналогично описанному. При формировании управляющих сигналов последнег канала сигнал с выхода старшего ра ряда счетчика 20 задним фронтом сб сывает триггер 28, который устанавливает при этом в единичное сос тояние триггер 29.

I

50

Формирование управляющих сигнал третьего этапа обработки производи ся следующим образом. На вход счет чика 20 поступают через коммутатор 19 с выхода счетчика 18 импульсы, которые переключают сетчик 20 в сл дующее состояние. Коды с выхода сч чика 20 поступают на выход 36 блок 16. На этот же вькод поступают код с выходов разрядов счетчика 32 и ч рез элементы ИЖ группы 31 код с выхода первого разряда счетчика 32 который используется для управлени считыванием выборок Р или v . Сче чик 32 переключается в следующее состояние по заднему фронту сигнал с выхода старшего разряда счетчика 20. Импульсы записи для накапливаю щего сумматора 8 поступают с выхо да коммутатора 33 на выход 37 бло 16. После формирования суммарного сигнала Р + V по данному направл нию по заднему фронту сигнала с вы хода первого разряда счетчика 32 формируются импульсы сопровождения информации и импульсы обнуления на капливающего сумматора 8 с помощью формирователя 34. При формировании сигнала по последнему направлению по заднему фронту сигнала с выход последнего разряда счетчика 32 сб сываются триггер 23 и триггер 29 блок 16 управления прекращает фор рование управляющих сигналов до пр хода следующего импульса пуска.

циатора. Код с восьмого выхода дешифратора 25 поступает через коммутатор 33 на выход 37 блока 16 и используется для записи информации в накапливающий сумматор 8 при получении кардиоидной характеристики направленности. После вьтолнения К тактов счетчик 30 обнуляется. Сигнал с выхода старшего разряда данного счетчика через коммутатор 19 задним фронтом переводит счетчик 20 в следующее состояние, и осуществляется фор.мирование управляюпщх сигналов

Для преобразования четырёх выборок

Для преобразования четырёх выборок

сигналов следующего приемника аналогично описанному. При формировании управляющих сигналов последнего канала сигнал с выхода старшего разряда счетчика 20 задним фронтом сбрасывает триггер 28, который устанавливает при этом в единичное состояние триггер 29.

I

Формирование управляющих сигналов третьего этапа обработки производится следующим образом. На вход счетчика 20 поступают через коммутатор 19 с выхода счетчика 18 импульсы, которые переключают сетчик 20 в следующее состояние. Коды с выхода счетчика 20 поступают на выход 36 блока 16. На этот же вькод поступают код с выходов разрядов счетчика 32 и через элементы ИЖ группы 31 код с выхода первого разряда счетчика 32, который используется для управления считыванием выборок Р или v . Счетчик 32 переключается в следующее состояние по заднему фронту сигнала с выхода старшего разряда счетчика 20. Импульсы записи для накапливающего сумматора 8 поступают с выхода коммутатора 33 на выход 37 блока 16. После формирования суммарного сигнала Р + V по данному направлению по заднему фронту сигнала с выхода первого разряда счетчика 32 формируются импульсы сопровождения информации и импульсы обнуления накапливающего сумматора 8 с помощью формирователя 34. При формировании сигнала по последнему направлению по заднему фронту сигнала с выхода последнего разряда счетчика 32 сбрасываются триггер 23 и триггер 29 и блок 16 управления прекращает формирование управляющих сигналов до прихода следующего импульса пуска.

Формула изобретения

1. Устройство для обработки данных при формировании диаграммы кап- равленности антенной решетки, содержащее блок приема, выход которого соединен с информационным входом аналого-цифрового преобразователя, выход ГОТОВНОСТИ которого соединен со счетным входом .счетчика текущей выборки и входом пуска блока управления, первый выход которого соединен с адресным входом блока памяти кодов задержек и первым адресным входом блока оперативной памяти, выход которого подключен к информационному входу первого накапливающего сумматора, выход которого является выходом устройства, второй ад- ресный вход блока оперативной памяти соединен с выходом сумматора, вход первого слагаемого которого подключен к выходу счетчика текущей выборки, отличающееся тем, что, с целью расширения функциональных возможностей за-счет получения сигналов по лучам диаграммы направленности антенной решетки, на выходах приемников которой формиру- ются сигналы звукового давления и градиента давления по трем ортогональным координатам, в него введены первый, второй, третий коммутаторы, блок буферной- памяти, умножитель, второй накапливающий сумматор, блок инвертирования, блок памяти коэффициентов, причем информационньй выход аналого-цифрового преобразователя соединен с первым информационным входом первого коммутатора, второй информационный вход которого подключен к информационному входу блока оперативной памяти и к выходу вторр го накапливающего сумматора, второй выход блока управления соединен с .разрешающим входом блока инвертирования, с входом записи первого накапливающего сумматора и с входом записи/считывания блока оперативной памяти, управляющие входы второго накапливающего сумматора и умножителя подключены к третьему вькоду блрк управления, четвертый выход которого подключен к входу задания опера- ции блока буферной памяти,выход котрого подключен к первому информационному входу второго коммутатора и к входу множимого умножителя, вых

5

0 0 5 О 5 0 5

которого соединен с информационным входом второго накапливающего сумматора, вход множителя умножителя соединен с выходом второго коммутатора, второй информационньй вход которого подключен к выходу блока памяти коэффициентов, информационный вход которого соединен с выходом третьего коммутатора, первый информационный вход которого является входом устройства, второй информационный вход соединен с пять1м выходом блока управления, шестой выход которого подключен к управляющим входам первого, второго и третьего коммутаторов и к входу задания операции блока памяти коэффициентов, выход первого коммутатора соединен с информационным входом блока буферной памяти, первьш выход блока памяти кодов задержек и выход блока инвертирования подключе-- ны к входам второго и третьего сла- raeMbJx сумматора соответственно, второй выход блока памяти кодов задержек соединен с информационным входом блока инвертирования,

2. Устройство по п. 1, отличающееся тем, что блок управления содержит четыре триггера, счетчик, коммутаторы, счетчик канала, счетчик коэффициентов, счетчик шага, Дешифратор, счетчик направления, две группы элементов ШИ, элемент И, два формирователя прямоугольных импульсов и генератор тактовых импульсов, вход запуска которого соединен с выходом первого триггера, а выход подключен к счетному входу счетчика, к счетному входу счетчика ша.га, к.первому входу элемента И и к тактовому входу первого формирователя прямоугольных импульсов, выход которого является третьим выходом блока, единичные входы первого и второго триггеров соединены с входом пуска блока, выход второго триггера соединен с единичным входом третьего триггера, с управляющим входом первого коммутатора и с шестым выходом блока,выходы разрядов счетчика соединены с первьЕми входами элементов ИЛИ первой группы, выходы которых соединены с четвертым выходом блока, вторые входы элементов ИЛИ первой группы соединены с первьм выходом дешифратора, второй выход которого соединен с четвертым выходом блока, третий выход дешифратора соединен с управляющим входом первого формирователя прямоугольных импульсов, четвертый вьсход дешифратора соединен с вторым входом элемента И, выход которого соединен с первым информационным входом первого коммутатора, выход которо го соединен со счетным входом счетчика коэффициентов, выход которого подключен к чет вертому выходу блока, выход второго разряда счетчика соединен с первыми информационными входами второго и третьего коммутаторов, выход второго коммутатора соединен со счетньм входом счетчика каналов, выходы разрядов которого соединены с первым и четвертым выходами блока, выход старшего разряда счетчика каналов соединен с вторым информационным входом первого коммутатора, с нулевыми входами второго и третьего триггеров и со счетньм входом счетчика направления, выход последнего разряда которого соединен с кулевыми входами первого и четвертого триггеров, выход третьего триггера соединен с управляющими входами второго коммутатора и дешифратора, с единичным входом четвертого триггера и с установоч

ным входом счетчика шага, выход четвертого триггера соединен с установочным входом счетчика направления и с вторым информационным входом третьего коммутатора, выход которого соединен с вторым выходом блока, выходы разрядов счетчика шага соединены с информационным входом дешифратора и с пятым выходом блока, выход старшего разряда счетчика шага соединен с вторым информационным входом второго коммутатора, пятый выход дешифратора соединен с вторым выходом блока, шестой выход подключен к первым входам элементов ИЛИ второй группы, выходы которых соединены с первым выходом блока, вторые входы элементов ИЛИ второй группы и вход второго формирователя прямоугольных импульсов соединены с выходом первого разряда счетчика направления, выходы разрядов которого соединены с первым выходом блока, выход второго формирователя прямоугольных импульсов соединен с вторым выходом блока, седьмой выход дешифратора соединен с шестым выходом блока, восьмой выход подключен к управлякиде му входу третьего коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой обработки сигналов | 1988 |

|

SU1575203A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Многоканальный цифровой интерполирующий фильтр для частотного уплотнения каналов | 1987 |

|

SU1525716A1 |

| Многоканальный цифровой интерполирующий фильтр | 1986 |

|

SU1401480A1 |

| Цифровой фильтр | 1988 |

|

SU1566469A1 |

| Многоканальный перестраиваемый цифровой фильтр | 1988 |

|

SU1569955A1 |

| Цифровой согласованный фильтр для импульсных эхо-сигналов | 1981 |

|

SU964979A1 |

| Устройство для реализации быстрого преобразования Хартли | 1987 |

|

SU1444815A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Устройство для измерения вероятностных характеристик фазы случайного сигнала | 1985 |

|

SU1320822A1 |

Изобретение относится к вычислительной технике и может использоваться для обнаружения и определения направления на источник излучения сигналов. Целью изобретения является расширение функциональных возможностей за счет получения сигналов по лучам диаграммы направленности антенной решетки, на вводах приемников которой формируются сигналы звукового давления и градиента давления по трем ортогональным координатам. Устройство содержит блок 1 приема, аналого-цифровой преобразователь 2, коммутатор 3, блок 4 буферной памяти, умножитель 5, накашшвакнций сумматор 6, блок 7 оперативной памяти, накапливающий сумматор 8, коммутатор 9, блок 10 памяти коэффициентов, коммутатор 11, блок 12 памяти входов задержек, сумматор 13, блок 14 ин- , вертирования, счетчик 15 текущей выборки, блок 16 управления. 3 ил. (Л

39

37

С

с

I

«5

::э

«5 Ъ

-1 1

§4

1

ij I

§5

«

||«

1 1

5, S «

ь

1

«о

: в

1

3

I

h«

«5

I.

4- §

«

IEl

I l«

SI-,55

W

s

I

I

ga

1г

| Устройство для управления лучом антенной решетки | 1983 |

|

SU1144118A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство для управления решеткой излучателей | 1983 |

|

SU1150630A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1987-08-28—Подача