группой ходоЪ блока уптретьейравления.

2. Процессор по п, 1, о т л й.чающийся TeMj что блок управления содержит генератор тактовых, импульсов , триггер, девять элементов И, счетчик тактов, дешифратор тактов, шесть элементов ИЛИ, выходной регистр, счетчик циклов . и схему сравнения кодов, причем вход запуска блока подключен к входу . установки в единицу триггера, выход которого соединен с первы;ми входами первого и второго элементов И, первый вход первого элемента ИЛИ соединен с первым входом признака функции блока, второй и третий входы признака функции блока соединены с первым и Вторым входами третьего элемента И и второго элемента ИЛИ, четвертый вход признака функции блока соединен с третьим входом второго элемента ИЛИ и вторым входом первого элемента ИЛИ, первый вход первой группы входов блока соединен с первым входом четвертого элемента И, второй вход первой группы входов блока соединен со вторыми входами второго и четвертого элементов И и первым входом пятого элемента И, выход третьего элемента И соединен с первым входом, а выход первого элемента ИЛИ - со вторым входом шестого элемента И, первый вход признака функции блока соединен с четвертым входом второго элемента ИЛИ и первым входом седьмого элемента И, первый вход второй группы входов блока соединен со вторым входом седьмого элемента И, второй вход второй группы входов блока соединен с третьим входом четвертого элемента И, третий вход второй группы входов .соединен с четвертым входом четвертого элемента И и первыми входами восьмого и девятого элементов И, выходы седьмого и восьмого элементов И соединены с первым и вторым входами треть го элемента ИЛИ соответственно, выходы четвертого иПятого элементов И .соединены с первым и вторым входами , четвертого элемента ИЛИ соответст венно, первая группа входов схемы сравнения кодов подключена к третьей группе входов блока, а вторая группа входов схемы сравнения кодов соединена с входами счетчика циклов, выход схемы сравнения кодов соединен с входом установки в ноль триггера,

второй вход первого элемента И. сое. дйнен с выходом генератора тактовых импульсов, а выход - со счетным входом счетчика тактов, выходы которого соединены с входами дешифратора тактов, первый выход которого соединен с пятым входом второго элемейта ИЛИ, второй выход дешифратора тактов соединен с третьим входом третьего элемента И, третий выход

;этого дешифратора соединен с третьим входом шестого элемента И, четвертый выход дешифратора тактов соединен с пятым входом четвертого элемента И, пятый и шестой выходы дешифратора тактов соединены с первым и вторым входами пятого элемента ИЛИ соответственно, седьмой выход дешифратора .тактов соединен с третьим входом седьмого элемента И, восьмой выход дешифратора тактов соединен со вторым входом пятого .элемента И, девятый выход дешифратора тактов соединен с первым входом шестого элемента ИЛИ, десятый выход дешифратора тактов соединен со вторыми входами восьмого и девятого элементов И, одиннадцатый выход дешифратора тактов соединен со вторым входом шестого элемента ИЛИ, четвертый вход седьмого элемента И подключен к выходу триггера, выходы второго элемента ИЛИ, второго и третьего элементов И, четвертого и пятого элементов ИЛИ, шес. того, восьмого и седьмого элементов И, шестого и третьего элементов ИЛИ подключены к первому -.десятому входам выходного регистра соответственно, первый, второй и .третий выходы которого соедине ы с первой группой выходов блока, четвертый выход выходного регистра соединен с первым выходом блока, пятый выход выходного регистра соединен с вторым выходом блока, шестой и седьмой выходы выходного регистра соединены со второй группой выходов блока, восьмой выход выходного регистра подключен к третьему выходу блока и счетному входу счетчика циклов, девятый выход выходного регистра соединен с четвертым выходом -блока,, десятый выход выходгного регистра соединен с пятым вы:Лэдом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Цифровой генератор функций | 1987 |

|

SU1413613A1 |

| Специализированный процессор | 1977 |

|

SU723581A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Арифметическое устройство | 1978 |

|

SU780004A1 |

| Устройство для измерения параметров газовых сред | 1980 |

|

SU894527A1 |

1. СПЕЦИАЛИЗИРОВАННЫЙ ПРОЦЕССОР , содержащий входной, регистр., счетчик порядка, сдвигатель, первое 1 и второе запоминающие устройства .: коэффициентов аппроксимирующего поли.нома, множительное устройство, сум/матор, регистр .функции, группу элементо И и выходной регистр, причем первая группа входов входного ре.-гистра подключены к входам мантиссы, аргумента процессора, первая группа выходов этого регистра соединена с информационными входами .сдвигате- / ля/ вторая группа выходов входного регистра соединена с адресными вхсэдами первого запоминающего устройства коэффициентов аппроксимирующего . полинома, выходы которого подключе ны к первой группе входов множитёл.ьного устройства, выходы которого подключены к входам первого слагаемого сумматора, выходы которого подключены ко второй группе входов входного регистра и информационным входам регистра функции, выходы которого соединены с информационными входами выходного регистра и первьа 1и входами элементов И группы, выходы которых . соединены со второй группой входов множительного устройства, выходы которого подключены к третьей группе входов входного регистра, третья Группа выходов которого соединена с;третьей группой входов множительного. устройства и входами второго слагаемого сумматора, установочные входы счетчика порядка подключены к входам порядка аргумента процессора, пер. вая группа выходов счетчика порядка подключена .к четвертой группе входов множительного устройства, вторая группа выходов счетчика порядка сое:динена с управляющими входами едвигателя, выходы которого соединены садресными входами второго запоми нающего устройства коэффициентов аппроксимирующего полинома, выходы .которого соединены с входами третьего слагаемого сумматора, вход запуска блока управления подключен к входу запуска процессора, входы признаков функции блока управления соединены (Л с,входами признаков функции процессора, первая группа входов блока уп;равления соединена е четвертой груп-. пой выходов входного регистра, вто-рая группа входов блока управления соединена со второй группой выходов счётчика порядка, первая группа вы; ходов блока упразвления соединена с . выходами прйзнаасов процессора, первый выход блока управления соединен с входом синхронизации регистра функ;ЦИК, второй выкод блока управления соединен с управляющим входом второго запоминающего устройства коэффициентов аппроксимирующего, полинома, ;третий выход блока управления соеди;нен со вторыми входами элементов И группы, четвертый выход блока управ;Лёния соединен с входом синхронизации выходнргО регистра, пятый выход блока управления соединен с входом :установки в ноль выходного регистра, о т ли ч а ю и и и с я тем, что, .целью увеличения производительнос, ти, в него введено запоминающее устройство степени аппроксимирующего полинома, адресные входы которого подключены к выходам сдвига;теля, а выходы соединены г

Изобретение относится к вычислительной технике и может быть использовано в качестве периферийного устройства универсальных и специализирорванных ЦВМ иликак специализированный фуйИЩиональныйпреобразователь BJ различных вычислительных и управляю;щих системах для вычисления элементарных функций с высокой точностью и быстродействием.

Известен специализированный ;Процессор - цифровой интерполятор высокого порядка, содержащий выход-: ной регистр, множительное устройство, постоянное запоминающее ус.тройCTiBO, сумматор, регистр функции, две группы элементов И,: выходной бу-фер и блок управления. Процессор позволяет вычислять значения элементарных функций, которые могут бытьразложены в ряд Тейлора 1.

Недостаток такого процессора ртсутствие технических средств приведения значений аргумента к стан- . .дартному интервалу (0,1) .и, как следствие, отсутствие возможности, вычисления значений элементарных функций от аргументов, представленных в форме с плаваюгцей точкой, что значительно сужает область применения указанного специализирован-ного процессора.

Наиболее близким к изобретению является специализированный процессор , содержащий входной регистр., счетчик порядка, сдвигатель, первое запоминающее устройство С ЗУ), множительное устройство, сумматор, первую группу элементов- И, второе/ ЗУ, блок управления, регистр функции, вторую группу элементов И, выходной региртр, причем выходил входного регистра соединены с входами .сдвигателя, множительного устройства, сумматора, первого ЗУ, , выходы счетчика порядка соединены с входами сдвигателя, множительного, устройства и блока управления, вы- ;. ходы;сдвигателя подключены.к входам: второго ЗУ, выходы первого ЗУ подключены к входам множительного устройства,ВЫХОДЫ которого со цинены с .входами сумматора и входного регистра, .выходы сумматора подключены к входам регистра функции и . входного регистра, первой группы элементов И подсоединены к , входам сумматора, выходы второго ЗУ подключены к входам первой группы элементов И, выходы БУ соединены с входами счетчика порядка, первой группы элементов И,регистра функции, второй группы элементов Ни выходного регистра, выходы регист- ра функций подключены к входам второй группы элементов И и выходного регистра, выходы второй группы элементов И связаны с входами МУ, выходы выходного регистра могут сое.дийяться с входами внешйих устройств. ;Введение в процёссЬр счетчика по|рядка, сдвигателя и первого ЗУ пЬзволяет ВЫЧИСЛЯТЬ значения- х ункций е , hnx, sinx,cosx от аргументов с плавающей точкой, т.е. расширить диапазон представления аргументов и, как следствие, расширить область применения устройства 2 j . ;

однако известное устройство характеризуется сравнительно низкой производительностью, обусловленной отсутствием технических средств

0 адаптации к особенностям различных элементарных функций и характеру их доведения в зависимости от текущего зиачения аргумента.

Причина этого кроется в методах

5 проектирования многофункциональных специализированных процессоров, в частности - в методике выбора степени аппроксимирующего полинома И, которая выбирается исходя из условия обеспечения заданной методичес

0 кой погрешности аппроксимации при допустимых аппаратурных затратах. В случае использования ряда Тейлора методическая ошибка равна

5

р . («1-1)1

:где |М:--тох

- максимальное I .тсеЩЦ значение мо0дуля IVH-1 ) -и

ИЫ.К) производной на интервале 10,1) для i -И функции из

ляции.

Так как М: явлЛется функцией от Ч| то она может меняться на интерва- ле в широких пределах. Например, для ич.(Х-И)модуль шестой производной меняется от 720 до 5,63 при

5 X 1, т.е. более чем на два порядкаJ Следовательно, при фиксированном зна чении h в тех же пределах меняется и методическая сяаибка. Еше большее различие М наблюдается у разных

0 по свойствам функций, так при X - О модуль шестой производной стремится в О (для 1м{Х- Ч) . Таким образом, степень полинома, выб; ранная по наихудшему с гучаю из усло5вия (iVf является величиной завышенной не только Для тех функций, у которых но и для каждой конкретной из функций при различных значениях аргумента. Следовательно;

0 имеется теоретическая возможность изменять степень аппроксимирующего полинома в процессе вычисления в э ;Висимости от вида ЭФ и значения ар ;гумента при выполнении требования Ьбеспечения заданной методической

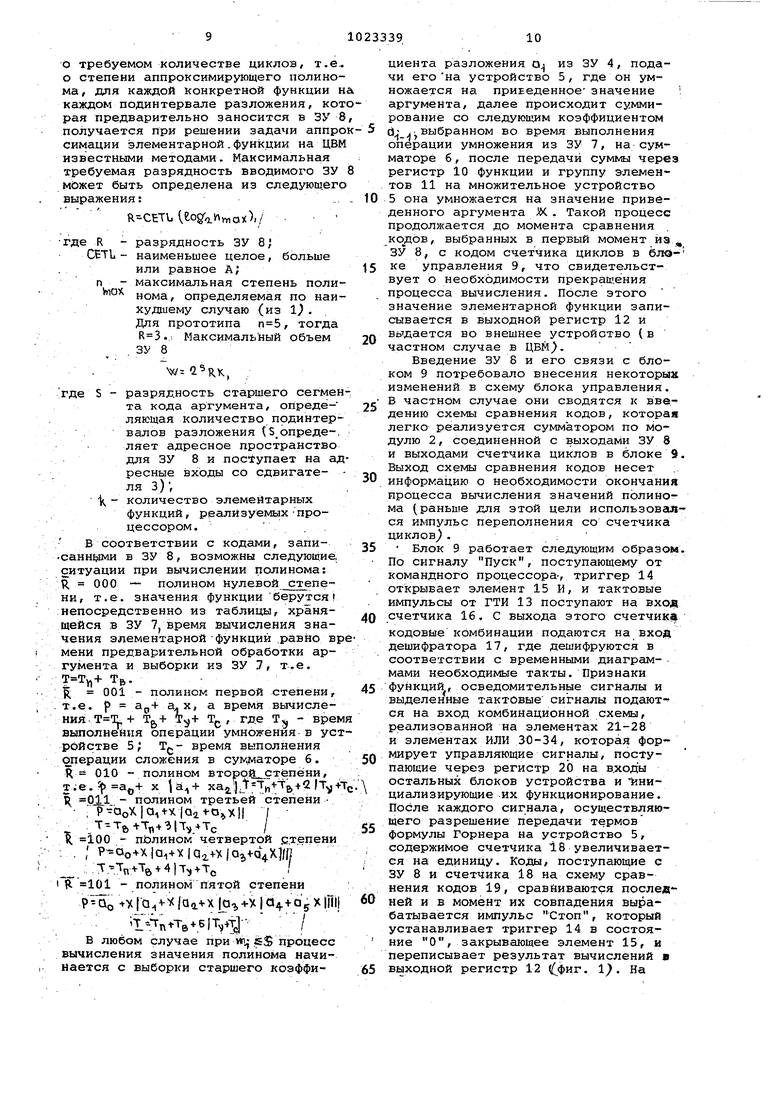

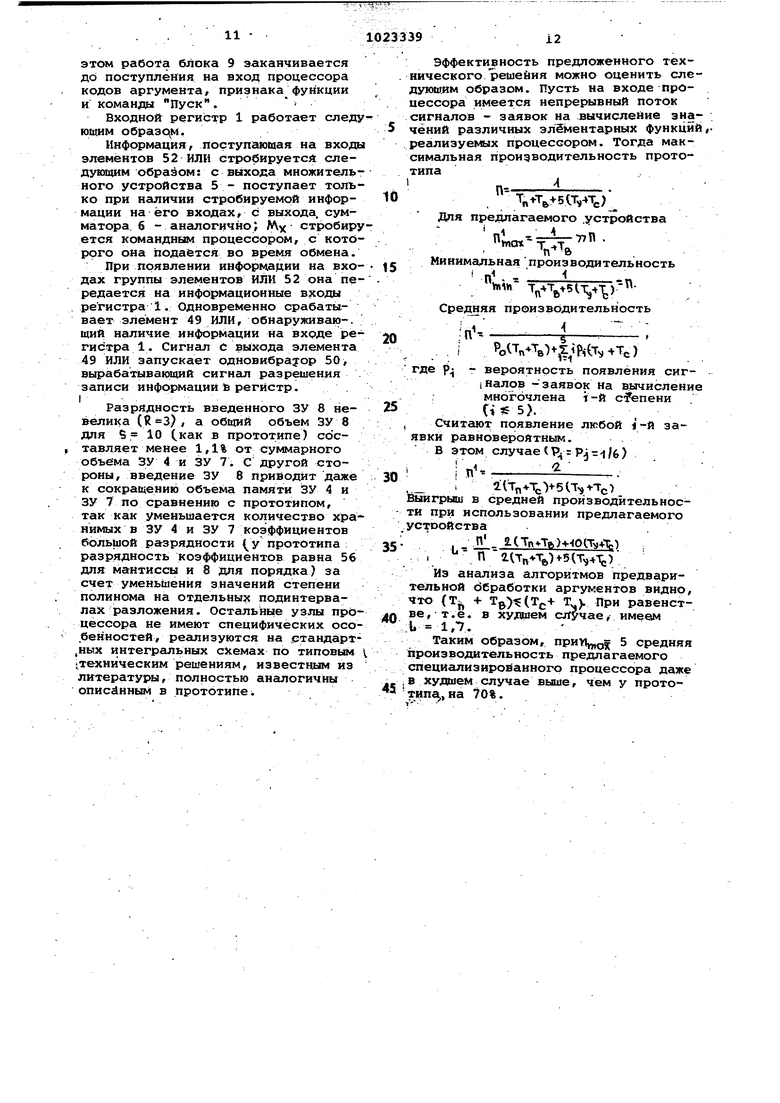

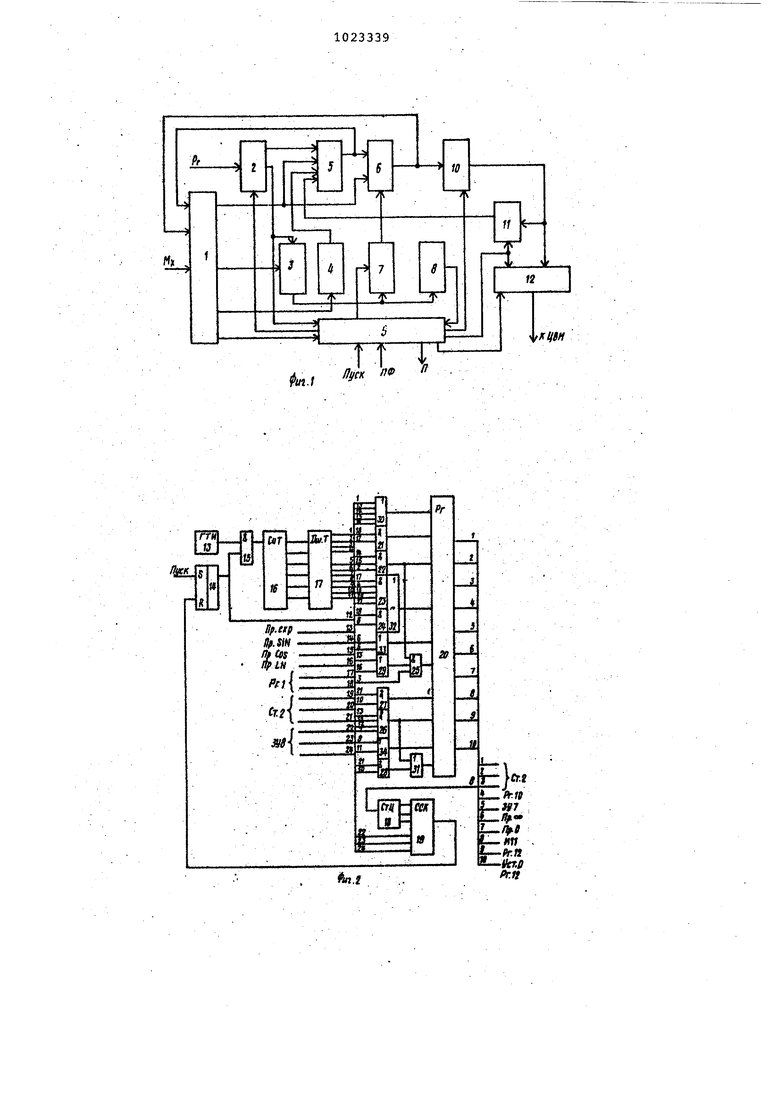

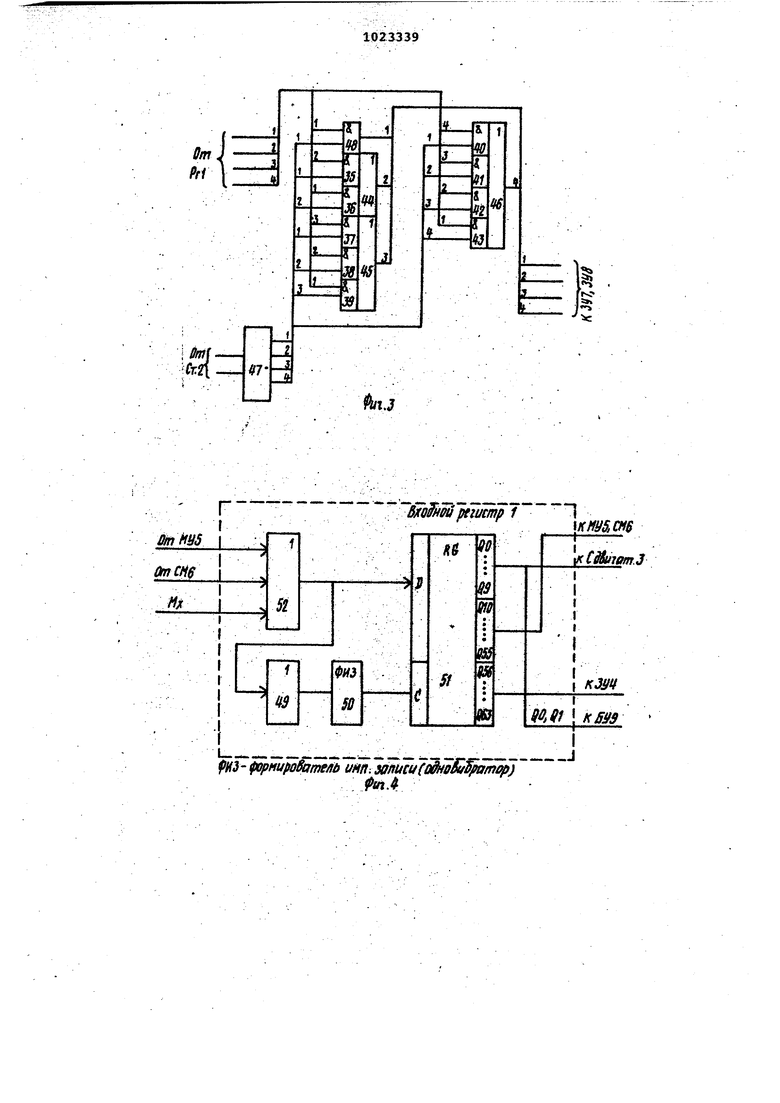

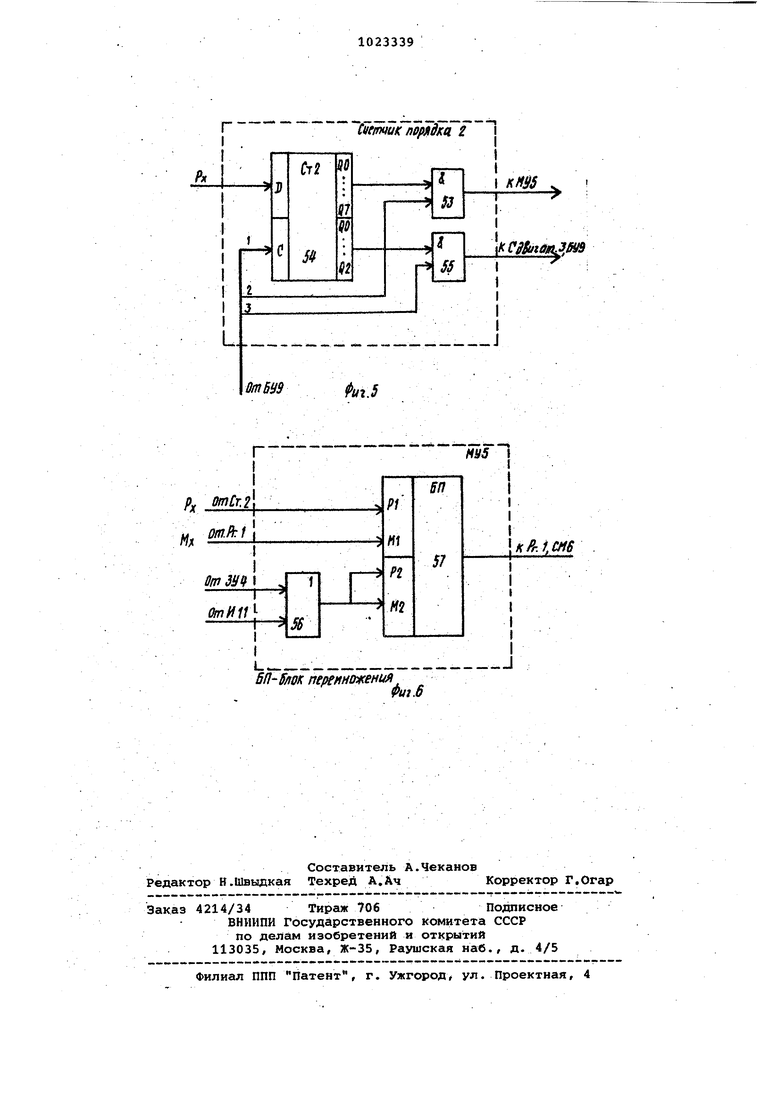

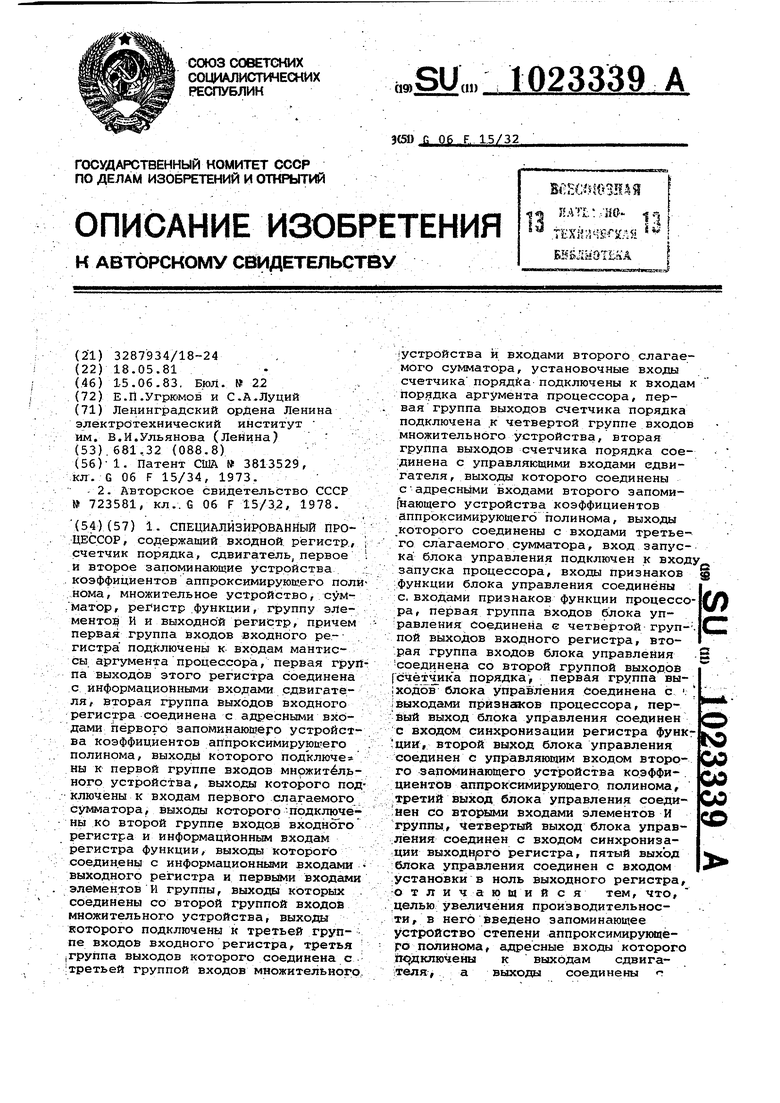

5 погрешности. Это являвтся резервом для увеличения производительности процессора. Целью изобретения является увели чение производительности специалйзированного процессора. Поставленная цель достигается тем, что в процессор, содержаний входной регистр, счетчик порядка, сдвигатель, первое и второе запоминающие устройства коэффициентов аппроксимирующего полинома, множительное устройство, сумматор, регистр функции, группу элементов И и выходной регистр, причем первая группа входов входного регистра подключена к входам мантиссы аргумента процессора, первая группа выходов этого регистра соединена с информационными входами сдвигателя, вторая группа выходов входного регистра соединена с адресными входами первого запоминающего устройства коэффициентов аппроксимирующего полинома, выходы которого подключены к первой группе входов множительного устройства, выходы которого подключены к входам первог слагаемого сумматора, выходы которо подключены ко второй группе входов входного регистра и информационным входам регистра функции, выходы кот рого соединены с информационными входами выходного регистра и первым входами элементов И группы, выходы которых соединены со второй группой входов множительного устройства, вы ходы которого подключены к третьей группе входов входного регистра, третья группа выходов которого соединена с третьей группой входов мно жительного устройства и входами вто рого слагаемого сумматора, установочные входы счетчика порядка подключены к входам порядка аргумента процессора, первая группа выходов счетчика порядка подключена к четвертой группе входов множительного устройства, вторая группа выходов счетчика порядка соединена с управляющими входами сдвигателя, выходы которого соединены с адресными входами второго запоминающего устройства коэффициентов аппгэоксимирующего полинома, выходы которого соединены с входами третьего слагаемог сумматора, вход запуска блока управ ления подключен к входу запуска про цессора, входы признаков функции блока уп равления соединены с входами признаков функции процессора, первая группа входов, блока управления соединена с четвертой группой выходов входного регистра, вторая группа входов блока управления соединена со второй группой выходов счетчика порядка, первая группа выходов блока управления соединена с входами синхронизации счетчика порядка, вторая группа выходов блока управления соединена с выходами признаков процессора, первый выход блока управления соединен с входами синхронизации регистра функции, второй выход блока управления соединен с управляющим входом второго запоминающего устройства коэффициентов аппроксимирующего полинома третий выход блока управления соединен со вторыми входами элементов И группы, четвертый выход блока управления соединен с входом синхронизации выходного регистра, пятый Еыход блока управления соединен с входом установки в ноль выходного регистра, введено запоминающее устройство степени аппроксимирующего полинома, адресные входы которого подключены к выходам сдвигателя, а выходы соединены с третьей группой входов блока управления. Кроме того, блок управления содержит генератор тактовых импуЛьсов, триггер, девять элементов И, счетчик тактов, дешифратор тактов, шесть элементов ИЛИ, выходной регистр, счетчик циклов и схему сравнения кодов, причем вход запуска блока подключен к входу установки в единицу триггера, выход которого соединен с .первыми входами первого и второго элементов И, первый вход первого элемента ИЛИ соединен с первым входом признака функции блока, второй и третий входы признака функции блока соединены с первым и вторым входами третьего элемента И и второго элемента ИЛИ, четвертый вхрд признака функции блока соединен с третьим входом второго элемента ИЛИ и вторым входом первЬго элемента ИЛИ,. первый вход первой группы входов блока соединен с входом четвертого элемента И, второй вход первой группы входов блока соединен со вторыми входами второго и четвертого элементов И и первым входом пятого элемента И, выход третьего элемента И соедийен с первым входом, а выход пер-. вого элемента ИЛИ - со вторым входом шестого элемента И, первый вход признака функции блока соединен с четвертым входом второго элемента ИЛИ и первым входом седьмого элемента И, первый вход второй группы входов блока соединен со вторым входом седьмого элемента И, второй вход второй группы входов блока соединен с третьим входом четвертого элемента И, третий вход второй группы входов блок соединен с четвертым входом четвертого элемента И и Первыми входами восьмого и дёвятого элементов И выходы седьмого и восьмого элементов -И соединены с первым и вторым входами третьего элемента ИЛИ соответственно, выходы четвертого и пятогоэлементов и соединены с первым и вторым входами четвертого элемента ИЛИ соответствённо, первая группа входов схемы сравнения кодов подклнэчена к третьей группе входов блока, а вторая групг па входов схемы сравнения кодов соединена fc входами: счетчика циклов, выход схемы сравнения кодов qoeдинен с входом установки в ноль .триггера, в торой вход первого элемента И. соединен с выходом генератора тактовых импульсов, а выход - со счетным входом счетчика тактов, выходы которого соединены с входами дешифратора тактов, первый выход которого соединен с пятым входом второго элемента ИЛИ, второй выход дешифратора тактов соединен с третьим входом ..третьего элемента И, третий выход j этого дешифратора соединен с третьим ;)входом шестого Элемента И, четвертый выход дешифратора тактов сое- . динен с. пятым входом четвертого элемента И, пятый и шестой выходы дешифратора тактов соединены с первым и втйрым входами пятого элемента ИЛИ .соответственно, седьмой выход дешифратора тактов Соединен с третьим входом седьмого элемента И, восьмой выход дешифратора тактов соединен со вторым входом пятого элемента И, девятый выход дешифратора тактов соеди нен с первьии входом шестого элемента ИЛИ, десятый выход дешифратора тактов соединен со вторыми входами восьмого и девятого элементов И,один надцатый выход дешифратора тактов соединен со вторым входом шестого элемента ИЛИ, четвертый вход седьмог элемента И подключен к выходу тригге ра, выходы второго элемента ИЛИ, вто рого и третьего элементов И, четвертого и пятого элементов ИЛИ, шестого восьмого и седьмого элементов И, шес того и третьего элементов ИЛИ подклй чены к первому - десятому входам.выходного регистра соответственно, пер . вый, второй и третий выходы которого соединены с первой группой выходов блока, четвертый выход выходного регистра соединен с первым выходом бло ка, пятый выход выходного регистра соединен со вторым выходом блока, шестой и седьмой выходы выходного ре гистра соединены со второй группой выходов блока, восьмой выход выходкого регистра подключен к третьему выходу блока и счетному входу счетчика циклов, девятый выход выходного регистра соединен с четвертым выходом блока, десятый выход выходного регист ра Соединен с пятым выходом блока. На фиг. 1 приведена структурная схема предлагаемого СП; на фиг. 2 структурная схема блока управления, i на фиг. 3 - схема сдвигателя на 4 разряда (на 8 разрядов схема выполняется аналогично); на фиг. 4 - схема входного регистра; на фиг. 5 - структурная схема счетчика порядка на фиг. 6 - структурная схема множительного устройства. Специализированный процессор фиг. 1) содержит входной регистр 1, счетчик 2 порядка, сдвигатель 3, первое ЗУ 4 коэффициентов аппроксимируюшего полинома, множительное устройство 5, сумматор 6, второе ЗУ 7 коэффициентов аппроксимирующего полинома, ЗУ 8 степени аппроксимирующего полинома, блок 9 управления, регистр 10 функции, группу элементов 11 И, выходной регистр 12. Блок 9 управления (фиг. 2) содержит генератор 13 тактовых импульсов, триггер 14, первый элемент 15 И, счетчик 16 тактов, дешифратор 17 тактов, счетчик 18 циклов, схему сравнения кодов 19, выходной регистр 20, второй - девятый элементы И 21-28 соответственно, элемент.29 НЕ, первый - пятый элементы ИЛИ 30-34 соответственно. Сдвигатель 3 (фиг.З) содержит :первый -девятый элементы И 35-43 (соответственно,первый - третий элементы ИЛИ 44-46 соответственно, деШИфратор 47, десятый элемент И 48. Входной регистр 1 (фиг. 4) содерЖит элемент 49 ИЛИ, одновибратор 50, регистр 51, группу элементов 52 ИЛИ. Счетчик 2 порядка (фиг. 5) содержит первую группу элементов 53 И, счетчик 54 и вторую группу элементов 55 И. Множительное устройство 5 (фиг.6) содержит группу элементов 56 ИЛИ и блок 57 перемножения. Структура и связи входного регистра 1, счетчика 2 порядка и сдвигателя 3 множительного устройства 5 аналогичны прототипу. Алгоритмы функционирования их не имеют отличий от алгоритмов аналогичных блоков прототипа. Процесс вычисления значений элементарнь1х функций, как и в прототипе, состоит иэ двух основных этапов: при- введение значений аргументов к стандартному интервалу вычисления (0,l)j вычисление значения полинома по схеме Горнера. Введение ЗУ 8 (см. фиг, i) неповлияло на процесс приведения аргументов к интервалу (0,1.} , поэтому он выполняется в предлагаемом устройстве так же, как ив прототипе 2. Вычисление значений полинома отличается от 2j переменным (в зависимости от вида элементарной функции И значения аргумента) количеством циклов сложение-умножение. Информация о требуемом количестве циклов, т.е о степени аппроксимирующего полино ма , для каждой конкретной функции каждом подинтервале разложения, ко рая предварительно заносится в ЗУ получается при решении задачи аппр симации элементарной.функдии на ЦВ известными методами. Максимальная требуемая разрядность вводимого ЗУ может быть определена из следующег выражения:. (еодГа мак)./ где R - разрядность ЗУ 8; CETL - наименьшее целое, больше или равное А; максимальная степень поли нома, определяемая по наи худ1иему случаю (из 1 . Для прототипа , тогда .; Максимальный объем ЗУ 8 , где S - разрядность старшего сегмен та кода аргумента, определяющая количество подинтер валов разложения (S определяет адресное пространство для ЗУ 8 и поступает на ад ресные входы со сдвигателя 3) ; - количество элемейтарных функций, рэалИзуемь1Х-процессором. В соответствии с кодами, записаннуми в ЗУ 8, возможны следующие, ситуации при вычислении полинома: R 000 - полином Нулевой степени, т.е. значения функции берутся непосредственно из таблицы, хранящейся в ЗУ 7, время вычисления значения элементарной-функций .равно вр мени предварительной обработки аргумента и выборки из ЗУ 7, т.е. )+ Tft. 001 - полином первой степени, т.е. р ajj+ , а время вычисления + Tgj+ ТУ+ Tj, , где Т- - врем выполнения операции умножения в ус ройстве 5; время выполнения операции сложения в сумматоре б. Я 010 - полином второ|1.степёни, т.е. X ха) J ln1;Tb + полином третьей степени-- ; Р-ОоХ 1 ад t4|Q2f 7 : T--Tg,tTfl 3|Tv4Tc / К 100 пЬлином четвертой ст.епени ; P-ao X|a1- X|a2; -УiQ,, .Т.-Тп.Тв + 41т,,Тс / I Я 101 - полином пятой степени IQ., ( |а,, х 1П1 + / в любом случае при ип .fiS процесс вычисления значения полинома начинается с выборки старшего коэффициента разложения о из ЗУ 4, подачи его на устройство 5, где он умножается на приведенное значение . аргумента, далее происходит суммирование со следующим коэффициентом . У выбранном во время выполнения операции умножения из ЗУ 7, на сумматоре б, после передачи суммы через регистр 10 функции и группу элементов 11 на множительное устройство 5 она умножается на значение приведенного аргумента К. Такой процесс продолжается до момента сравнения кондов, выбранных в первый момент из,, ЗУ 8, с кодом счетчика циклов в блоке управления 9, что свидетельствует о необходимости прекращения процесса вычисления. После этого значение элементарной функции записывается в выходной регистр 12 и выдается во внешнее устройство (в частном случае в ЦВЙ). Введение ЗУ 8 и его связи с блоком 9 потребовало внесения некоторых изменений в схему блока управления. В частном случае они сводятся к введению схемы сравнения кодов, которая легко реализуется сумматором по модулю 2, соединенной с выходами ЗУ 8 и выходами счетчика циклов в блоке 9. Выход схемы сравнения кодов несет : информацию о необходимости окончания процесса вычисления значений полинома (раньше для этой цели использовался импульс переполнения со счетчика циклов.; Блок 9 работает следующим образом. По сигналу Пуск, поступающему от командного процессора-, триггер 14 открывает элемент 15 И, и тактовые импульсы от ГТИ 13 поступают на вход счетчика 16. С выхода этого счетчику кодовые комбинации подаются на BXOJEI дешифратора 17, где дешифруются в соответствии с временными диаграм- . мами необходимые такты. Признаки функций, осведомительные сигналы и выделенные тактовые сигналы подаются на вход комбинационной схемы, реализованной на элементах 21-28 и элементах ИЛИ 30-34, которая форлдарует управляющие сигналы, noctyпающие через регистр 20 на в.ходы остальных блоков устройства и инициализирующие их функционирование. После каждого сигнала, осуществляющего разрешение передачи термов формулы Горнера на устройство 5, содержимое счетчика 18 увеличивается на единицу. Коды, поступающие с ЗУ 8 и счетчика 18 на схему сравнения кодов 19, сравйиваются последней и в момент их совпадения вырабатывается импульс Стоп, который устанавливает триггер 14 в состояние О, закрывающее элемент 15, и переписывает результат вычислений в выходной регистр 12 фиг. I), На

этом работа блока 9 заканчивается до поступления на вход процессора кодов аргумента, приэиака функции , и команды Пуск.

Входной регистр 1 работает следующим образqM.

Информация г поступающая на входы элементов 52 ИЛИ стробируетсй следующим образом: с выхода множительного устройства 5 - поступает только при наличии стробируемой информации на его входах/ с выхода, сумматора. 6 - аналогичноJ MX стробируется командным процессором, с KOTCJрого она подается во время обмена.

При появлении информации на вхо- дах группы элементов ИЛИ 52 она передается на информационные входы регистра 1. Одновременно срабатывает элемент 49 ИЛИ, обнаруживаю-, щий наличие информации на входе регистра 1 . Сигнал с выхода элемента 49 ИЛИ запускает одновибрауор 50, вырабатывакщий сигнал разрешения записи информацииь регистр. .

Разрядность введённого ЗУ 8 невелика (), а общий объем ЗУ 8 для S 10 Скак в прототипе) составляет менее 1,1% от суммарного объема ЗУ 4 и ЗУ 7, С другой стороны, введение ЗУ 8 приводит даже к сокращению объема памяти ЗУ 4 и ЗУ 7 по сравнению с прототипом, так как уменьшается количество хранимых в ЗУ 4 и ЗУ 7 коэффициентов большой разрядности ( у прототипа ; разрядность коэффициентов равна 56 для мантиссы и 8 для порядка) за счет уменьшения з начений степени полинома на отдельных подинтервалах разложения. Остальные узлы процессора не имеют специфических особенностей, реализуются на ртандарт,ных интегральных схемах по типовым техническим решениям, известным из лктературы, полностью аналогичны описанным в прототипе -,

: эффективность предложенного тех. нического Ъешейия можно оценить следуюшим образом. Пусть на входе процессора имеется непрерывный поток сигналов - заявок на вычисление значёний различных элементарных функций,реализуемых процессором. Тогда максимальная производительность прототипа. М

, VTB: 5tVTe; Для предлагаемого устройства

: --i; Минимальная производительность

i

П1

)

Cpeдjfяя производительность

„1- . . ;

I JU x v ;ypieTv- Tc)

где р - вероятность появления сиг(Налов -заявок на вычисление многочлена if-и степени Ci« 5).

Считают появление любой i-и заявки равновероятным. . В этом случае (Рцгр г 1/6)

, (T,,) выигрыш в средней производительности при использовании предлагаемого УСТРОЙСТВа

. - J l-Ail l±M±:10C M5t)

, п i(,) +5(Tj4T;.) Из анализа алгоритмов предварительной Обработки аргументов видно, что (Tj + %)(TC+ Т). При равенстве, т.е. в худшем случае, :Ь 1Л.

Таким образом, приУ,,, 5 средняя производительность предлагаемого специализированного процессора даже в худшем случае выше, чем у прото„на 0%.

., Пуск ПФ Л

КЗ- ми 8ате7ь (о§нвЩрагп ; ai4

i,.

Sff-S/fffx перенно ения

Фиг.6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3813529, кл | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Специализированный процессор | 1977 |

|

SU723581A1 |

Авторы

Даты

1983-06-15—Публикация

1981-05-18—Подача