(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления тангенса | 1984 |

|

SU1187162A1 |

| Устройство для вычисления функции @ ( @ - @ )/( @ + @ ) | 1982 |

|

SU1076911A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Устройство для вычисления функции ( @ - @ )/ @ | 1982 |

|

SU1076912A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1188750A1 |

| ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2513683C1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| УСТРОЙСТВО ДЛЯ НАХОЖДЕНИЯ ЭКСТРЕМУМА ФУНКЦИИ МЕТОДОМ ДИХОТОМИИ | 2002 |

|

RU2229742C2 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КООРДИНАТ | 1991 |

|

RU2007749C1 |

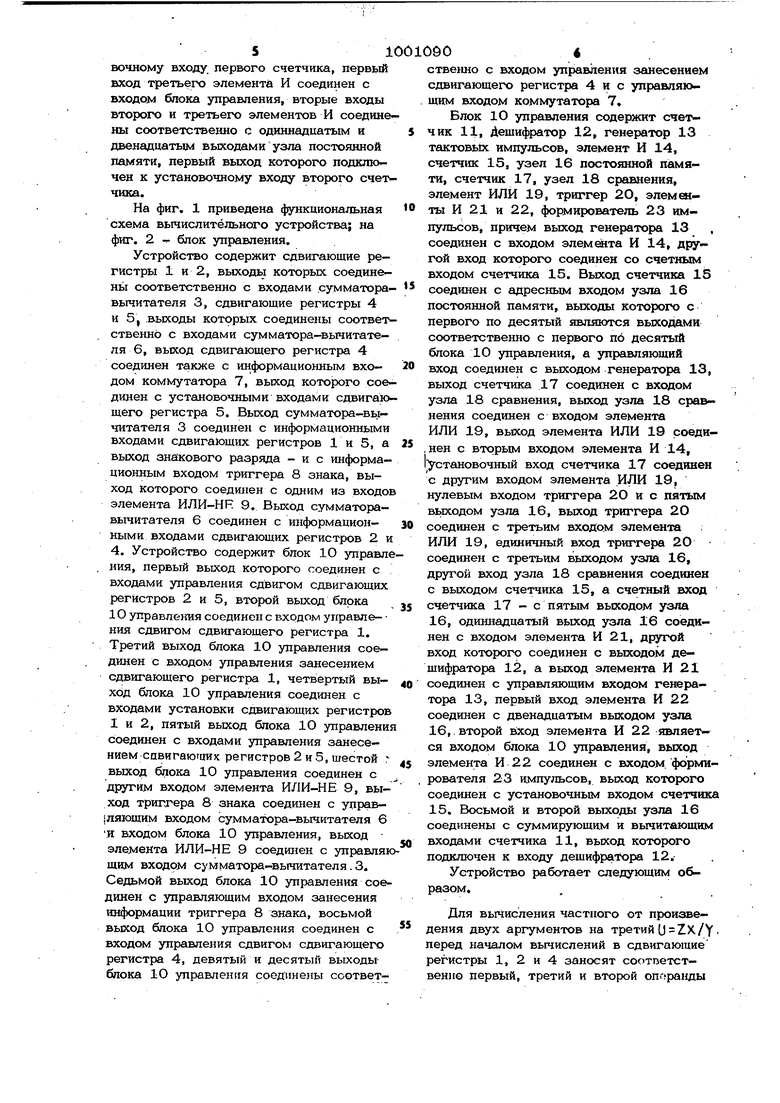

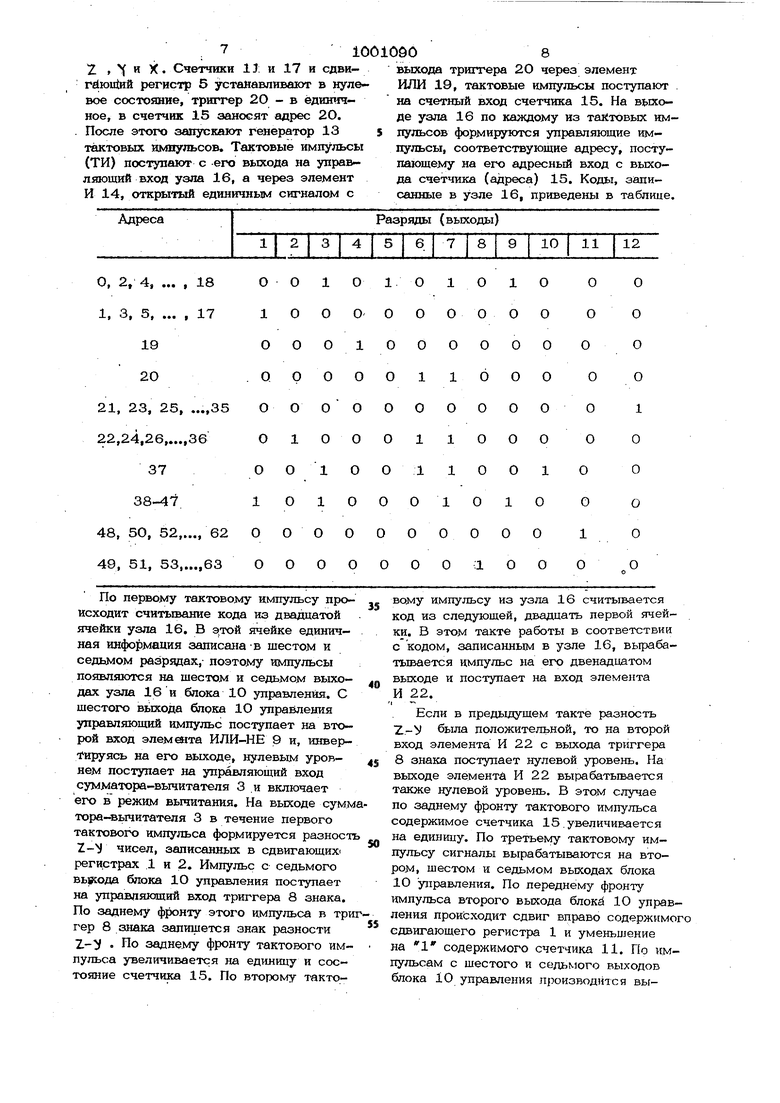

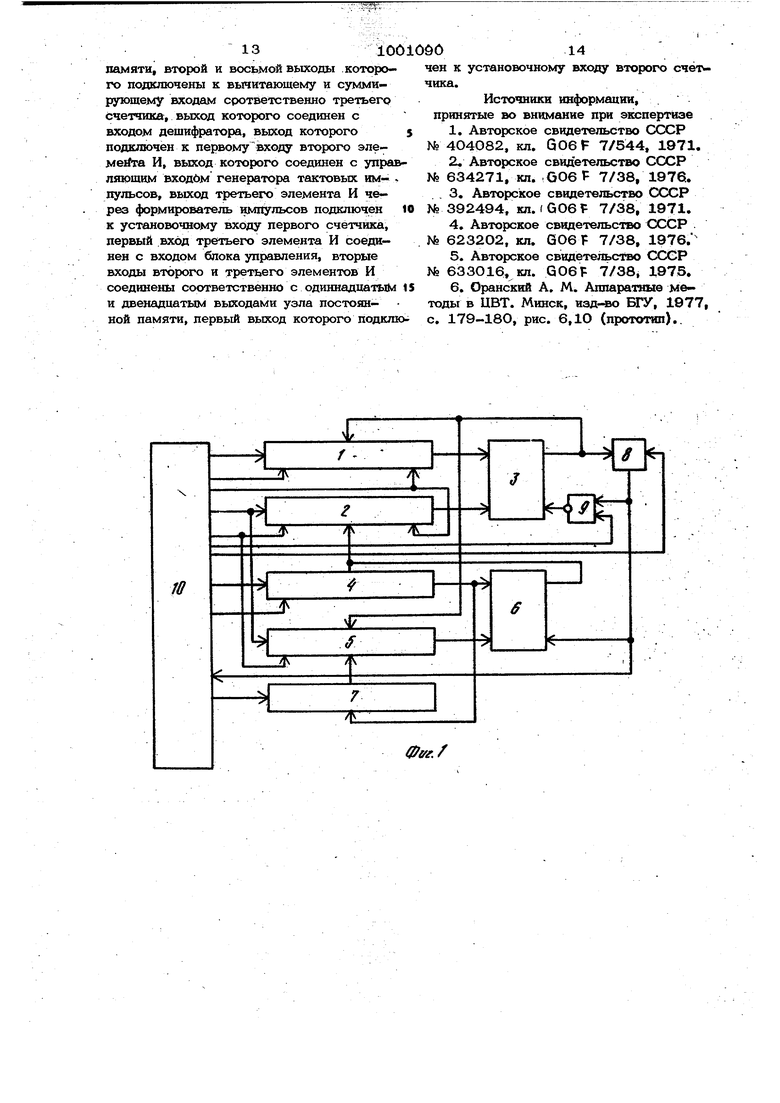

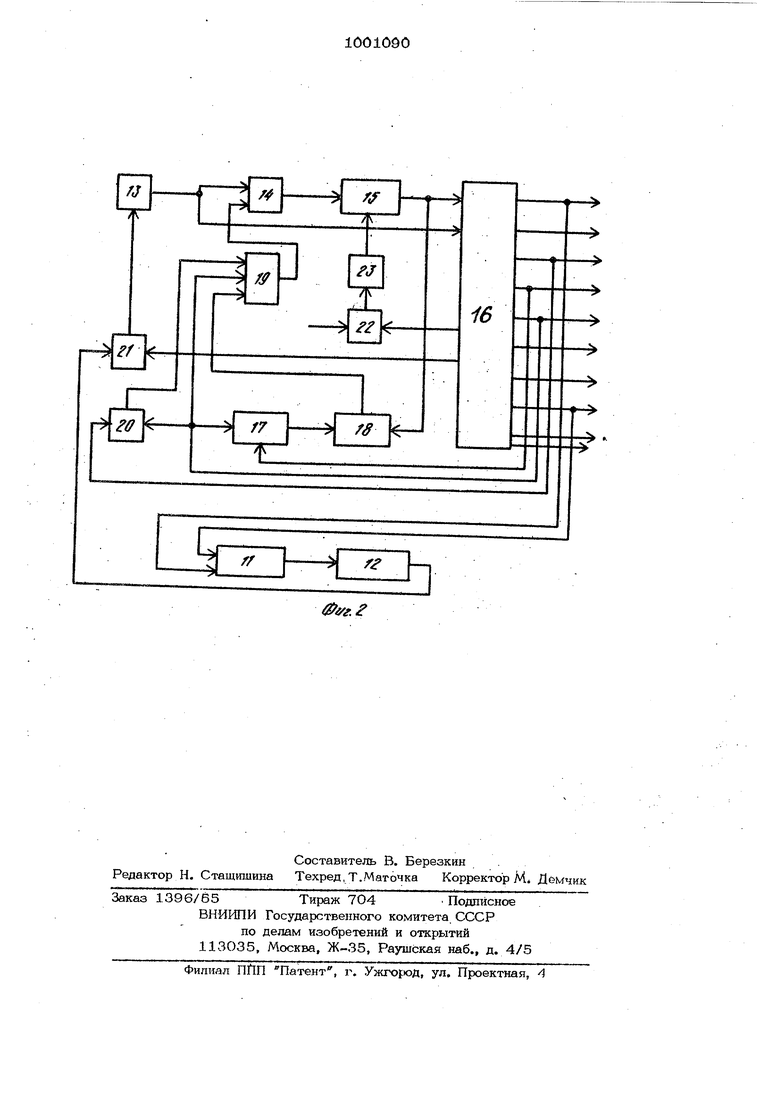

Изобретение относится к вычислительной технике и предназначено для вычисле ния модуля комплексного числа и вычисления частного от произведения двух аргументов на третий и может быть исполь зовано в автоматизированных системах цифровой-обработки сигналов. Известны вычислительные устройства для вычисления модуля комплексного чис 1. 2.31 и 4. Однако они не предназначены для вь1числения частного от произведения двух аргументов на третий и имеют сложную конструкцию. Кооме того, устройства LI и 2 вычисляют модуль комплексно числа,лишь с точностью до постоянного коэффициента. Известно вычислительное устройство для вычисления частного от произведения двух аргументов на третий, содержащее блок управления, пять сдвигающих регистров, три сумматора-вычитателя и блок анализа сходимости, содержащий узлы сравнения, триггеры и логические узлы 53 .. Однако это устройство имеет сложную конструкцию и не может использоваться для вычисления модуля комплексного чис-ла,.. Наиболее близким к предлагаемому является вычислительное устройство, осуществляющее умножение и деление, содержащее четыре сдвигающих регистра, два сумматора-вычитателя, триггер знака и узел управления, выходы первого и второго сдвигающих регистров соответственно соединены с первым и вторым, входами первого сумматора-вычитателя, вькод которого соединен с информационными входами первого сдвигающего регист ра и триггера знака, выходы третьего и четвертого сдвигающих регистров соединены соответственно с первым и вторым входами второго сумматора-вьпитателя, выход второго сумматора-вычитателя соединен с информационным входом тре- тьего сдвигающего регистра, выход триг гера знака соединен с управляющим входом второго сумматора-вычитателя, первый выход блока управления соединен с управляющим входом сдвшгчэв второго сдвигающего регистра бЗ . Известное устройство можно использовать для вычисления частного от произведения, двух аргументов на третий U-2X/Y только если третий аргумент Y больще или равен Половине первого аргумента Z . Кроме того, устройство не может выполнять операцию Ьычислени модуля комплексного числа. Цель изобретения - расщирение функциональных возможностей устройства за счет расширения области допустимых зне чений аргументов при вычислении част, ного от произведения двух аргументов на третий и возможности вычисления значения модуля комплексного числа. Поставленная цель достигается тем, что вычислительное устройство, содержащее сдвигаюише регистры, сумматорывьгчитатели, блок управления, триггер 31така, причем выходы первого и второго сдвигающих регистров соединены с информационными входами первого суммато ра-вычитателя, выход которого соединен с информационным входом первого сдвигающего регистра и информационным входом триггера знака, выходы третьего и четвертого сдеигаюших регистров соединены с информационными входами второго сумматора-вычитателя, выход которого соединен с информационным входом третьего сдвигающего регистра, выход триггера знака соединен с управляющим входом второго сумматора-вычитателя, первый выход блока управления соединен с входом управления сдвигом второго сдвигающего решстра, содержит элемент ИЛИ-НЕ, коммутатор, а блок управления содержит генератор тактовых импульсов, счетчики, элементы И, ИЛИ, триггер, дещифратор, узел сравнения, формирователь импульсов и узел постоянной памят выходы которого с первого по десятый являются соответствующими выходами блока управления, при этом выход элеме та ИЛИ-НЕ соединен с управляющим вхо дом первого сумматора-вычитателя, а входы - с выходом триггера знака и шестым выходом блока управления, выход третьего сдвигающего регистЕра соединен с информационным входом коммутатора, выход которого подключен к информационному входу четвертого сдвигающего регистра, выход второго сумматора-вычитателя соединен с информационным входом второго сдвигающего регистра, выход первого сумматора-вычитателя соединен с информационным входом четвертого сдвигающего регистра, первый выход блока управления соединен с входом управления сдвигом четвертого сдвигающего регистра, второй выход блока управления соединен с входом управления сдвигом первого сдвигающего регистра, третий выход блока управления соединен с входом управления занесением первого сдвигающего регистра, четвертый выход блока управления соединен с входами установки первого и второго сдвигающих регистров, пятый выход блока управления соединен с входами управления занесением второго и четвертого сдвигающих регистров, седьмой выход блока управления соединен с управляющим входом триггера знака, восьмой вьссод блока управления соединен с входом управления сдвигом третьего сдвигающего регистра, девятый выход блока управления соединен с входом управления занесением третьего сдвигающего регистра, десятый выход блока управления соединен с управляющим входом коммутатора, выход триггера знака соединен с входом блока управления, в котором выход генератора тактовых импульсов соединен с управляющим взводом узла постояйной памяти и с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика, выход которого соединен с адресным входом узла постоянной памяти и первым входом узла сравнения, второй вход которого соединен с выходом второго счетчика, счетный вход которого соединен с пятым выходом узла постоянной памяти, первым -входом триггера и первым входом элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, второй и третий входы элемента ИЛИ подключены соответственно к выходу узла сравнения и выходу триггера, второй вход которого соединён с четвертым выходом узла постоянной памяти, второй и восьмой выходы которого подключены к вычитающему и суммирующему входам соответственно третьего счетчика, выход которого соединен с входом дешифратора, выход которого подключен к первому входу второго элемента И, выход которого соединен с управляющим входом генератора тактовых импульсов, выход третьего элемента И через формирователь импульсов подключен к устаноБочному входу, первого счетчика, первый вход третьего элемента И соединен с входом блока управления, вторые входы второго и третьего элементов И соедине ны соответственно с одиннадцатым и двенадцатым выходами узла постоянной памяти, первый выход которого подключен к установочному входу второго счет чика. На фиг, 1 приведена функциональная схема вычислительного устройства; на фиг. 2 - блок управления. Устройство содержит сдвигающие регистры 1 и 2, выходы которых соединены соответственно с входами сумматора вычитателя 3, сдвигающие регистры 4 и 5, .выходы которых соединены соответ ственно с входами сумматора-вычитателя 6, выход сдвигающего регистра 4 соединен также с информационным входом коммутатора 7, выход которого сое динен с установочными входами сдвигаю щего регистра 5. Выход сумматора-вычитателя 3 соединен с информационными входами сдвигающих регистров 1 и 5, а выход знакового разр5ща - и с информационным входом триггера 8 знака, выход которого соединен с одним из входо элемента ИЛИ-HF 9. Выход сумматоравычитателя 6 соединен с информационными входами сдвигающих регистров 2 и 4. Устройство содержит блок 10 управл ния, первый выход которого соединен с входами управления сдвигом сдвигающих регистров 2 и 5, второй выход блока Ю управления соединен с входом управле- ния сдвигом сдвигающего регистра 1. Третий выход блока 10 управления соединен с входом управления занесением сдвигающего регистра 1, четвертый выход блока 10 управления соединен с входами установки сдвигающих регистров I и 2, пятый выход блока 1О управлени соединен с входами управления занесением сцвигаюгоих регистров 2 и 5, шестой выход блока 10 управления соединен с другим входом элемента ИЛИ-НЕ 9, выход триггера 8 знака соединен с унрав|ляюшим входом сумматора-вычитателя 6 И входом блока 10 управления, выход элемента ИЛИ-НЕ 9 соединен с управля щ14М ВХОД9М сумматора-вычитателя. 3. Седьмой выход блока 10 управления сое динен с управляющим входом занесения информации триггера 8 знака, восьмой выход блока 10 управления соединен с входом управления сдвигом сдвигающего регистра 4, девятый и десятый выходыблока 10 управления соед1ше}1ы соответстве шо с входом управления занесением сдвигающего регистра 4 и с управляющим входом коммутатора 7. Блок 10 управления содержит счетчик 11, Дешифратор 12, генератор 13 тактовых импульсов, элемент И 14, счетчик 15, узел 16 постоянной памяти, счетчик 17, узел 18 сравнения, элемент ИЛИ 19, триггер 20, элементы И 21 и 22, формирователь 23 импульсов, причем выход генератора 13 , соединен с входом элемента И 14, другой вход которого соединен со счетным входом счетчика 15. Выход счетчика 15 соединен с адресным входом узла 16 постоянной памяти, выходы которого с первого по десятый явл5аотся ВЫХОДАМИ соответственно с первого п6 десятый блока 10 управления, а управляющий вход соединен с выходом генератора 13, выход счетчика 17 соединен с входом узла 18 сравнения, выход узла 18 сравнения соединен с входом элемента ИЛИ 19, выход элемента ИЛИ 19 соеди- нен с вторым входом элемента И 14, установочньщ вход счетчика 17 соединен с другим входом элемента ИЛИ 19, нулевым входом триггера 20 и с пятым вьхходом узла 16, выход триггера 2О соединен с третьим входом элемента ИЛИ 19, единичный вход триггера 20 соединен с третьим выходом узла 16, другой вход узла 18 сравнения соединен с выходом счетчика 15, а счетный вход счетчика 17 - с пятым выходом узла 16, одиннадцатый выход узла 16 соединен с входом элемента И 21, другой вход которого соединен с выходом дешифратора 1, а выход элемента И 21 соединен с управляющим входом генератора 13, первый вход элемента И 22 соединен с двенадцатым выходом узла 16, второй вход элемента И 22 является входом блока 10 управления, выход элемента И 22 соединен с входом, формирователя 23 импульсов, выход которого соединен с установочным входом счетчика 15. Восьмой и второй выходы узла 16 соединены с суммирующим и вычитающим входами счетчика 11, выход которого подключен к входу дешифратора 12. Устройство работает следующим образом. Для вычисления частного от произведения двух аргументов на третий (J ZX/Y . перед началом вычислений в сдвигающие регистры 1, 2 и 4 заносят соответственно первый, третий и второй опг ранды

2 и X. Счетчики 13; и 17 и сдвиrdrouiHft регистр 5 усталавливают в нулевое состо5шие, триггер 20 - в ёдинтганое, в счетчик 15 заносят адрес 20. После этого запускают генератор 13 тактовых импульсов. Тактовые импульсы (ТИ) поступают с его выхода на управляющий вход узла 16, а через элемент И 14, открытый единичным сигналом с По первому тактовому импульсу про исходит считывание кода из двадцатой ячейки узла 16, В э,той ячейке единичная информация записала -в шестом и седьмом разрядах, поэтому импульсы появляются на щестом и седьмом выходах узла 16 и блока 1О управления. С щестого выхода блока 10 упрайления управляющий импульс поступает на второй вход элемв1та ИЛИ-НЕ 9 и, инвертируясь на его выходе, нулевым уровнем поступает на управляющий вход сумматора-вычитателя 3 .и включает его в режим вычитания. На выходе сум тора-вь1читателя 3 в течение первого тактового импульса формируется разност Z- чисел, записанных в сдвигающих регистрах 1 и 2. Импульс с седьмого вь1|Кода блока 1О управления поступает на управляиощий вход триггера 8 знака. По заднему фронту этого импульса в тр гер 8 знака запишется знак разности Z-V . По задне.му фронту тактового импульса увеличивается на единицу и состояние счетчика 15. По второму тактовыхода триггера 20 через элемент ИЛИ 19, тактовые импульсы поступают на счетный вход счетчика 15. На выходе узла 16 по каждому из тактовых импульсов формируются управляющие импульсы, соответствующие адресу, поступающему на его адресный вход с выхода счетчика (адреса) 15. Коды, записанные в узле 16, приведены в таблице. вому импульсу из узла 16 считывается код из следующей, двадцать первой ячейки. В этом такте работы в соответствии скодом, записанным в узле 16, вырабатывается кмпульс на его двенадцатом выходе и поступает на вход элемента И 22. Если в предыдущем такте разность 21-V была положительной, то на второй вход элемента И 22 с выхода триггера 8 знака поступает нулевой уровень. На выходе элемента И 22 вырабатывается также нулевой уровень, В этом случае по заднему фронту тактового импульса содержимое счетчика 15. увеличиваете я на единицу. По третьему тактовому импульсу сигналы вырабатываются на втором, шестом и седьмом выходах блока 10 управления. По переднему фронту импульса второго выхода блоки 1О управления происходит сдвиг вправо содержимого сдвигающего регистра 1 и уменьшение на I содержимого счетчика 11. По импульсам с шестого и седьмого выходов блока 10 управления производ пся вычисление разности .) и занесение знака разности в триггер 8 знака. Коды в ячейках 23-26 узла 16 и вьшолняемые по этвди кодам операции повторяют коды и операции из двадцать первой и двадцат второй ячеек узла 16. В случае, если при вьшолнении коман из ячеек 21, 23, 25 ... ,35 узла 16 на второй вход элемента VI 2.2 с выхода триггера 8 знака поступает единичный .сигнал, то с двенадцатого вькода узла 16 на вход формирователя 23 импульсов проходит управляющий импульс, по задне му фронту которого формируется импульс на выходе 23 формирователя. Этот импульс записывает в счетчик 15 число 37. В этом случае по следующему тактовому импульсу выполняется команда из тридцать седьмой ячейки узла 16. По этой команде вычисляется и записыг.ается в сдвигающий регистр 1 разност j3jj 2yy,V , а в сдвигающий регистр 5 переписывается число из сдвигающего регистра 4. Далее по командам из ячеек 38-47 узла 16 производится вьр1исление величины {jU-Zv7)X/VB соответствии с алгорит мом л-.. q.. - 51§:и CTi) .Ti-cv Vi- . При этом в результате выполнения программы из ячеек 20-36 узла 16, не зависимо от величины аргументов Ч и Z записанных в сдвигающие регистры 1 и 2 перед пуском устройства, обеспечивается соотношение , явл5пошееся достаточным условием сходимости выбранного алгоритма. Поэтому в предлагаемом устройстве обеспечивается вы. числение операции U-Zx/Y независимо от величины-аргументов X, Y , Z Поело выполнения алгоритма (1) величина U записана в сдвигающем регистре 4. Для получения результата О-ZX/ - бобходимо умножить число и на целую степень двух. По командам, .записанным в ячейках 48-63 узла 16 вьшолняется сдвиг числа U влево на столько разрядов, на сколько было сдвинуто число Z при выполнении команд из ячеек 2О-36 узла 16. При каждом сдвиге -на один разряд увслич тается на единицу содержимое счётчика 11. В с гучае равенства содержимого счетчика нулю, на выходе дешифратора 12 вырабатывается единичный сиптал, открываю- щий элемент И 21. При выполнении очередной команды из ячеек 48, 50, 52,..., 62 узла 16 управляющий щипульс с его одиннадцатого выхода проходит ерез открытый элемент И 21 на вход генератора 13 и переводит егов состояние Останов. После этого в третьем сдвигающем регистре 4 записан результат от деления произведения двух аргументов на третий 13 - Zx/Y .. Для вычисления модуля комплексного числасэ Хчч необходимо записать в сдвигающ 1е регистры 1 и 5 число Y в в сдвигающие регистры 2 и 4 - число Jf, установить в нулевое состояние триггер знака, счетчики 11 и 15 и запустить генератор тактовых Импульсов 13. После этого по программе, записанной в ячейках 0-19 узла 16, выполняется алгоритм вычисления величины Q в соответствии с алгоритмом: X; ,X-+a-v-2 i-t-t 1. f 1 i .u.-S e-ncvu,) Коэффициент Q определяется выражениемq--jS ViTr j-i,(i,vДля выполнения алгоритма (2) команды из ячеек узла 16 с нечетными номерами 3, 5, ... , 17 должны выполняться соответственно два, три, ... , девять раз. Это обеспечивается тем, что каждый раз при выполнении команд из ячеек узла 16 с четным номером 2, 4 ... , 16 импульс с пятого выхода узла 16 уставав. ливает в нулевое состояние триггер 2О и счетчик 17. При выполнении следующей по счету команды из ячейки узла 16 с нечетным номером на все входь элемента ИЛИ 19 поступает нулевой Уровень, элемент И 14 закрыт нулевым уровнем с выхода элемента ИЛИ 19, поэтому содержимое счетчика 15 не увеличивается. При выполнении этих команд импульсом с Первого выхода узла 16 увеличивается содержимое счетчика 17 до тех пор, пока оно не сравняется с числом, поступающим на второй вход узла 18 сравнения. Требуемое количество повторений команды обеспечивается тем, что ко второму входу узла 18 сравнения подключены все разряды счотчика 15, кроме младшего. Сигнал сравнения с выхода узла 18 сравнени через ИЛИ 19 и элемент И 14, открытыГ тактовым импульсом, поступает на счетный вход счетчика 15 и обеспечивает переход к вьшолнению следующей команды. После вьшолнения командь из восем-надцдтой ячейки узла 16 в сдвигающем регистре 4 будет записано яислорУ( Для получения точного значения результа по команде из ячейки 19 узла 16 в сдви гающие регистры 1 и 2 по установочным входам записываются числа соответствен но 1 и О. Далее вьтолняется алгоритм (1) q начальными условиями ZQ 1 X . , после выполнения которого получаем в сдвигающем регистре 4 модуль комплексного числа C|rVX 4C2 Таким образом, предлагаемое устройство позволяет вычислять множительно- делительную операцию при любых значеHH5IX аргументов и точное значение модуля комплексного числа. .Формула изобретения Вьгчислительное устройство, содержащее сдвигающие регистры, сумматорывычитатели, блок управления, триггер знака, причем выходы первого и второго сдвигающих регистров соединены.с информационным входами, первого су.мматор вычитателя, выход которого соединен с информационным входом первого сдвигающе1 о. регистра и информациоШ1ым входом триггера знака, выходы третьего и четвертого сдвигающих регистров соединены с информационными входами второго сумматора-вычитателя, выход которого соединен с информационным .входом треть его сдвигающего регистра, выход триггера знака соединен с улравляоощим входом второго сумматора-вычитателя, первый выход блока управления соединен с входом управления сдвигом второго сдвигающего регистра, отличающеес я тем, что, с целью расширения функциональных возможностей устройства за счет расширения области. допустимых значений аргументов при вычислении частног от произведения двух аргументов на третий и возможности вычисления значения модуля комплексного числа, оно содержит элемент ИЛИ-НЕ, коммутатор, а блок зшравления содержит генератор тактовых импульсов,, счетчики, элементы. И, ИЛИ, триггер, дешифратор,, узел сравнения, формирователь импульсов и узел постоянн памяти, вькоды которого с первого по 10 QO12 десятый являются соответствующими выходами блока управления, при этом выход элемента ИЛИ-НЕ соединен с управлякшшм входом первого сумматора-вычитателя, а входы - с выходом триггера знака и шестым выходом блока управления, выход третьего сдвигающего регистра соединен с информационным входом коммутатора, выход которого подключен к информационно.му входу четвертого сдвигающего регистра, выход второго сумматора-вычитателя соединен с информационным входом второго сдвигающего регистра, выход первого сумматора-вычитателя соединен с информационным входом четвертого сдвигающего регистра, первый выход блока управления соединен с входом управле гая сдвигом четвертого сдвигающего регистра, второй выход блока управления соединен с входом управления сдвигом первого сдвигающего регистра, третий выход блока управления соединен с входом управления занесением первого сдвигающего регистра, четвертый выход блока управления соединен с входами установки первого и второго сдвигающих регистров, пятый выход блока управления соедш1ен с входами управления занесением второго и четвертого сдвигающих регистров, седьмой выход блока управления соединен с управляющим входом триггера знака, восьмой выход блока управления соединен с входом управления сдвигом третьего сдвигающего регистра, девятый выход блока управления соединен с входом управления занесением третьего сдвигающего регистра, десятый выход блока управления соединен с управляющим входом коммутатора, выход триггера знака соединен с входом блока управления, в котором выход генератора .тактовых импульсов соединен с управляющим входомузла постоянной памяти и с первым входомпервого элемента И,выход Которого соединен со счетным входом первого счетчика, выход которого соединен с адресным. входом узла постоянной памяти и первым входом узла сравнения, второй вход которого соединен с выходом второго счетчика, счетный вход которого соединен с пятым выходом узла постоянной памяти, первым входом триггера и первым входом элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, второй и третий входы элемента ИЛИ подключены соответственно к выходу узла сравнения и выходу триггера, второй вход которого соединен с четвертым выходом узла постоянной

шиияти, второй и восьмой выходы которого подключены к вычитающему и суммирующему входам соответственно третьего счетчика, выход которого соединен с входом дешифратора, выход которого$

подключен к первому входу второго элеMetfra И, выход которого соединен с управляюшши входбм генератора тактовых им- . пульсов, выход третьего элемента И через формирователь импульсов подключен 10 к установочному входу первого счетчика, первый вход третьего элемента И соединен с входом блока управления, вторые входы второго и третьего элементов И соединены соответственно с одиннадцатым 15 и двенадцатым выходами узла постоян- ной памяти, первый выход которого подклк чен к установочному входу второго счёт. чика.

Источники информации, принятые во вн1шание при экспертизе

. , 3. Авторское свидетельство СССР № 392494, кл. ( G06 7/38, 1971.

&г.

Авторы

Даты

1983-02-28—Публикация

1980-07-23—Подача