(54) ПРОГРАММИРУЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый делитель частоты | 1980 |

|

SU871340A2 |

| Каскад программируемого делителя частоты | 1980 |

|

SU919091A1 |

| Программируемый делитель частоты | 1975 |

|

SU621099A1 |

| Программируемый делитель частоты | 1977 |

|

SU696611A2 |

| Электростимулятор мышечного насоса крови | 1989 |

|

SU1704791A1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1328937A1 |

| Устройство для управления шаговым двигателем | 1986 |

|

SU1365342A1 |

| Счетчик импульсов с переменным коэффициентом счета | 1978 |

|

SU783998A2 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1248062A1 |

| Делитель частоты | 1982 |

|

SU1019644A1 |

Программируемый делитель частот относится к устройствам импульсной техники, используемым в радиотехнической аппаратуре различного назначения, в частности в синтезаторах частот.

По основному авт. св. 621099 известен программируемый делитель частоты, который содержит N одинаковых каскадов, каждый из которых состоит из управляемого делителя, блока автономной установки, элемента совпадения и дополнительного элемента совпадения. Тактовый вход управляемого делителя соединен с первым входом блока автономной установки, а первый выход - со вторым входом блока автономной установки. Выход блока автономной установки подключен к третьему входу блока автономной установки предыдущего каскада и к одному из входов элемента совпадения, на второй вход которого подается управляющий сигнал. Выход этого элемента совпгщения подключён к гстановочному входу управляемого делителя. Второй выход управляемого делителя через дополнительный элемент совпгшения соединен с тактовым входом управляемого делителя следующего каскада. Кроме того, инЕерснйП выход блока автономной установки соединен со вторым входом дополнительного элемента совпадения 1.

Недостатком известного устройства является высокое энергопотреР5ление.

Цель изобретения - снижение знергопотребления программируемого дели0теля частоты.

Поставленная цель достигается тем, что в каждый каскад программируемого делителя частоты, содержащий управляемый делитель, блок автоном5ной установки и два элемента совпадения, введен блок запрета, первый вход которого соединен с выходом блока автономной установки, второй вход - с третьим выходом управляемо0го делителя, а выход - со вторым входом дополнительного элемента совпадения и с четвертым входом блока автономной установки.

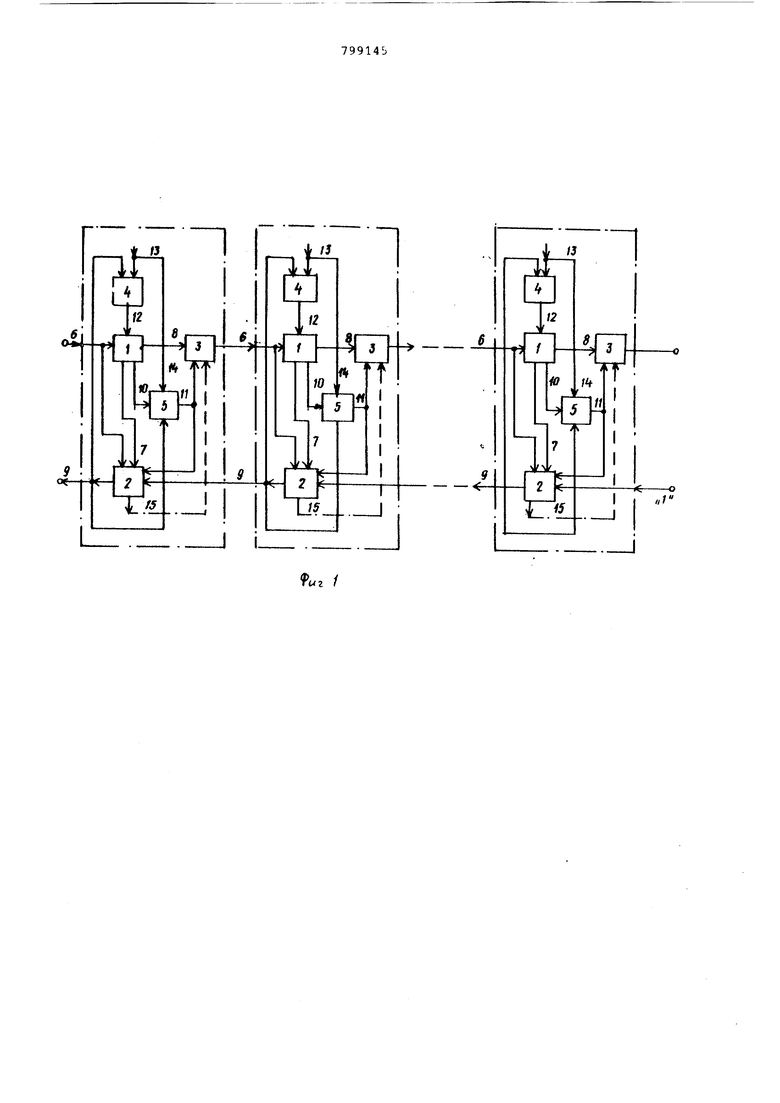

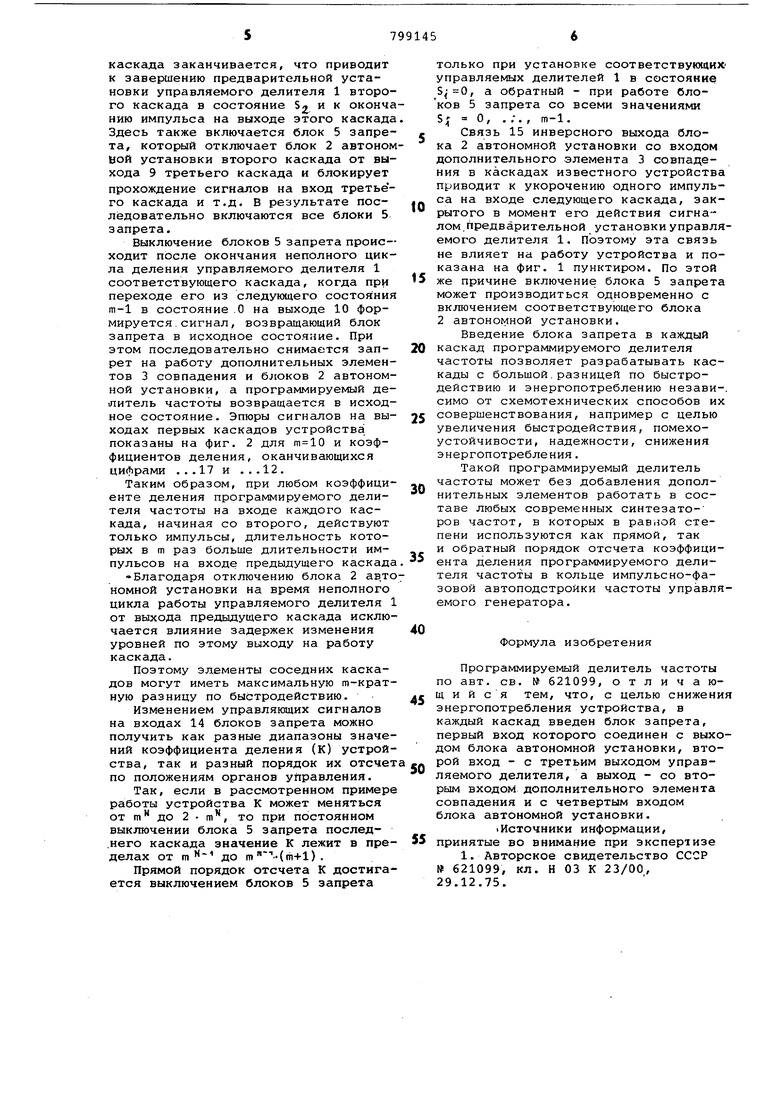

На фиг. 1 представлена функцио5НсШьНая схема программируемого делителя частоты; на фиг. 2 - эпюры синалов на входах первых каскадов программируемого делителя частоты.

Программируемый делитель частоты (см. фиг. 1) содержит N одинаковых каскадов, каждый из которых состоит из управляемого делителя 1 (например декадного типа), блока 2 автономной установки, дополнительного элемента 3 совпадения, элемента 4 совпадения и блока 5 запрета. Входом каждого каскада является тактовый вход б управляемого делителя 1, соединенный с первым входом блока 2 автономной установки. Выходом каскада служит выход дополнител ного элемента 3 совпадения, соединенный со входом 6 следующего каска да. Первый выход 7 управляемого дели теля 1 подключен ко второму входу блока 2 автономной установки, а вто рой выход 8 - к одному из входов до полнительного элемента 3 совпадения Выход 9 блока 2 автономной установк соединен с первьлм входом блока 5 запрета, с одним из входов элемента 4 совпадения и с третьим входом бло ка 2 автономной установки предыдуще коскада. Третий выход 10 управляемо го делителя 1 соединен со вторым входом блока 5 запрета, выход 11 ко торого подключен к четвертому входу блока 2 автономной установки и ко второму входу дополнительного элемента 3 совпадения. Установочный вход 12 управляемого делителя 1 соединен с выходом элемента 4 совпаде ния, на -второй вход 13 которого под ется управляющий сигнал. Управляющи сигнал может также подводиться к третьему входу 14 блока 5 запрета для его включения или выключения. Входом программируемого делителя частоты является вход 6 первого кас када, а выходом - выход 9 любого каскада. Элемент 4 совпадения является обобщенным элементом и может состоять из нескольких элементов совпадения, выходы которых С9единены, например, с информационными входами соответствующих триггеров управляемого дели теля 1, а один из входов - с выходом 9 блока 2 -автономной установки. Управляющие сигналы на остальных входах 13 этих элементов совпадения определяют состояние предваритель ной установки управляемого делителя 1 (здесь i-порядковый номер каскада от входа устройства). В управляемом делителе 1 выход 7 имитирует выделение одного из т его состояний например, состояние т-1, К выходу 8 подключен выход триггера управляемого делителя 1, формирующего импульсы длительность которых в m раз (при: четном т) больше длительности импульсов на входе каскада. По выходу 10 формируется сигнал выключения блока 5 запрета при переходе управля емого делителя 1 из состояния m-l в состояние О. Программируемый делитель частоты работает следующим образом. Пусть на третьем входе блока 2 автономной установки последнего каскада и на входах 14 блоков 5 запрета всех каскадов действует постоянный логический уровень 1 (в дальнейшем просто 1 или 0), разрешающий включение этих блоков. В исходном состоянии блоки 2 автономной установки, элементы 4 совпадения и блоки 5 запрета - выключены, а дополнительные элементы 3 совпадения - включены: на выходах 9,12 -О, на выходах 11 - 1. Управляемый двигатель 1 последнего каскада находится в состоянии 0. Состояния управляемых делителей 1 остальных каскадов и логические уровни на их выходах 7, 8 и 10 - произвольны. Каждый из N-1 каскадов начинает работать в режиме постоянного деления в m раз частоты входных импульсов. Форма сигналов на их входах б повторяет форму импульсов, на выходы 8 управляемых делителей 1 предьщущих каскадов и на вход последнего каскада поступают импульсы длительностью в раз больше длительности импульсов на входе первого каскада, которые переводят управляемый .делитель 1 N-ro каскада в состояния 1, 2 и т.д. С переходом этого управляемого делителя 1 в состояние т-1 появляется 1 на соответствующих выходах 9 и 12 и начинается предварительная установка его в состояние S(j. Подготавливается к включению (или включается) блок 5 запрета последнего каскада и снимается запрет на включение блока 2 автономной установки предыдущего (N-l)-ro каскада. Аналогичные процессы происходят затем последовательно в (N-l)-OM, (N-2)-OM,..., первом каскадах после перехода их управляемых делителей в состояние т-1. На выходе 9 первого каскада появляется выходной импульс программируемого делителя частоты. Завершение предварительной установки управляемых делителей 1 происходит в обратном порядке: от перВ9ГО каскада к последнему. С окончанием тактового импульса на входе первого каскада, соответствующего состоянию т-1 его управляемого делителя 1, на выходах 9 и 12 появляется 0. Импульс на выходе первого каскада заканчивается. Управляемый делитель 1 переходит в состояние S. Включается блок 5 запрета. ровень О на его выходе отключает блок 2 автономной- установки первого каскада от выхода 9 второго каскада и блокирует прохождение сигналов через дополнительный элемент 3 совпадения. Импульс на входе второго каскада заканчивается, что приводит к завершению предварительной установки управляемого делителя 1 второго каскада в состояние $2 и к оконча нию импульса на выходе этого каскада Здесь также включается блок 5 запрета, который отключает блок 2 автоном ной установки второго каскада от выхода 9 третьего каскада и блокирует прохождение сигналов на вход третьего каскада и т.д. В результате последовательно включаются все блоки 5 запрета. Выключение блоков 5 запрета происходит после окончания неполного цикла деления управляемого делителя 1 соответствующего каскада, когда при переходе его из следующего состояния т-1 в состояние .0 на выходе 10 формируется, сигнал, возвращающий блок запрета в исходное состояние. При этом последовательно снимается запрет на работу дополнительных элементов 3 совпадения и блоков 2 автономной установки, а программируемый делитель частоты возвращается в исходное состояние. Эпюры сигналов на выходах первых каскадов устройства показаны на фиг. 2 для и коэффициентов деления, оканчивающихся цифрами ...17 и ...12. Таким образом, при любом коэффициенте деления программируемого делителя частоты на входе каждого каскада, начиная со второго, действуют только импульсы, длительность которых в m раз больше длительности импульсов на входе предыдущего каскада Благодаря отключению блока 2 ав.то номной установки на время неполного цикла работы управляемого делителя 1 от выхода предыдущего каскада исключается влияние задержек изменения уровней по этому выходу на работу каскада. Поэтому элементы соседних каскадов могут иметь максимальную т-кратную разницу по быстродействию. Изменением управляющих сигналов на входах 14 блоков запрета можно получить как разные диапазоны значений коэффициента деления (К) устройства, так и разный порядок их отсчет по положениям органов уйравления. Так, если в рассмотренном примере работы устройства К может меняться от т до 2 т, то при постоянном выключении блока 5 запрета послед.него каскада значение К лежит в пределах от до m -(in+l) Прямой порядок отсчета К достигается выключением блоков 5 запрета только при установке соответствующих управляемых делителей 1 в состояние) , а обратный - при работе блоков 5 запрета со всеми значениями 5 О, .;., т-1. Связь 15 инверсного выхода блока 2 автономной установки со входом дополнительного элемента 3 совпадения в каскадах известного устройства приводит к укорочению одного импульса на входе следующего каскада, закрытого в момент его действия сигналом.предварительной установки управляемого делителя 1. Поэтому эта связь не влияет на работу устройства и показана на фиг. 1 пунктиром. По этой же причине включение блока 5 запрета может производиться одновременно с включением соответствующего блока 2 автономной установки. Введение блока запрета в каждый каскад программируемого делителя частоты позволяет разрабатывать каскады с большой.разницей по быстродействию и энергопотреблению незави-. симо от схемотехнических способов их совершенствования, например с целью увеличения быстродействия, помехоустойчивости, надежности, снижения энергопотребления. Такой программируемый делитель частоты может без добавления дополнительных элементов работать в составе любых современных синтезаторов частот, в которых в рав.1Ой степени используются как прямой, так и обратный порядок отсчета коэффициента деления программируемого делителя частоты в кольце импульсно-фазовой автоподстройки частоты управляемого генератора. Формула изобретения Программируемый делитель частоты по авт. св. № 621099, отличающийся тем, что, с целью снижения энергопотребления устройства, в каждый каскад введен блок запрета, первый вход которого соединен с выходом блока автономной установки, второй вход - с третьим выходом управляемого делителя, а выход - со вторым входом дополнительного элемента совпадения и с четвертым входом блока автономной установки. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 621099, кл. Н 03 К 23/00, 29.12.75.

Авторы

Даты

1981-01-23—Публикация

1979-01-05—Подача