1

Изобретение относится к импульсной технике.

В основном авторском свидетельстве № 621099 описан программируемый делитель частоты, содержащий N каскадов, каждый из которых содержит управляемый делитель частоты, блок автономной установки делителя частоты., два двухвходовых логических элемента И, выход одного из которых соединен со входом управляемого делителя частоты последующего каскада ij

Недостатком данного дел;ггеля частоты является недостаточное быстродействие.

Целью изобретения является повышение быстродействия.

Поставленная цель достигается тем, что в делитель частоты, содержащий N каскадов, каждый из которых содержит управляемый делитель частоты, блок автономной установки делителя частоты, два двухвходовых логических элемента И, выход одного из которых соединен со

ВХОДОМ управляемого делителя частш-ы последующего каскада, в каждый каскад введен трехвходовый логический элемент И, первый вход которого соединен с дополнительным выходом управляемого делителя частоты, второй вход соединен с первым выходом блока автономной установки делителя частоты данного каскада, второй вход которого соединен с выхо« дом упомянутого тре Аходового логического элемента И, а третий вход упомянутого трехвходового логического элемента подключен ко второму выходу блока автономной установки делителя частоты последующей ячейки

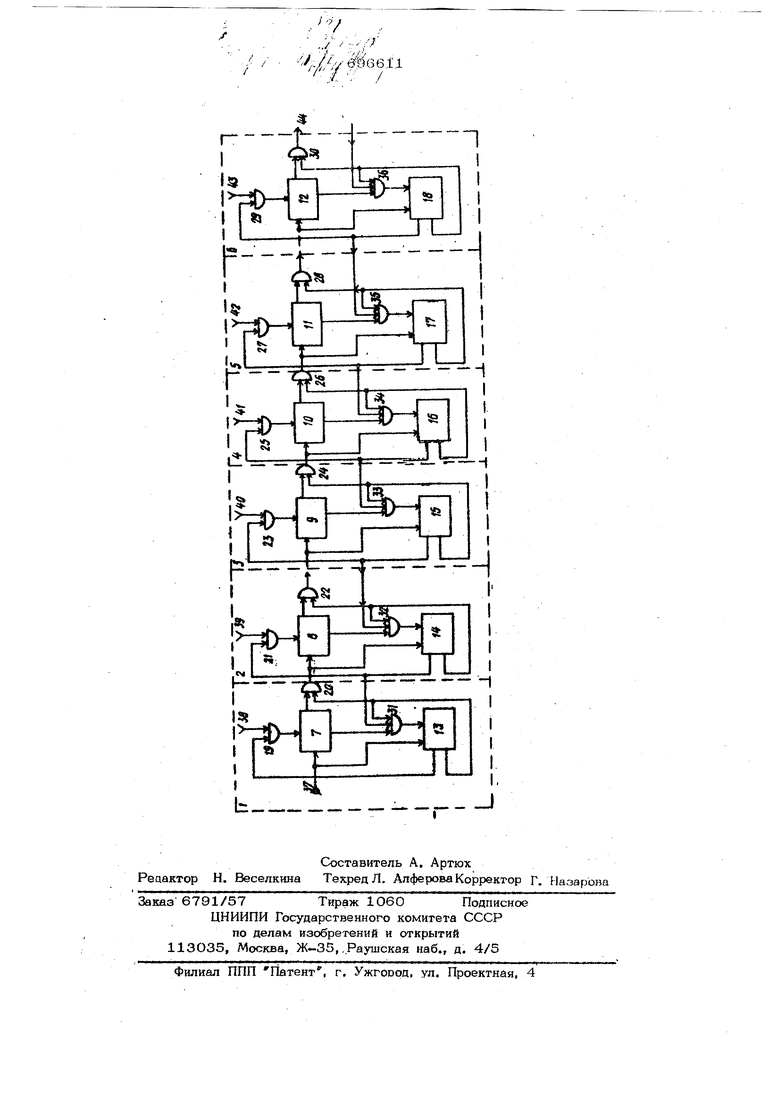

Структурная электрическая схема делителя частоты праведена на чертеже.

Делитель частоты содержит N идентичных каскадов 1-6, состоящих на управляемых делителей частоты 7-12, блоков автономной установки делителей частоты 13 - 18, двухвходовых логических элементов И 19 - 30 и трехвходовых логических элементов И 31 - 36. Входной сигнал подай на входную шину 37. На шины 38 - 43 поданы сигналы управления. Выходной сигнал снимается с выхода 44, Принцип работы делителя заключается в следующем. Программируемый делитель частоты работает следующим образом. Пусть требуется коэффициент деления N . Пдя этого в делитель, максимальная емкость которого равна tri , необходимо записать число Z , равное кц N . Тогда с поступлением на вход N импул сов произойдет заполнение делителя, цикл деления завершится и на выходе сформируется выходной импульс. Пусть N. q Vn°-v0 ш-...q.i-i:., + где ,1,2,.., тогда Z -(m-a hi+(vn-l-c 2 --...-b(hi--|-ol -) , т. е. в первый каскад необходимо записать число, являющееся дополнением до Vn, а в остальные - числа, являющиеся дополнениями до m -1. Например, для слу чая декадных делителей, т. е., когда п .1О, необходимо получить N 253. В этом случае требуется три каскада, максимальная емкость равна 1О - 1ООО, а N 1ООО-253 747, . е. в первый каскад необходимо предварительно записать .7, во второй - 4, в третий - 7. Динамика работы рассматривается на примере работы первого каскада дели теля для случая, когда N в младшем разряде содержит единицу (наиболее слож ный случай). Тактирующим фронтом для триггеров (не показаны) делителей является отрицательный фронт тактового импульса, а для блоков 13-18 передний, что соответствует практике. Рассмотрим состояние делителя перед приходом (N - 1) импульса в цикле де ления. На выходе делителя 7 , так как он находится в состоянии 8. На другом его выходе - 1, поскольку с приходом ( М- 2)° импульса последний триггер (не показан) управляемого делителя 7 лереходит в состояние I. На выходе блока 14 -1, поскольку в следующих каскадах импульс установки С( мировался и продолжается. На инверсном выходе блока 14.- , которая присутствует постоянно, исключая время, равно длительности установки первого каскада. На прямом выходе блока 13 -О. С поступлением отрицательного тактирующего фронта импульса этот делитель переходит в состояние 9 и на его выходе появляется , которая вызывает совпадение в логическом элементе И 31, в результате через время задержки включения делителя и логического элемента И 31 на Д-входе блока 13 автономной установки появляется 1 и он готов к переключению, которое происходит с поступлением на его тактовый вход переднего фронта тактового импульса. В результате срабатывания данно4 о блока 13 на его выходах через соответствующее время задержки появятся соответственно сигналы и О. Первый является импульсом установки управляемого делителя первого каскада и через логический элемент И 19 в соответствии с управляющим сигналом на щине 38 прикладывается к установочным входам делителя 7 и устанавливает его в необходимое для формирования требуемого коэффициента деления состояние. Появление на инверсном выходе блока 13 О вызывает окончание импульса на выходе логического элемента И 31 и появление на информационном входе блока 13 автономной установки О. Кроме того, это вызывает появление отрицательного перепада на выходе логического элемента И 20, т. е. формируется последний в цикле деления тактирующий перепад на входе ВТОРОГО каскада. Отрицательный фронт тактирующего фронта не вызывает изменений в состоянии первого каскада, поскольку он накрыт импульсом установки исходного состояния управляемого делителя. С появлением переднего фронта первого импульса- в цикле деления блок 13 переключается, переводя сигнал на выходах в противоположное состояние. На этом оканчивается импульс установки управляемого делителя первого каскада, на выходе логического элемента И 20 формируется передний фронт первого тактирующего импульса для второго каскада и, следовательно, оканчивается импульс установки на втором каскаде, снимая единичный сигнал со входа логического элемента И 31. Отрицательный фронт первого тактирующего импульса переведет делитель первого каскада в нулевое состояние ОбОО), в результате на выходе делителя 7 появится О, который лередается логическим элементом И 2О на вход второго каскада. Это будет первый такти5Oрукиций фронт на входе второго каскада, к приёму которого он г-отов, так как импульс его установки окончился с передним фронтом первого импульса. Следует отметить, что как первый, так и второй каскады не реагируют на отрицательный фронт последнего тактирую щего импульса, поскольку он накрыт соответствующими импульсами установки этих каскадов. Это позволяет испопьзо- вать последующие каскады с значительно меньшим быстродействием (практически на порядок), чем первый. Быстродействие первого каскада а, следовательно, и всего программируемо- го делителя ограничено двумя факторами 1)задержкой установления на выходе логического элемента И 31; 2)задержкой окончания импульса установки на выходе логического элемента И 19, В первом случае для нормальной работы делителя передний фронт тактового импульса должен появиться только после установления 1 на информационном входе блока 13. В противном случае не произойдет формирования импульса установки. Во втором случае отрицательный тактирующий фронт первого импульса цик ла должен приходить на вход не раньше окончания импульса установки, поскольку в противном случае делитель на него не отреагирует и произойдет сбой. I6 Таким образом, максимальная временнвя задержка формирования единичного сигнала на выходе логического элемента И 31 или окончания импульса установки первого каскада определяет быстродействие программируемого делителя. Формула изобретения Программируемый делитель частоты по авторскому свидетельству № 621099, отличающийся тем, что, с целью повышения быстродействия, в каждый каскад введен трехвходовый логический элемент И, первый вход которого соединен с дополнительным выходом управляемого делителя частоты, второй вход соединен с первым выходом блока автономной установки делителя частоты данного каскада, второй вход которого соединен с выходо{ упомянутого трехвходо- вого логического элемента И, а третий вход упомянутого трехвходового логичес- кого элемента подключен ко второму выходу блока автономной установки делителя частоты последующей ячейки. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 621О99, кл. Н ОЗ К 23/ОО, 4.О2.64.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство генерации импульсов управления шаговым двигателем с электронной коррекцией | 1991 |

|

SU1829022A1 |

| Программируемый делитель частоты | 1975 |

|

SU621099A1 |

| Многофазный параметрический стабилизатор напряжения постоянного тока | 1988 |

|

SU1628057A1 |

| Фотоимпульсный измеритель поперечных размеров объектов | 1980 |

|

SU945646A1 |

| Программируемый делитель частоты | 1980 |

|

SU871340A2 |

| Асинхронный электропривод | 1989 |

|

SU1697252A1 |

| Устройство восстановления тактового сигнала из цифрового потока | 1991 |

|

SU1757114A1 |

| Устройство амплитудного отбора импульсов | 1978 |

|

SU739730A1 |

| Устройство для дистанционного контроля необслуживаемых регенеративных трансляторов | 1976 |

|

SU926775A1 |

| Устройство для определения направления вращения ротора | 1984 |

|

SU1259460A1 |

Авторы

Даты

1979-11-05—Публикация

1977-05-19—Подача