(54) ПЮГРАММИРУЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой управляемый генератор | 1987 |

|

SU1415448A1 |

| Цифровой управляемый генератор | 1986 |

|

SU1378022A1 |

| Программируемый делитель частоты | 1979 |

|

SU799145A2 |

| Каскад программируемого делителя частоты | 1980 |

|

SU919091A1 |

| Программируемый делитель частоты | 1975 |

|

SU621099A1 |

| Программируемый делитель частоты | 1977 |

|

SU696611A2 |

| Устройство для управления шаговым двигателем | 1986 |

|

SU1365342A1 |

| Устройство цифровой фазовой автоподстройки частоты | 1990 |

|

SU1732466A1 |

| Система для асинхронного сопряжения импульсных потоков | 1986 |

|

SU1420670A1 |

| Устройство для ввода информации | 1991 |

|

SU1824632A1 |

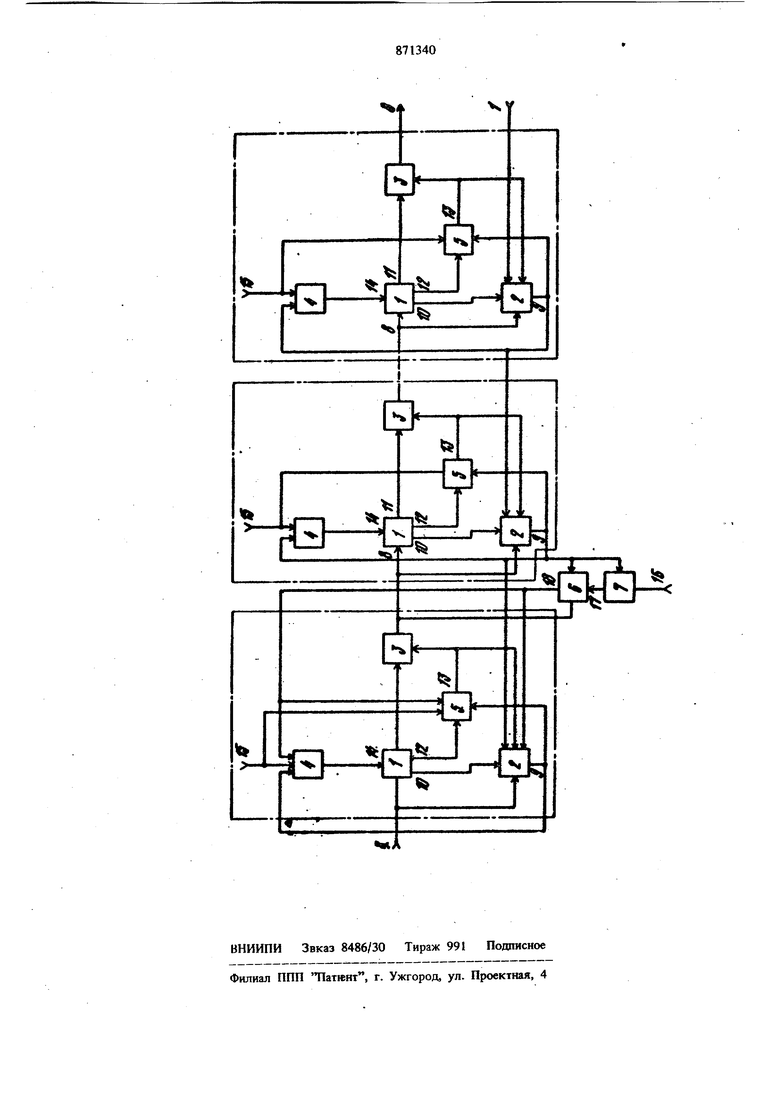

Программируемый делитель частоты относится к устройствам импульсной техники, используемым в радаютехнической аппаратуре различного назначения, в частности, в синтезаторах частот с малым временем перестройки частоты Известен программируемый делите;п частоТЫ) содержащий N каскадов, кажф1Й из состоит из управляемого делителя, блока автономной установки, злемента совпадения зяемента управления и элемента запрета. Недостатком известного программируемото делителя является то, что он на работу только с целочисленными, а не с дробными значениями коэффи1шентов деления, что затрудняет его использование в синтезаторах частот с малым временем перестройки частоты. Целью изобретения является расширение функциональных возможностей устройства, путем обеспечения дробного значения коэффициентов деления. Поставленная цель достигается тем, что в программируемый делитель частоты, содержащий N каскадов, каждый из которых состоит из управляемого делителя, блока авт м{ №1шой установки, злемента совпадения, злемента управления и элемента запрета, тактовый вхОд управляемого делителя соединен с первым входом блока автономной установки, а первый выход - со вторым входом блока автономной установки, выход блока автономной установкипредыдущего каскада подключен к третьему входу блока автономнЫ) установки 1юслед аощего каскада и к одиому из входов элемента управления, иа второй вход которого подается управляющий сигнал, выход этого элемента управления подключен к установочному входу управляемого делителя, второй выход управляемого делителя через злемент совпадения соединен с тактовым входом управляемого делителя следующего каскада, инверсный выход блока автономной установки соединен со вторым входом элемента оовпадения, кроме того, первый вход элемента запрета сгьдянен с вьгход(мм блока автсжомной установки, второй вход - с третьим выходом управляемого делителя, а выход - со вторым входом дополнительного элемента совпадения и с четвертым входом блока ав3тономной установки, введены накопитель фазы и узел добавления, первый вход которого соединен с тактовым входом управляемого делителя второго каскада, второй вход - с выходом блока автономной установки второго каскада и с первым входом накопителя фазы, на второй вход которого подается управляющий сигнал, выход которого соединен с третьим входом узла добавления, выход которого подключен к третьему входу элемента управления первого каскада, к пятому входу блока автономной установки первого каскада и к четвертому входу блока запрета первого каскада. На чертеже представлена схема программируемого делителя частоты. Устройство-делитель с дробным козффициентом деления (ДЦКД) - содержит N одинаковых каскадов, каждый из которых состоит из управляемого делителя 1 (например, декадного типа), блока 2 автономной установки, элемеита 3 совпадения, элемента 4 управления и блока 5 запрета, а также узла 6 добавления и накопителя 7 фазы. Входом каждого каскада является тактовый вход 8 управляемого делителя 1, соединенный с первым входом блока 2 автономной установки. Выходом каскада служит выход злемента 3 совпадения, соединенный со входом 8 следующего каскада. Входом ДЦКД является вход 8 первого каскада, а выходом - выход 9 блока 2 автономной ус1:ановки любого каскада. Первый выход 10 управляемого делителя 1 подключен ко второму входу блока 2 автоном ной установки, а второй выход 11 - к одному из входов злемента 3 совпадения. Выход 9 блока 2 автономной установки предьщущего каскада подключен к третьему входу блока 2 автономной установки последующего каскада, к первому входу блока 5 запрета и к первому входу элемента 4 управления. Третий выхо 12 управляемого делтеля 1 соединен со вторым входом блока 5 запрета, выход 13 которого подключен ко второму входу злемента 3 совпадения и четвертому входу блока 2 автономной установки. Установочный вход 14 дели теля 1 соединен с выходом злемента 4 управления, на второй вход 15 которого подается управляющий потенциал, который может также подводиться и к третьему входу блока запрета для его включения или блокировки. Выход 8 первого каскада ДЦКД соединен с первым входом узла 6 добавления. Выход б ка 2 автономной установки второго каскада соединен со вторым входом узла 6 добавлени и с первым входом накопителя 7 фазы, на вт рой вход 16 которого подается управляющий потенциал. Выход 17 накопителя 7 фазы подлючен к третьему входу узпа 6 добавления, ыход 18 которого соединен с третьим входом лемента 4 управления первого каскада, с четертым входом 5 запрета первого каскада с пятым входом блока 2 автономной устаовки первого каскада. Устройство работает следующим образом. Пусть на выходе 17 накопителя 7 фазы дейтвует постоянный логический уровень О (в дальнейщем просто О или I), который локирует узел 6 добавления и на его выходе 18 формируется постоянный уровень 1, т.е. акопитель 7 фазы и узел 6 добавления в зтом случае не влияют на работу ДЦКД. i Пусть также в нсходном состоянии на третьем входе блока 2 автономной установки последнего каскада и на третьих входах блоков 5 запрета всех каскадов действует уровень Г, разрещающий включение этих блоков. Блоки 2 автономной установки, элементы 4 управления и блоки 5 запрета - выключены, а элементы 3 совпадения - включены: на выходах 9, входах 14 - О, иа выходах 13 - 1. Управляемый делитель 1 последнего каскада находится в состоянии О Состояния управляемых делителей 1 остальных каскадов и логические уровни на их выходах 10, 11, 12 - произвольны. Каждый из N-1 каскадов начинает работать в режиме постоянного деления частоты входных импульсов в m раз (т - число состояний управляемого делителя). Форма сигналов на их входах 8 повторяет форму импульсов на выходах 11 управляемых делителей 1 предыдущих каскадов и На вход последнего каскада поступают импульсы длительностью в раз больше длительности импульсов на входе первого каскада, которые переводят управляемый делитель 1 N-ro каскада в состояние 1, 2 и т.д. С переходом этого управляемого делителя 1 в состояние т-1 появляется 1 на соответствующих выходах 9, входах 14 и начинается предварительная установка его в состояние . Подготавливается к включению (или включается) блок 5 запрета последнего каскада и снимается запрет на включение блока 2 автономной установки предыдущего (N-I)-ro каскада. Аналогичные процессы происходят затем последовательно в (N-l)-oM, (N-2)-OM, ... первом каскадах после перехода их управляемых делителей в состояние т-1. :3аверщение предварительной установки управляемых делителей 1 происходит в обратном порядке: от первого каскада к последнему. С окончанием тактового импульса на входе первого каскада, соответствующего состоянию т-1 его управляемого делителя 1, на выходах 9, входах 14 появляется О . Импульс на выходе первого каскада заканчивается. Управляемый делитель 1 переходит в состояние 5. Включается блок 5 запрета. Уровень О на его выходе отключает блок 2 автономной установки первого каскада от выхода 9 второго каскада и блокирует прохождение сигналов через элемент 3 совпадения. Импульс на входе второго каскада заканчивается, что приводит к завершению предварительной установки управляемого делителя 1 второго каскада в состояние Sj и к окончанию импульса иа выходе этого каскада. Здесь также включается блок 5 запрета, который отключает блок 2 автономной устано ки второго каскада от выхода 9 третьего каск да и блокирует прохождение сигналов на вход третьего каскада и т.д. В результате последовательно включаются все блоки 5 запрета. Выключение блоков 5 запрета происходит после окончания неполного цикла деления упра ляемого делителя 1 соответствующего каскада, когда при переходе его из следующего состояния т-1 в состояние О иа выходе 12 формируется сигнал, возвращающий блок 5 запрета в исходное состояние. При этом последовательно снимется затрет на работу злемеитов 3 совпадения и блоков 2 автономной установки, а ДДКД возвращается в исходное состояние и заканчивается один цикл его деления. Первый в новом цикле деления импульс на входе 8 каждого i-ro каскада задерживается иа m-Si- тактовых импульсов, действующих на входе 8 предыдущего каСкада. Поэтому, при сохранении начального уровня логической 1 на выходе 18 узла 6 добавления, коэффициент деления ДДКД является целочислеииым и определяется формулой К - S (у,-5)уц1-. Величина и порядок отсчета коэффициентов деления определяется управляющими потенциалами иа входах 15 элементов управления 4 всех каскадов. На первый вход накопителя 7 фазы поступают импульсы, длительность которых ие менее чем в m раз больще длительности импульсов иа входе 8 первого каскада, которые его состояние. Изменение состояния накопителя 7 фазы происходит после окончания импульса на выходе 9 блока 2 автономной установки второ го каскада. При достижении состоя1шя, заданиого управля щим сигналом иа втором входе 16 накопителя 7 фазы, на его выходе 17 формируется уровен 1 J подготавливающий включение узла 6 додобавлеиия. Включение узла 6 добавления происходит с появлением положительного фронта первого в новом цикле деления ДДКД импульса на выходе 8 первого каркаса (входе второго каскада). При этом на выходе 18 узла 6 добавления появляется уровень ; О , который подготавливает управляемый делитель 1 первого каскада к установке в состояние ш-1 по третьему входу элемента 4 управления независимо от управляющего потенциала по входу 15 и снимает блокировку с блока 5 запрета первого каскада по его четвертому входу на время работы узла 6 добавления, если блок 5 запрета был заблокирован управлянь щим потенциалом, подаваемым на его третий вход. Кроме того сигнал с выхода 18 узла б добавления воздействует на пятый вход блока 2 автономной установки первого каскада и снимает запрет на его включение. После перехода управляемого делителя 1 перво-i го каскада в состояние т-1, элементы всех каскадов работают в последовательности, описанной выще, так как с окончанием первого импульса в данном цикле давления ДДКД. на выходе первого каскада узел 6 дооавления возвращается в исходное состояние и на его выходе появляется . При этом появление второго импульса в этом цикле деления ДДКД на выходе 8 первого каскада задерживается иа одии период частоты следования импульсов на входе ДДКД, а коэффициент деления К2 ДДКД увеличивается на единицу (Kj KI + 1). По окончании цикла деления ДДКД на выходе 9 блока 2 автономной установки второго каскада заканчивается очередной импульс, который переводит накопитель 7 фазы в следующее состояние. Если накопитель 7 фазы в соответствии с управляющим сигналом остается в исходном состоянии, то следующий цикл деления ДДКД также произойдет с коэффициентом деления Kj. Иначе, уровень на выходе 17 накопителя 7 фазы переходит в О и коэффициент деления ДДКД в последующих циклах будет равеи KIW В исходное состояние накопитель 7 фазы возвращается через число импульсов, поступивщих на его первый вход (число циклов работы N каскадов ДДКД) равное интервалу vcoenиения . L т, где К - целое число. Количество иитервалов г с уровнем Г и их длительность q- (в циклах работы ДДКД), где j 1, 2, .. на выходе 17 накопителя 7 азы определяется конкретным алгоритмом ™ Работы, а средний коэффициент деления Q стройства за интервал усреднения L, равен ,,.,-. гИ о: - 2 cj,---5:q.i jH J -( - коэффициенты разложения целого числа oL, по основанию т. 8 Таким образом, введение узля 6 добавления и накопителя 7 фазы в программируемый делитель частоты, позволяет получать ие только целые, но и дробные значения коэффициента деления устройства. Использование предлагаемого программируемого делителя частоты в сравнении с известным программируемыми делителями частоты с дробным козффициентом деления позволит сократить габариты к вес цифровой части устройств синтеза частот, а, следовательно, и устройств синтезатора в целом, так как узел 6 добавления и накопитель 7 фазы в данном устройстве управляются сигналами, длительность импульсов которых ие менее чем в m раз превышает, длительности импульсов, поступающих на тактовый вход устройства и, следовательно, узел 6 добавления и накопитель 7 фазы могут быть выполнены на злементах, обладающих меньшим быстродействием и допускающих большую плот ность интеграции. 8 Формула изобретения Программируемый делитель частоты по авт.св. № 799145, отличающийся тем, что, с целью расширения функциональных возможностей устройства, путем обеспечения дробного значения коэффициентов деления, в него введены накопитель фазы и узел Добавления, первый вход которого соединен с тактовым входом управляемого делителя второго каскада, второй вход - с выходом блока авто номной установки второго каскада и с первым входом и опителя фазы, на второй вход которого подается управляющий сигнал, выход котоpqro соединен с третьим входом узла добавления, выход которого подключен к третьему входу злеметга управления первого каскада к пятому входу блока автономной установки первого каскада и к четвертому входу блока запрета первого каскада.

Авторы

Даты

1981-10-07—Публикация

1980-01-24—Подача