Изобретение относится к радвотехнике и предназначено для использования в спектрометрии ионизирующих излученвй. По основному авт. св. hfe 479245, известно устройство со/ ржаиее вхошю формирователь, аыхоА котерсго соединен с первым ВХ.СЖЯЛ коммутатс а аналсягозого сигнала, второй вхоо которсго через первый формирсеатель задержки, усидвЕтель и регулятор соедвнви с ( блжа формирования управляющих С1сгналов, первый вход котсрого соединен с первым выходом блсжа выделения кода, а второй - с первым входом блока функциональней зависимости, первым входом гене ратора веса, первым входом входасяо фор мирователя, выходом блока выделения интервала, а второй вход соединен со вторым генератором веса я выходом дискриминатора, вход котсрот-о соединен с выхо дом коммутатора аналогового сигнала и через второйформирователь задержки с первым входом блока сложения, выход которого соединен со вторым входом ре гулятора, а второй вход - блсж функциональной зависимости с выходом генератора веса. Этот преобразователь реализует посяедовагельное умножение остатков и имеет режима работы: основной - измерительный и дополнительный - режим линеаризации характеристики (феобразовате) ля . Однако погрешность эталонов вносит ошибку в процесс коррекции коэффициента передачи кодирующего тракта и не позволяет с необходимой точностью устанавливать его значение. Цель изо етения - повышение точности и быстродействия преобразования. Поставленная цель достигается тем, что в аналого-цифрсжой преобразователь, содержащий входной формирователь, выход которого соединен с первым входом коммутатсфа аналогового сигнапа, второй вход которого через первый формирователь задержки, усилитель и регулятор соединен с выходом блока формирования уп-

равняющих сигналов, первый вход которо1го соединен с первым выходом блока выделения кода, а второй - с первым входом блока функциональной зависимости, первым входом генератора веса, первым входом входного ффмирователя, выходом блока выделения интервала и с первым входом блока выделения кода, выход которого соединен со входом блока выделения интервала, а второй вход соединен со

вторым генератора веса и выходом дискриминатора, вход которого соединен с выходом коммутатора аналогового сигнала и черезвторой формирователь задержки с первым входом блока сложения, выход которого соединен со вторым входом регулятора, а второй вход - через блок функциональной зависимости с выходом генератора веса, введены блок управления, блок выделения погрешности этдлонов, блок выделения погрешности коэффициента передачи кодирующего тракта и фс мирователь эталонной длительности, причем первый вход блока управления подключен ко второму выходу блока выделения кода второй вход - к выходу блока выделения интервала, а выходы соединены со входами формирователя эталонной длительности, выходы которого соединены соответственно с управляющим входами первого и второго формирователей задержки, при этом вьиод коммутатора аналогового сигнала соединен с первыми входами блока выделения погрешности эталонов и блока вычисления коэффициента передачи кодирующего траста, вторые входы которых соединены с выходом блока выделения -интервала , а выходы соединены соответственно с тре тьим входом блока функциональной завИ симости и блока формирования управляющих сигналов.

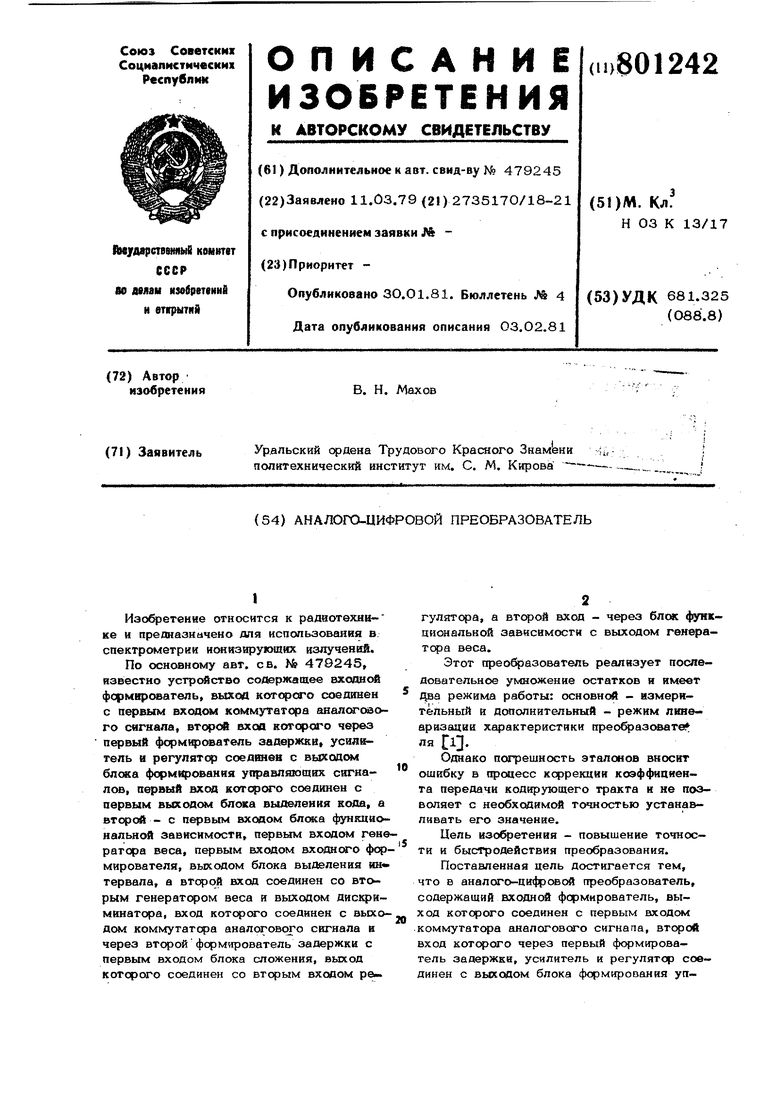

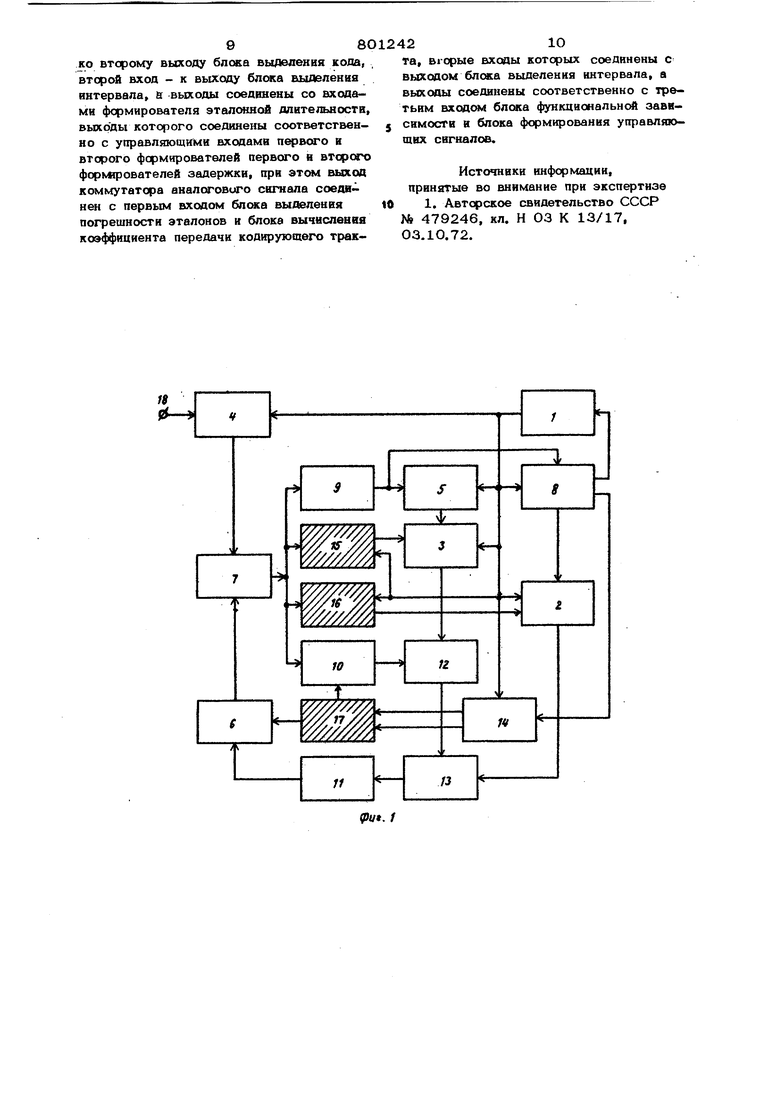

На фиг. 1 представлен аналого-цифровой преобразователь, структурная схема,

Устройство содержит блок 1 выделения интервала, блок 2 формирования управляющего сигнала, блок 3 функцихжальной зависимости , входной формирователь 4, генератор 5 веса, первый формирователь 6 задержки, коммутатор 7 аналояо вого сигнала, блок 8 выделения кода, дискриминатор 9, второй формирователь 1О задержки, усилитель 11, блок 12 сложения, регулятор 13, блок 14 управления, блок 15 выделения погрешности эталсжов, блок 16 выделения погрешности коэффициента передачи кодирующего тракта, формирователь 17 эталонной длительности, шину 18 входного сигнала.

Алгоритм, по которому работает образователь, можно представить вынием

-i:;

,в&ли Uj

икн U; /О

0.

V

Uy или

U;iO

если

где cKi.

- двоичная цифра в t -ом

n-t разряде кода измеряемой величины;

Ut

- остаток в i, -ом такте кодирования Uy измеряемой величины, равный U;i(Ui. ).

к - коэффициент передачи кодиругдеющего тракта.

Причем U{, Uy при СЯ о рдля АЦП, в процессе преобразования Ux используют эталон одного знака, в этом случае Ug U , где Up величина дискриминатора. В случа использования в прояхессе преобразования двух эталонов, одинаковых по амплитуде и разных по знаку а 1 при 1, ai -1 при ct. О, а . В первом такте кодирования Ut величина остатка будет равна

LJiHUx-a Ug) (2)

Через п тактов величину остатка УП можно представить выражением

.эт)-°а эт1 -0пЧ,,. (3)

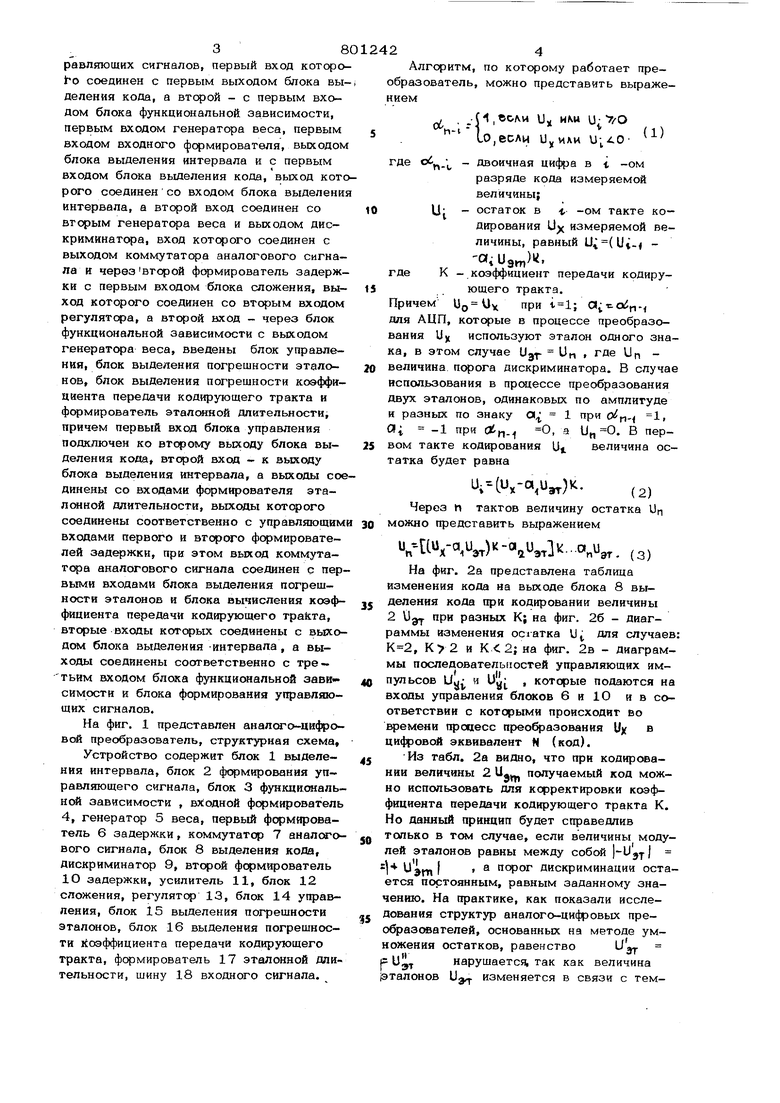

На фиг. 2а представлена таблица изменения кода на выходе блока 8 выделения кода при кодировании величины 2 Од. при разных К; на фиг. 26 - диаграммы изменения остатка U для случае , и фиг. 2в - диаграммы последовательЕюстей управляющих импульсов Uu и Uy , которые подаются н входы управления блоков 6 и 10 ив соответствии с которыми происходит во времени процесс преобразования Uy в цифровой эквивалент Ц (код).

Из табл. 2а видно, что при кодировании величины 2 Uj получаемый код можно использовать для корректировки коэффициента передачи кодирующего тракта К. Но данный принцип будет справедлив только в том случае, если величины модулей эталонов равны между собой pUj-j-) s и аи, I . а порог дискриминации остается постоянным, равным заданному значению. На практике, как показали исследования структур аналого-цифровых преобразователей, основанных на методе уми

ножения остатков, равенство

зт р Ug нарушаете так как

величина

/эталонов и, изменяется в связи с температурными и динамическими дрейфами используемых элементов и узлов для формирования Нестабильность порога дискриминации, в случае использования в процессе преобразования двух эталонов разного знака удается исключить аутем использования дискриминатора с коррекцией нулевого уровня и усил теля, который ставится перед дискримин тором, с целью уменьшения в К раз приведенной неопределенности порога срабатывания дискриминатора, где К коэффициент усиления усилителя. Устройство раоотает следующим образом. Когда закс«чилось преобразование очередного измеряемого сигнала, провер ется линейность характеристики преобра зования. Блок 1 выделения временного интервала переводит блок 8 выделения кода, блок формирования управляющего сигнала 2 и блок 3 функциональной зависимости в режим линеаризации, блокирует входной формирователь 4 и запуска ет генератор 5 веса. Эталсжный импуль с генератора 5 веса поступает на вход блсжа функциональной зависимости 3 и преобразуется им в случае кодирования системе счисления с основанием 2 в Сигнал противоположной полярности с сохранением амплитуды (инверпфуется). Функция преобразования задается один раз .и остается неизменной в течение всего времени работы преобразователя. Полученная с выхода блока 3 функциональней зависимости величина поступает через формирователь 6 задержки на вход коммутатора 7 аналсягежого сигнала и Далее начинается кодирсюание этого сигнала, которое происходит таким же 0 зом, как и код фование измеряемого сиг- нала. Полученный код гфеобразо&анной величины сравнивается с идеальным кодом этеЛ величины и полученная ошибка (разность кодов) подается блоком S на вход блока управления и блока форм фования управляющего сигнала. Этот блсж вырабатывает управляющий сигнал, соответствующий полученной ощцбке. Этим сигналом корректируется коэффициент передачи кодирующего тракта и, тем самым улучщается линейность характеристики преобразования. Процесс линеаризации характеристики разбивается на два этапа. На первом этапе происходит проверка равенства двух эталонов по модулю и проводится соответствующая коррекция величины эталонов до выпоп- нения равенства эталонов по модулю с необходимой точностью. Для этого на каждом I -ом такте кодирования одновременно включаются оба эталона, которые подаются на вход блока 12 сложения. Полученный на выходе блока сложения сигнал разности эталонов проходит по кодирующему тракту и усиленный в К раз { К AUg )поступает на второй вход блока сложения и на вход блока 15 вьшеления погреишости эталонов. На втором такте кодирования (точнее, процесса вьшеления ошибки) величина сигнала на выходе блсжа сложения будет равна CiiUgT Ь U .Через п тактов величина сигнала на выходе блока сложения будет равна А i Uyj- . .... tiАUST такая же веля чина сигнала будет подаваться на вход блока 15 выделения псгрешности этал(нов. Полученная величина А, , характеризующая точность выполнения равенства эталонов «о модулю }- UJT | - I U | используется в блсже 3 функциональной зависимос1-и для выполнения необходимой коррекции величины эталсмов. Как видно из таблицы (фиг. 2а), код при кодировании величины 2 UJT меняется только в случае изменения К в пределах и не меняется при изменении К в области . Таким обрнзом, при такой коррекции принципиально невозможно получить К 2, что необходимо для полного исключения влияния К на лннейность характеристики преобразования. Измене- ние К происходит в блоке 16 выделения погрешности коэффициента передачи тракта. П| имером реализации блока 16 м жет служить счробируемый интегратор (фиг, 2г), иа суммирующий вход котороподаетсз. е каждом такте процесса коррекции два импульса: один - с выхода коммутатора 7, а другой - с внутреннего генератора, причем величина их равна соответственно 0 - ti U эт / а 3(1 2иэт/ . Ключ на входе интегратора открывается только на время коррекции К. Получаемое на вькоде интегратора напряжение; иэт()нк ;С, где V jj - коэффициент преобразования интегратора. В конце процесса коррекции К будет характеризовать отклонение К от 2 как в сторону больших, так и меньших величин, и может использоваться в блоке 2 для формирования управляющего сигнала, изменяю1црго посредством регулятора 13 величину коэффициента передачи кодирующего тракта К. В качестве фсрмироцателя 6 задержки может быть использована простейшая ячейка

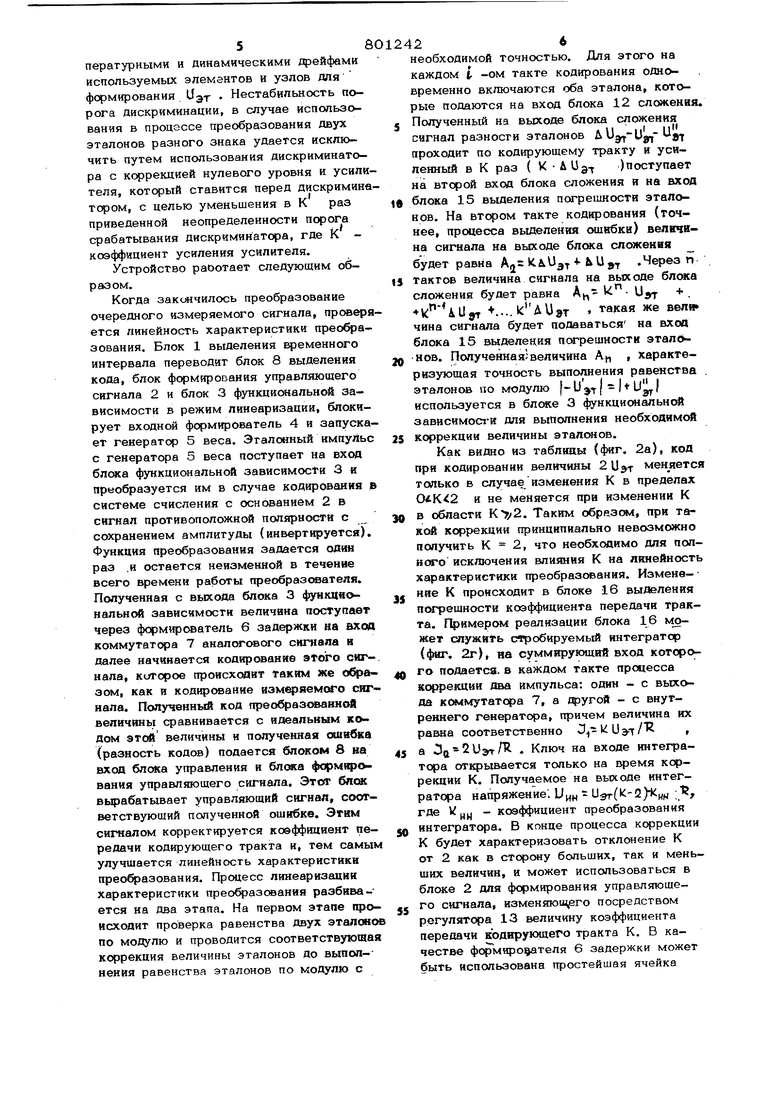

памяти, показанная на фиг. 2д, где R, сопротивление замкнутого ключа, а ключ будем считать идеальным, идеальными (для простоты) будем считать и временные пapa ;ieтpы второго формирователя 10 задержки. При этих условиях все временные процессы в преобразователе будут огфеделяться временными процессами, происходящими в первой ячейке памяти (ф(фмирователь 6). В качестве исходных условий примем состояние, при котфом напряжение на емкостях С, равно нулю, а ключ первой ячейки памяти разомкнут.

Измеряемый сигнал U подается через входной формирователь 4, коммуга- тор 7, формирователь 1О задержки на второй вход блока 12 слохсення, на первый вход которого подается соответствующий эталон. С выхода блока сложения остаток, равный U Uy подается через регулятор 13 и усилитель 11 на вход формирователя 6 задержки, причем величина его становится равной

С приходом управляющего сигнала с ; длительностью At , определяемой формирователем эталонной длительности 17, ключ формирователя 6 задержки замьшаегся на время t и напряжение на конденсаторе CD изменится в соотвегствнй с выражением . bcf-i . где Uci--, -напряжение на конденсатсчэе до момента замьшания ключа;-напряжение на выходе ключа после момента его замыкания}-постоянная времени ( ) цепи заряда конденсат(ра Ср , Считая, что в

первый момент исходное

состояние) напряжение.на конденсаторе равно нулю (UQO О), найдем напряжение на конденсаторе после первого такта крдирования,

с1;идье: ),|

где Ди -напряжение на выходе блока 12 сложения. После размыкания ключа коммутатср Г замыкает выход формирователя 6 задержки на вход фс мирователя 10 задержки,

после чего выходное напряжение У переписывается в формирователь Ю. На этом первый цикл кодирования заканчивается, в результате чего на второй

вход блока 12 сложения подается натфяжение, равное УС U, 6К.

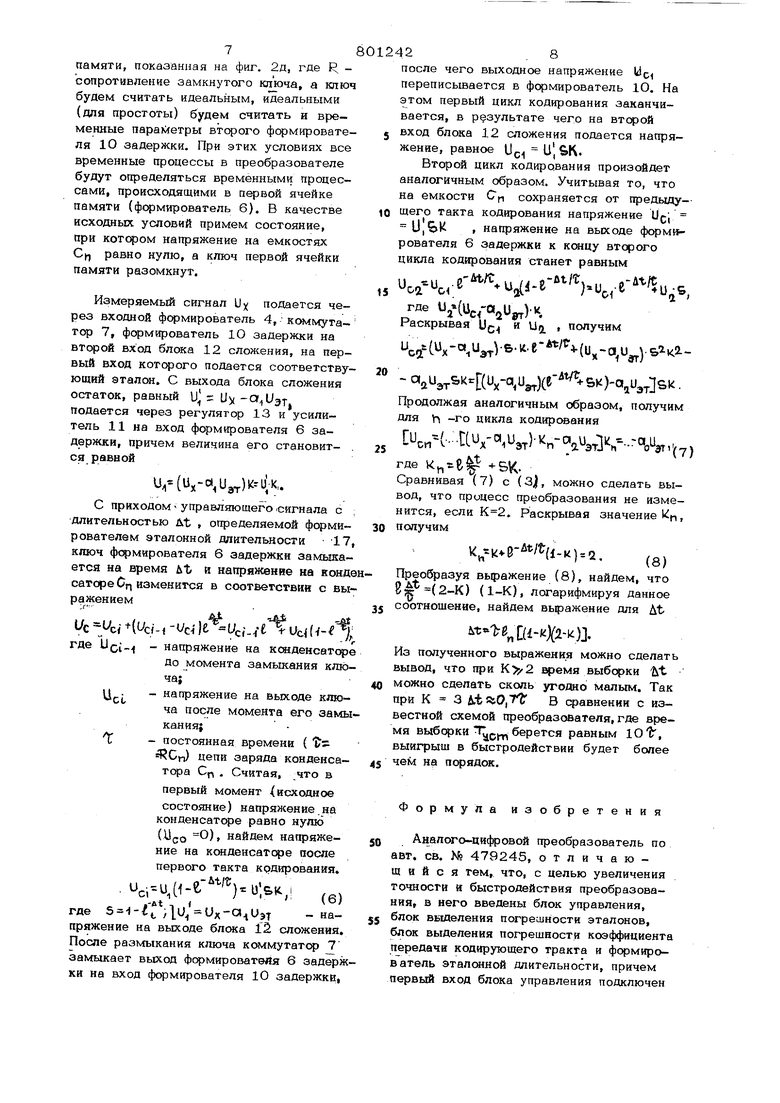

Второй цикл кодирования произойдет аналогичным образом. Учитывая то, что на емкости С сохраняется от предыдущего Такта кодирования напряжение Uc| L), , напряжение на выходе фс м№рователя 6 задержки к второго цикла кодирования станет равным

..).u,,,

г

где Ua(icfa2 T)4 Раскрывая U i получим

.iJ3TVB-e 4Ux-oi u).&Vi- «aU3TS ()Ce - 5K)-a,.

Продолжая аналогичным образом, получим для h -го цикла кодирования

tt ,)-lin-a,,U3, (7,

где SVC.

Сравнивая (7) с (3, можно сделать вывод, что процесс преобразования не изменится, если . Раскрывая значение , получим

5,„. 2.(8,

Формула изобретения

Аналсхго-цифровой преобразователь по авт. св. № 479245, отличающийся тем, что, с целью увеличения точности и быстродействия преобразования, в него введены блок управления, 5 блок ВБШеления погрешности эталонов, блок выделения погрешности коэффициента передачи кодирующего тракта и формирователь эталсшной Длительности, причем первый вход блока управления подключен Преобразуя выражение (8), найдем, что 84(2-К) (1-К), логарифмируя данное соотношение, найдем выражение для At «-гб„(-ф-). Из полученного выражения можно сделать вывод, что при время выбелки At. можно сделать сколь угодно малым. Так при К 3 A,,7 В q)aвнeнии с известной схемой преобразователя, где время выбфки берется равным Ю Ь , выигрыш в быстродействии будет более порядок.

ко BTqpoMy выходу блока выделения кода, второй вход - к выходу блсжа влшеления интервала, ts выходы соединены со входа-ми формирователя эталсжной длительности, выходы которого соединены соответственно с управляющими входами первого и второго формирователей первого я второго формфователей задержки, при этом выход коммутатора аналогового сигнала соедв нен с первьм входом блсжа выделения погрешности эталонов и блока вычисленвя коэффициента передачи кодирующего тракта, вгорые входы которых соединены с выходом блока выделения интервала, а выходы соединены соответственно с третьим входом блсжа функциональней зависимосги и блока формирования управляющих сигналов.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 479246, кл. Н 03 К 13/17, 03.10.72.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1972 |

|

SU479245A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

| Преобразователь фаза-код с автоматической коррекцией погрешности преобразования | 1980 |

|

SU883784A1 |

| Аналого-цифровой преобразователь | 1977 |

|

SU683017A1 |

| Устройство преобразования аналогового сигнала в кодовые слова | 1981 |

|

SU1005303A2 |

| Устройство для сжатия данных | 1987 |

|

SU1522268A1 |

| Цифровой фазометр | 1985 |

|

SU1298687A2 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU748862A1 |

| Аналого-цифровой преобразователь | 1977 |

|

SU677098A1 |

/

f

g V

t ffyi

-2ff,

т I

КЛ

Cn

Авторы

Даты

1981-01-30—Публикация

1979-03-11—Подача