лонов, дискриминатор нуля, блок стабилнзации коэффициента, блок стабилизации нулевого уровня, блок управления, блок регистрации и выдачи кода, введены нерестраиваемый генератор тока разряда, блок стабилизации тока разряда, блок перестройки коэффициента усиления усилителя, одновибратор, блок выравнивания эталонов, причем выходы блока управления соединены с управляющими входами перестраиваемого генератора тока разряда, выход которого соединен с аналоговым входом первой базовой ячейки памяти, регулирующий вход соединен с выходом блока стабилизации тока разряда, а второй управляющий вход соединен с выходом одновибратора; блока перестройки коэффициента усиления усилителя, выход которого соединен с входом перестройки усилителя; блока выравнивания эталонов, вход и выход которого соединены соответственно с выходом и входом генератора эталонов; блока стабилизации тока разряда; одновибратора; а вторые управляющие входы одновибратора, блока стабилизации тока разряда соединены с выходом дискриминатора нуля.

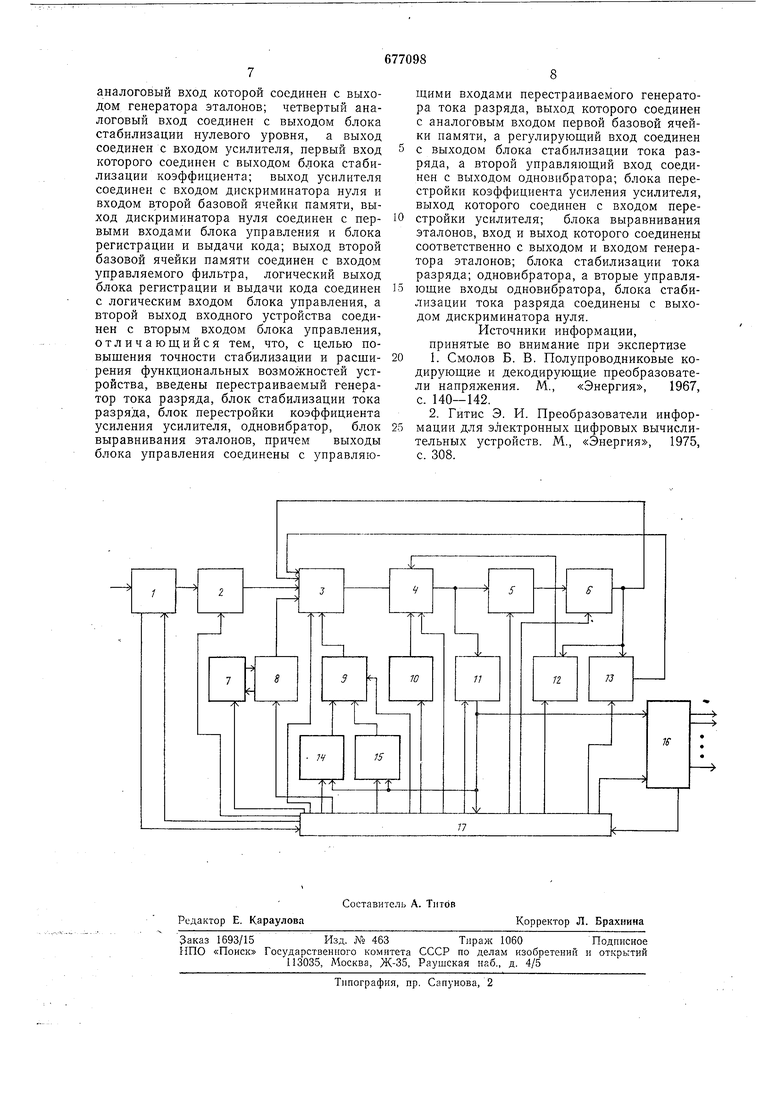

Структзфная электрическая схема устройства приведена на чертеже.

Устройство содержит входное устройство 1, входной коммутатор 2, базовую ячейку 3 памяти, усилитель 4, базовую ячейку 5 памяти, управляемый фильтр 6, блок 7 выравнивания эталонов, генератор 8 эталонов, перестраиваемый генератор 9 тока разряда, блок 10 перестройки коэффициента усиления усилителя, дискриминатор 11 нуля, блок 12, стабилизации коэффициента передачи, блок 13 стабилизации нулевого уровня, блок 14 стабилизации тока разряда, одновибратор 15, блок 16 регистрации и выдачи кода, блок 17 управления.

Устройство работает следующим образом.

В исходном состоянии входное устройство 1 разблокировано, входной коммутатор 2 разомкнут. Базовые ячейки 3 и 5 открыты по входу. Управляемый фильтр 6 работает с большой постоянной времени и снимает возбуждение в кодирующем тракте. За счет отрицательной обратной связи с коэффициентом К весь тракт приводит себя к стабильному нулевому уровню. Более точно этот уровень подстраивается блоком 13 работающим в промежутках между рабочими состояниями схемы. Блок 16 обнулен.

С приходом исследуемого сигнала U на вход входного устройства 1 последнее фиксирует его максимальное значение и выдает логический сигнал в блок 17, который выдает подготовительные сигналы и блокирует блок 13, управляемый фильтр 6 переключается в режим с малой постоянной времени, закрывает по входу базовую ячейку 5 и открывает входной коммутатор 2. Сигнал Ux через входной коммутатор 2, базовую ячейку 3, усилитель 4 поступает на вход дискриминатора И, который определяет его знак. Если f/. - на вход базовой ячейки 3 подается отрицательный эталон (ят), если - положительный эталон (- -EntY По знаку остатка онределяется старшая разрядная цифра. При

(ад -(„)О, т. е. (ад(эт), старшая разрядная цифма равна 1, а полученный остаток запоминается первой базовой ячейкой 3. При (f/:.) -(эт)0, т. е. (ад (эт), старшая разрядная цифра равна

0. Эталон со входа снимается, и величина Ux запоминается. Разрядная цифра записывается в старший разряд блока 16. Блок 16 включается на сложение. Следующей операцией является линейный разряд емкости базовой ячейки 3 путем подключения к ней перестраиваемого генератора 9 с одновременным подсчетом числа единичных приращений на блоке 16. Разряд емкости памяти продолжается целое количество квантов времени, причем время ti после напряжения перехода на емкости через нуль отвечает требованию.

.

где ti - текущее время, которому соответствует напряжение остатка f/,;

TO - квант времени между импульсами стабильной частоты, которому соответствует изменение напряжения, равное Uo (единичное приращение - квант), причем /о

- (эг)

N

где - полное число единичных приращений, составляющих (эт);

К - коэффициент усиления усилителя 4, включенного между ячейками памяти;

п - количестводвоичных разрядов, причем п может принимать значение О, 1, 2,

Квант времени То - ,

где Ге - время разряда эталона. В течение времени ti Mx+To на емкости выделяется остаток напряжения Ui (At/,. +Uo),

где At/ж - неизвестный остаток напряжения на емкости, выделяющийся за неизвестную Afx часть кванта времени, причем . и AUx. отвечают условиям .,, ,. 0.

С переходом напряжения через нуль дискриминатор 11 нуля нодготавливает блок 16 для переключения в режим вычитания, создает условия для запуска одновибратора 15, который запускается с началом кванта, и отключает перестраиваемый генератор одновременно с его окончанием,

что позволяет уменьшить погрешность, вносимую инерционностью элементов, коммутируюш;их ток разряда. Самый последний квант счетчиком не фиксируется. На этом заканчивается первый цикл формирования старших разрядных цифр. Полученный остаток ( инвертируется, усиливается в С раз, запоминается базовой ячейкой 5 памяти и передается на вход базовой ячейки 3. Одновременно с этим сигналом на вход базовой ячейки 3 подается отрицательный эталон - эт. Их разность - (Af/.v. +f7o)-(-К) +&Uxi . К запоминается. К емкости памяти подключается перестраиваемый генератор 9, начинается второй цикл работы. При этом блок 16 работает в режиме вычитания, а вес поступающих единичных прирап,ений в раз меньший, чем в предыдущем цикле. Работа устройства проходит аналогично описанному выще и заканчивается с формированием остатка второго цикла f/г, - (Af/,+ 17о). Этот остаток инвертируется, усиливается в К. раз, а запоминается базовой ячейкой 5 и подается вместе с эталоном - ЕЭТ на вход базовой ячейки 3. Разность Af/.t.. /С запоминается. На 3-ем цикле работы блок 16 работает в режиме суммирования, вес единичных приращений в раз меньше веса единичных приращений предыдущего цикла и т. д.

Таким образом, цикл за циклом на блоке 16 формируется цифровой код исследуемого сигнала, причем на первом цикле определяются старшие разряды цифр измеряемого сигнала, а в последующих циклах полученный цифровой код уточняется путем более точного измерения остатка от предыдущего цикла измерения. Точность преобразования увеличивается за счет того, что остаток усиливается и снова измеряется, а разряд емкости осуществляется одним и тем же током на всех циклах. При этом веса младших разрядов в предыдущем и последующем циклах отличаются в раз. Цифровой код снимается с m выходов блока 16.

По команде с внешнего устройства или по программе. Устройство изменяет Л т. е. изменяет укрупненное основание, в пределах которого (пределах цикла) осуществляется подсчет единичных приращений. Для этого блок 17 перестраиваемый генератор 9, блок 10, блок 16 перестраиваются в соответствии с тем основанием, в котором необходимо производить измерение. Наиболее употребительными значениями укрепленного основания является основания, кратные двум. Другим наиболее употребительным значением укрупненного основания является основание, равное 10. При этом выходной код будет двоично-десятичным.

При переходе устройства в режим коррекции корректируется ток разряда, а затем коэффициент передачи тракта. При этом входное устройство 1 заблокировано, входной коммутатор 2 разомкнут, базовая

ячейка 5 по входу закрыта, а на вход базовой ячейки 5 подается ЕЭТ, запоминается, затем подключается перестраиваемый генератор 9, в блоке 16 осуществляется подсчет единичных приращений. С поступлением Л- 1-го сигнала блок 16 через блок 17 запускает одновибратор 15, который отключает перестраиваемый генератор 9 одновременно с пост плением Л-ro импульса на вход блока 16. По знаку остаточного

напряжения, определяемого дискриминатором 11, величина тока разряда корректируется с помощью блока 14. После коррекции тока разряда корректируется коэффициент передачи тракта. При этом базовая

ячейка 3 закрыта. На емкости хранится нулевое напряжение. По команде блока 17 к емкости памяти подключается переключаемый генератор 9, одновременно запускается одновибратор 15. По истечении одного

кванта времени одновибратор 15 отключает перестраиваемый генератор 9. На емкости памяти выделяется единичное приращение напряжения Uo- Это напряжение инвертируется, усиливается в К раз, запоминается базовой ячейкой 5 и подается на вход базовой ячейки 3 одновременно с эталоном ЕЭТ. Результат сложения t/o через базовую ячейку 3 усилитель 4 поступает на вход дискриминатора 11, где определяется его знак. По знаку разности () блок 12 выдает сигнал для коррекции коэффициента усиления усилителя 4. Блок 7 как и блок 13 работает в промежутках между рабочими состояниями устройства, при этом результат суммы эталонов подается на вход блока 7. Поскольку один из эталонов берется за основной, то второй по знаку суммы корректируется -

подгоняется под первый, что позволяет уменьщить дифференциальную нелинейность характеристики преобразования.

Формула изобретения

Аналого-цифровой преобразователь, содержащий блок управления, управляющие выходы которого соединены с управляющими входами базовых ячеек памяти, усилителя, генератора эталонов, блока стабилизации нулевого уровня, блока стабилизации коэффициента, управляемого фильтра, блока регистрации и выдачи кода, входного коммутатора и входного устройства, аналоговый выход которого соединен через

входной комментатор с первым аналоговым входом первой базовой ячейки памяти; второй аналоговый вход которой соединен с выходом управляемого фильтра и аналоговым входом блоков стабилизации коэффициента усиления и нулевого уровня; третий

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU805488A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU805487A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2038694C1 |

| СПОСОБ ВОССТАНОВЛЕНИЯ ПРОВОДИМОСТИ ЗРИТЕЛЬНОГО НЕРВА ПРИ ГЛАУКОМЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1989 |

|

RU2072814C1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Способ уравновешивания цифровых экстремальных мостов переменного тока | 1987 |

|

SU1413537A1 |

| Калибратор переменного напряжения | 1983 |

|

SU1115031A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| Анализатор длительности выбросов и провалов напряжения | 1988 |

|

SU1674156A1 |

| Многоканальный интерполяционный измеритель временных интервалов | 1982 |

|

SU1027695A1 |

Авторы

Даты

1979-07-30—Публикация

1977-04-27—Подача