Изобретение относится к .ргщиоIтехнике и может быть использовано цифровых синтезаторах частоты приемно-передающей аппаратуры, э устройствах дискретной автоматики и вычислительной техники.

Известен делитель с переменншл коэффициентом деления, содержащий несколько счетчиков с переменньм коэффициентов деления и элементами совпадения на входе, триггегжа коммутсщии, логические элементьа И, ИЛИ и НЕ tl.

Однако известное устройство имеет сложный процесс установки требуемого коэффициента деления или задержку выходного сигнала, зависящую от коэффициента деления.

Известен также делитель частоты с переменным коэффициентом деления, содержащий счетчик с постоянным коэффициентом пересчета, первый счетчик с переменным коэффициентом пересчета с первой схемой установки, входы которых через элементы совпадения связаны с источником входного сигнала и с выходами триггера коммутации, а также триггер управления, инвертор, логические элементы И и ИЛИ, второй счетчик с переменным коэффициентом пересчета и со второй схемой установки C2J.

В известном делителе многоэлементная суммарная задержка выходного сиг. нала затягивает время переключения триггера коммутации в конце каждого цикла деления, в связи с чем неполностью используется быстродействие счетчиков и в результате чего извест0ный делитель с переменным коэффициентом деления имеет пониженное быстродействие .

Цель изобретения - повышение быстродействия.

5

Поставленная цель достигается тем, что в делитель частоты с переменным коэффициентом деления, содержащий счетчики с постоянным и переменным коэффициентом счета, триггер коммута0ции, запоминающий триггер, инвертор, элементы ИЛИ и И, первые входы двух первых из которых подключены к входной шине, вторые входы - к вЕлходам запоминающего триггера, а первый вход

5 третьего элемента И соединен с единичным выходом триггера коммутации, введены арифметические устройства, дополнительный запоминающий триггер, дополнительные элементы ИЛИ и И и

0 дополнительный инвертор, причем выход

первого арифметического устройства подключен к третьим входам двух первых элементов И, к первому входу четвертого элемента И, к первому входу первого дополнительного элемента И и через инвертор к первому входу рторого дополнительного элемента И, выход второго арифметического устройства подключен к четвертым входам двух первых элементов И, к первому входу пятого элемента И, ко второму входу второго дополнительного элемен. та И и через инвертор ко второму входу первого дополнительного элемента И третьи входы дополнительных элементов И и второй вход третьего элемента И подключены к входной шине, выход первого элемента И и первого дополнительнрго элемента И через элемент ИЛИ подключены ко входу первого счетчика с переменньа коэффициентом счета, выход которого соединен с нулевым входом запоминающего триггера и с единичньви входом дополнительного запоминающего триггера, выходы второго элемента И и второго дополнительного элемента И через последовательно соединенные дополнительный элемент ИЛИ и счетчик с постоянным коэффициентом счета подключены ко входу второго счетчика с переменным коэффициентом деления, выход которого подключен к единичному входу запоминающего триггера и к единичному входу триггера коммутации, нулевой вход которого подключен к выходу пятого элемента И, при этом нулевой вход дополнительного запоминающего триггера соединен с выходом четвертого элемента И, а единичный выход - с третьим входом третьего элемента И, выход которого подключен ко вторьм входам четвертого и пятого элементов И.

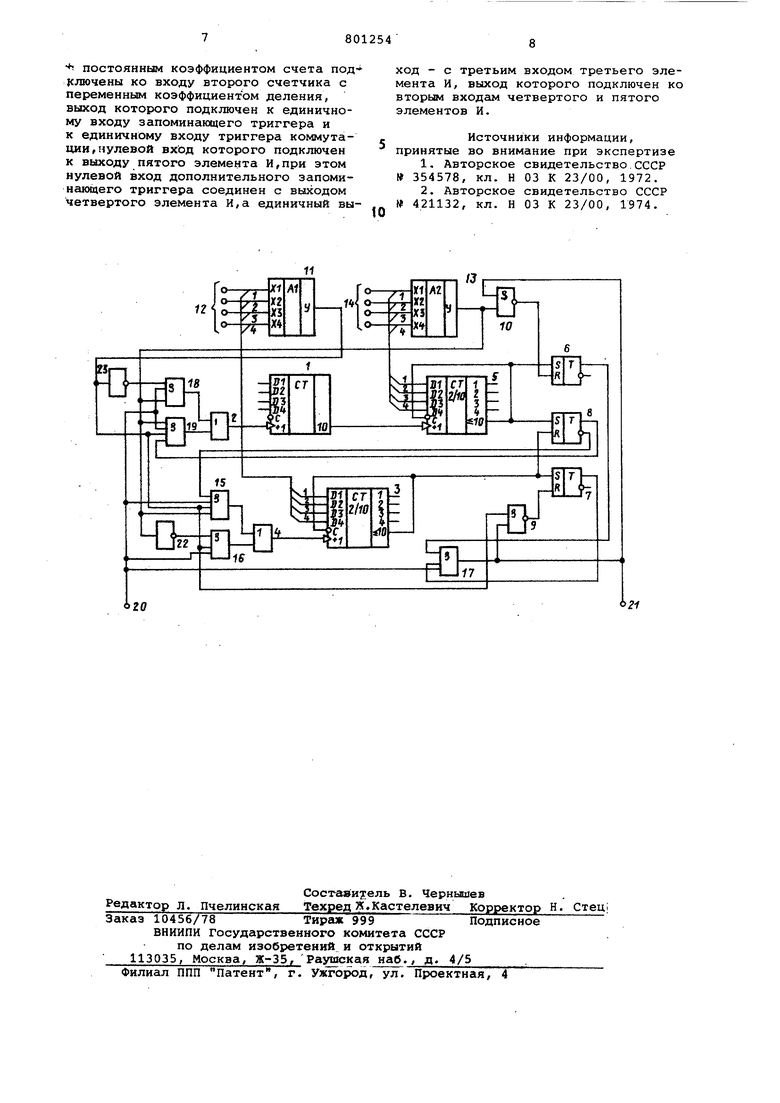

На чертеже представлен делитель частоты с переменным коэффициентом деления, структурная электрическая схема.

Устройство содержит счетчик 1 с постоянным коэффициентом счета с логическим элементом 2 ИЛИ на входе, первый счетчик 3 с переменным коэффициентом счета с логическим элементом 4 ИЛИ на входе, второй счетчик 5 с переменным коэффициентом счета, выход которого подключен к единичному входу триггера б коммутации, первый 7 и вторюй 8 запоминак&1ие триггера, нулевые входы которых подключены соответственно к элементам 9 и 10 И, первое арифметическое устройство 11, информационные входы которого подключены к шинам 12 сигналов двойного кода коэффициентов деления единицы, второе арифметическое устройство 13, информационные входы которого подключены к шинам 14 сигналов двоичного кода коэффициентов деления десятки, элементы 15-19 И, каждый второй вход

которых подключен к шине 20 источника входного сигнала, шину 21 выходного сигнала, инверторы 22 и 23. Выход счетчика 1 подключен непосредственно к входу счетчика 5, выход которого подключен к единичным входам триггеров 6 и 8. Единичный выход триггера 8 подключен к первому входу элемента 17 И. Выход счетчика 3 подключен к нулевому входу триггера 6 и к. единичному входу триггера 7, единичный выход которого подключен к третьему входу элемента 17 И, выход которого подключен к шине 21 и к первым входам элементов 9 и 10 И. Второ вход элемента И 9 подключен к выходу первого арифметического устройства 1 и к каждому третьему входу элементов 15, 1би19Иик входу инвертора 23, выход которого подключен к первому входу элемента 18 И, выход последнего подключен к первому входу элемента 2 ИЛИ. Второй вход элемента 10 И подключен ко второму арифметческому устройству 13, к третьему вхду элемента 18 И, к первому входу элемента 19 И, к третьему входу элемента 15 И и ко входу инвертора 22, выход которого подключен ко второму входу элемента 16 И, выход последнего подключен ко второму входу элемента ИЛИ 4. Единичный выход триггера б подключен к четвертому входу элемента 19 И, выход которого подключен ко второму входу элемента 2 ИЛИ. Нулевой выход триггера 6 подключен к первому входу элемента 15 И выход которого подключен к первому входу элемента 4 ИЛИ.

Устройство работает следующим образом.

Счетчик 1 имеет постоянный коэффициент счета NH 10. Счетчики 3 и имеют переменные коэффициенты счета соответственно Nj 1-10 и Nj 1-10, которые устанавливаются с помощью сигналов двоичного кода на соответствукяцих шинах 14 и 12. Оба счетчика с переменным коэффициентом счета работают в режиме автономного сброса и перезаписи, установленного на шинах 14 и 12, а следовательно, и на информационных входах. Общий коэффициент деления делителя определяется из выражения

N - N NJ+ N3 lONj +N3 N jc+NtA

где NAIC- tONs; NEA NJ .

Таким образом, последовательно включенные счетчики 1 и 5 обеспечивают получение слагаемого Мд,а счетчик 3-получение слагаемого МЕД в общем коэффициенте деления N. Поочередная работа счетчиков 1, 5 и 3 обеспечивается триггером 6, первым арифметическим устройством 11 совместно с элементами 15 и 16 И, элементом 4 ИЛИ, инвертором 22 и вторым арифметическим устройством 13 совместно с элементами 18 и 19 И, 2 ИЛИ и инвертором 23. Арифметические уст ройства 11 и 13 обеспечивают выполнение операции, определяемой выражениемт - Хя % А В случае, когда N О, на обоих выходах арифметических устройств 11 и 13 появляется запрещающий сигнал, блокирующий элементы 15, 16, 18 и 19 И и сигнал со входа 20 не проход на счетчики 1 и 3. Если N ЫЕД + О, то на вых дах арифметических устройств 11 и 13 присутствует сигнал логической единицы (разрешающий сигнал1. В это случае, в зависимости от сигналов на выходах триггера 6, входной сигнал с шины 20 будет поступать либо на вход счетчика 1 через элементы 19 И и 2 ИЛИ, либо на вход счетчика 3 через элементы 15 И и 4 ИЛИ. Выходные сигналы счетчиков 3 и 5 меняют состояние триггера 7 и одновре менно переключают триггеры 7 и 8 в единичное состояние, при котором по являются разрешающие сигналы на вто ром и третьем входе элемента 17 И. На этом первый цикл подсчета первого числа входных импульсов, равного N, оканчивается, в следующем цикле пов ряется поочередная работа счетчико-в 1, 5 и 3. При этом каждый первы импульс серии цикла проходит через элемент 17 И на выходную шину 21 де лителя и на элементы 9 и 10, которые возвращают триггеры 7 и 8 в исходное состояние. В случае, когда N Мдес,а MSA О запрещающий сигнал с выхода арифметического устройства 11 блокирует элементы 15, 16 и 19 И, а элемент 9 И удерживает триггер 7 в efiHuvtviiou состоянии,подготавливая элемент 17 И к прохождению входного И1«шульса на выход делителя. Одновременно через инвертор 23 подается разрешающий сиг нал на элемент 18 И, и входные импульсы поступают через элементы 18 И и 2 ИЛИ на вход счетчика 1, с выхода которого - на вход счетчика 5 и далее на триггер 8. После прохождения числа икшульсов, равного Ыдес, триггер 8 опрокидывается в единичное состояние, и на выходе элемента 17 И, а следовательно, на выходе 21 делителя , появляется выходной импульс, который является первым по счету в следующей серии подсчитываемых импульсов. Таким образом, триггер 8 ус танавливается в нулевое состояние, а счетчики 1 и 5 работают независимо от состояния выходов триггера 6, ибо элементы 15 и 19 И находятся в заблокированном состоянии. В случае, когда N Мед, О, 3апр)ещгиощий сигнал с выхода арифметического устройства 13 блокирует элементы 18, 19 и15 И и элемент 10 который удерживает триггер 8 в еди,«ичном состоянии, подготавливая тем самым элемент 17 И к прохождению входного импульса на выход делителя. Одновременно через инвертор 22 подается разрешающий сигнал на элемент 16 И, и входные импульсы через элементы 16 И и 4 ИЛИ поступают на вход счетчика 3, который подсчитывает число импульсов, равное , и после окончания счета опрокидывает триггер 7 в единичное состояние. На выходе элемента 17 И, а следовательно, и на выходе 21 делителя, появляется выходной импульс, который устанавливает триггер 7 в исходное состояние, а счетчик 3 работает независимо от состояния выходов триггера 6, ибо элементы 15 и 19 И находятся в заблокированном состоянии. Формула изобретения Делитель частоты с переменным коэффициентом деления, содержащий счетчики с постоянным и переменным коэффициентом счета, триггер коммутации, запоминающий триггер, инвертор, элементы ИЛИ и И, первые вхо:ды двух первых из которых подключены к входной шине, вторые входы .к выходам запоминающего триггера, а первый вход третьего элемента И со: единен с единичны выходом триггера I коммутации, отличающийся тем, что, с целью повьяиения быстродействия, в него введены арифметические устройства, дополнительный запоминающий триггер, дополнительные элементы ИЛИ и И к дополнительный инвертор, причем выход первого арифметического устройства подключен к третьим двух первых элементов И, к первому входу четвертого элемента И, к первому входу первого дополнительного элемента И и через инвертор к первому входу второго дополнительного элемента И, выход второго арифметического устрюйства подключен к четвертым входам двух первых элементов И, к первому входу пятого элемента И, ко второму входу второго дополнительного элемента И и черег инвертор ко второму входу первого дополнительного элемента И, третьи входы дополнительных элементов И и второй вход третьего элемента И подключены к входной шине, выходы первого элемента И и первого дополнительного элемента И через элемент ИЛИ подключены ко входу первого счетчика с переменным коэффициентом счета, выход которого соединен с нулевии входом запоминающего триггера и с единичным входом дополнительного запоминающего триггера, выходы второго элемента И к второго дополнительного элемента И через последовательно соединенные ополнительный элемент ИЛИ и счетчик

постоянным коэффициентом счета под- Ключены ко входу второго счетчика с переменным коэффициентом деления, выход которого подключен к единичному входу запоминающего триггера и к единичному входу триггера коммутации, нулевой вход которого подключен к выходу пятого элемента И,при этом нулевой вход дополнительного запоминающего триггера соединен с выходом четвертого элемента И,а единичный выход - с третьим входом третьего элемента И, выход которого подключен ко вторым входам четвертого и пятого элементов И.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство,СССР № 354578, кл. Н 03 К 23/00, 1972.

2.Авторское свидетельство СССР № 421132, кл. Н 03 К 23/00, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1982 |

|

SU1072266A1 |

| Управляемый делитель частоты с коэффициентом деления @ | 1980 |

|

SU1100730A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1182667A1 |

| Анализатор временных интервалов между импульсами | 1980 |

|

SU900431A1 |

| Цифровое устройство для обработки информации частотных датчиков | 1984 |

|

SU1239622A1 |

| Устройство для умножения частоты следования периодических импульсов | 1978 |

|

SU769720A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1119174A1 |

| Измеритель средней частоты импульсов | 1987 |

|

SU1487661A1 |

| Устройство для управления шаговым электродвигателем | 1980 |

|

SU928592A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

Авторы

Даты

1981-01-30—Публикация

1979-01-10—Подача