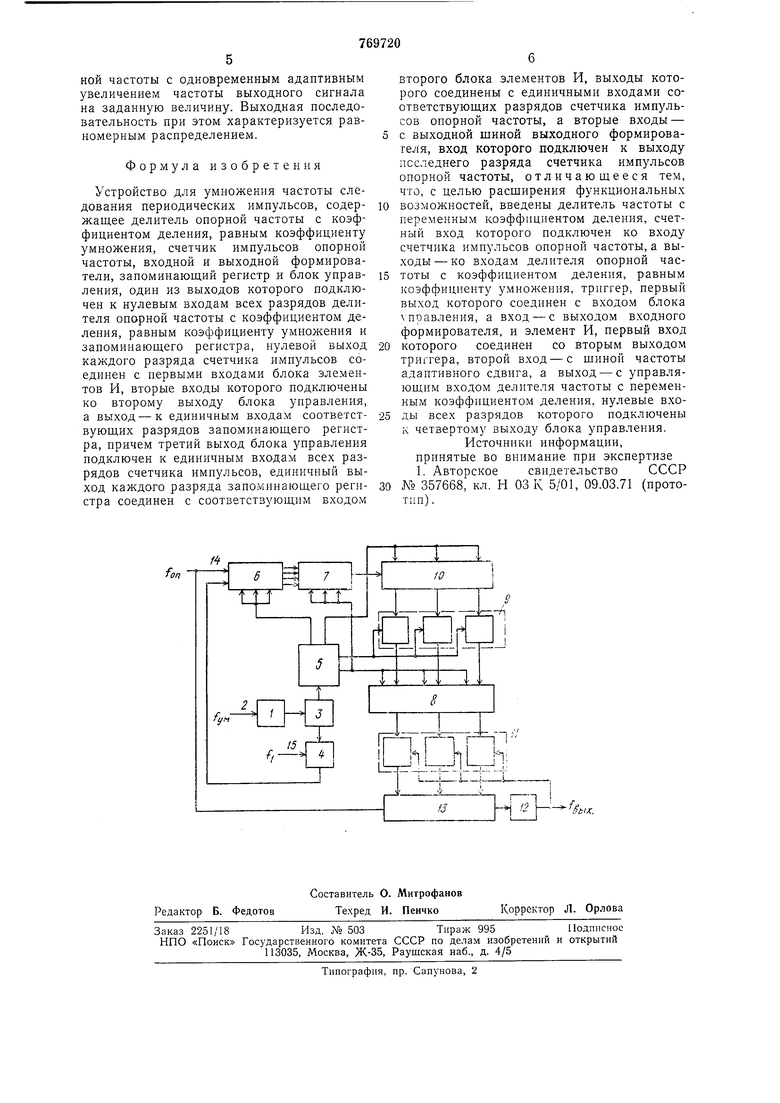

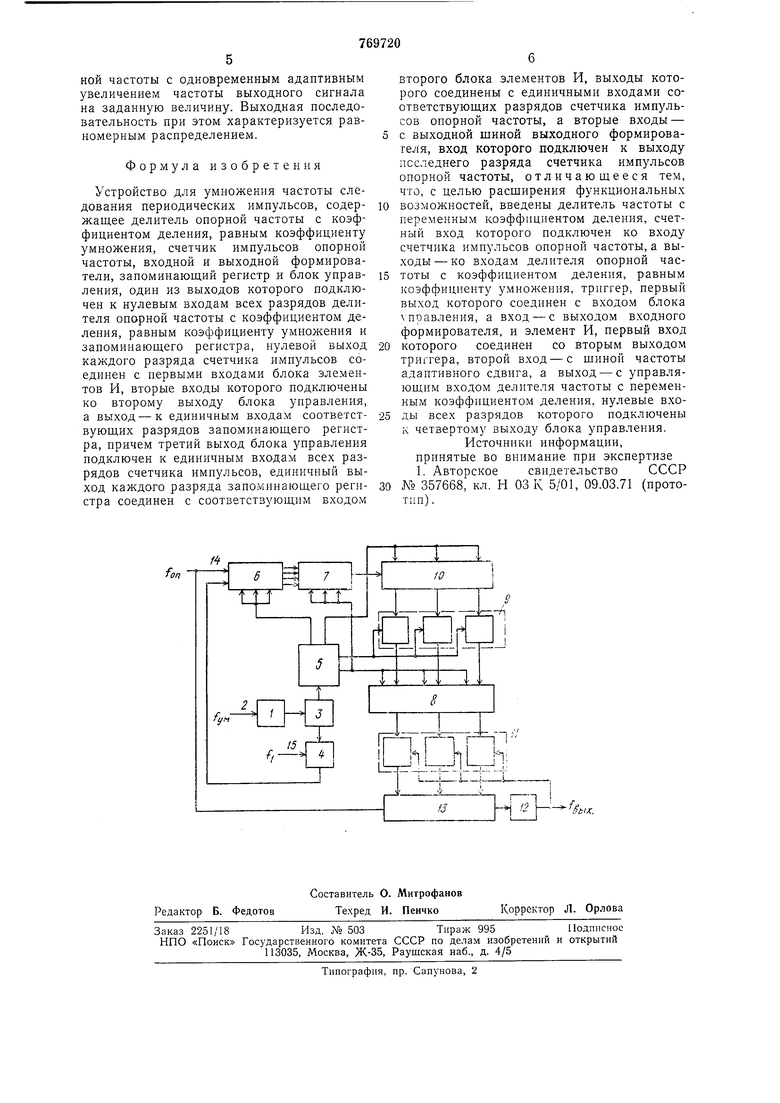

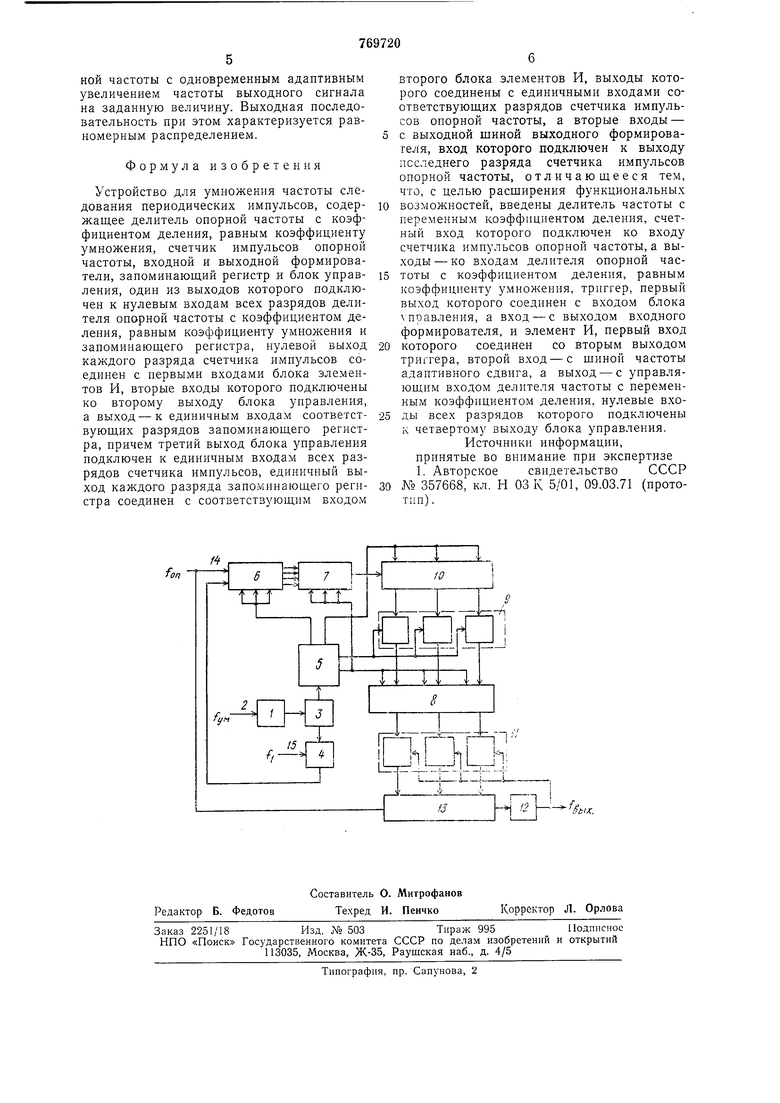

ной частоты с коэффициентом деления, равным коэффициенту умножения, триггер, первый выход которого соединен с входом блока управления, а вход - с выходом входного формирователя, и элемент И, первый вход которого соединен со вторым выходом тригге ра, второй вход - с шиной частоты адаптивного сдвига, а выход - с управляющим входом делителя частоты с переменным коэффициентом деления, нулевые входы всех разрядов которого подключены к четвертому выходу блока управления. На чертеже представлена структурная электрическая схема устройства. Устройство содержит входной формирователь 1, соединенный с шиной 2 входного сигнала, триггер 3, первый выход которого подключен к первому входу элемента И 4, а второй выход-ко входу блока 5 управления, один выход которого соединен с нулевыми входами делителя 6 частоты с переменным коэффициентом деления, второй-.с нулевыми входами делителя 7 частоты с коэффициентом деления, равным коэффициенту умножения, и с нулевыми входами запоминающего регистра 8, третий- с первыми входами блока элементов И 9, выходы которых подключены норазрядно к единичным входам запоминающего регистра 8, а вторые входы подключены к выходным шинам счетчика 10 имиульсов, счетный вход которого соединен с выходом делителя 7, а установочные входы - с четвертым выходом блока 5 управления. Выходы запоминающего регнстра 8 соединены с соответствующими входами блока элементов ИИ, вторые входы которых соединены с выходом выходного формирователя 12, вход которого подключен к выходу счетчика 13 имнульсов опорной частоты, а выходы блока элементов И И поразрядно соединены с единичными входами счетчика 13, счетный вход которого соединен с шиной 14 опорной частоты и с счетным входом делителя 6, управляющий вход которого подключен к выходу элемента И 4, второй вход которого соединен с шиной 15 частоты адаптивного сдвига. Устройство работает следуюшим образом. Импульсы (входной) умножаемой частоты 2/умн поступают на вход формирователя 1, а с выхода формирователя - на вход тригера 3, с одного выхода которого импульс с длительиостью 1//умн поступает на элемент И 4, на второй вход которого постзпает сигнал с частотой адаптивного Сдвига /1. На выходе элемента И 4 за один период количество импульсов оиределяется выражением Импульсы опорной частоты /оп поступают на вход делителя 6, коэффициент деления которого равен Л:, далее - на вход деителя 7, коэффициент делення которого равен заданному коэффицненту умножения Имиульсы с выхода делителя 7, частота следования которых равна - , в течение второго периода 1//умы подаются на счетный вход счетчика 10. Каждый импульс, поступающий со второго выхода триггера 3 в блок 5 управления, формирует в этом блоке четыре следующих друг за другом сигнала. Первый импульс устанавливает в состояние «О все разряды делителя частоты 7 и регистра 8, второй через блок элементов И 9 переносит обратный код из счетчика 10 в регистр 8, третий устанавливает все разряды счетчика lO в состояние «1, а четвертый по окончанию входиого импульса устанавливает делители 6 с нереносньш коэффициентом деления в состояния «О. За один нериод следования импульсов с выхода триггера 3 на вход счетчика 10 поступает количество импульсов .(2) (V, -г /)/у„„ Так как в иачале иериода импульса умножаемой частоты все разряды счетчика 10 устанавливаются в «1 состояния, то по окончании этого периода в счетчике 10 будет зафиксировано число N,.(3) При поступлении следующего импульса с триггера 3 в блоке 5 управления формируется очередная группа из четырех сигналов. При этом в регистр 8 вносится из счетчика 10 число в обратном коде, т. е. в регистре 8 устанавливается число N, N-N,,(4) где , т - число разрядов в счетчике 10 в регистре 8 и в счетчике 13. Число 4, нредставляющее собой дополнительный код числа yV2, переносится из регистра 8 в счетчик 13. Каждый импульс переполнения счетчика 13 постуиает на входы блока элементов И 11 через выходной формирователь 12. Частота следования импульсов на выходе формирователя 12 S /оп /onj J вых - ,Y yV4 Л - (N NI) з.()Л„,Лг(т + )- + Л«- (5) /умы/ Таким образом, выражение (5) показывает, что система реализует операцию умножения на заданный коэффициент входной частоты с одновременным адаптивным увеличением частоты выходного сигнала на заданную величину. Выходная носледовательность при этом характеризуется равномерным распределением.

Формула изобретения

Устройство для умножения частоты следования периодических импульсов, содержащее делитель опорной частоты с коэффициентом деления, равным коэффициенту умножения, счетчик импульсов опорной частоты, входной и выходной формирователи, запоминающий регистр и блок управления, один из выходов которого подключен к нулевым входам всех разрядов делителя опорной частоты с коэффициентом деления, равным коэффициенту умножения и запоминающего регистра, нулевой выход каждого разряда счетчика импульсов соединен с первыми входами блока элементов И, вторые входы которого подключены ко второму выходу блока управления, а выход - к единичным входам соответствующих разрядов запоминающего регистра, причем третий выход блока управления подключен к единичным входам всех разрядов счетчика импульсов, единичный выход каждого разряда запоминающего регистра соединен с соответствующим входом

второго блока элементов И, выходы которого соединены с единичными входами соответствующих разрядов счетчика импульсов опорной частоты, а вторые входы - с выходной шиной выходного формирователя, вход которого подключен к выходу последнего разряда счетчика импульсов опорной частоты, отличающееся тем, что, с целью расщирения функциональны. возможностей, введены делитель частоты с переменным коэффициентом деления, счетный вход которого подключен ко входу счетчика импульсов опорной частоты,а выходы- ко входам делителя опорной частоты с коэффициентом деления, равным коэффициенту умножения, триггер, первый выход которого соединен с входом блока управления, а вход - с выходом в.ходного формирователя, и элемент И, первый вход которого соединен со вторым выходом триггера, второй вход - с шиной частоты адаптивного сдвига, а выход - с управляющим входом делителя частоты с переменным коэффициентом деления, нулевые входы всех разрядов которого подключены к четвертому выходу блока управления.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР К° 357668, кл. Н 03 К 5/01, 09.03.71 (протоТ1Ш) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следованияиМпульСОВ | 1979 |

|

SU824418A1 |

| Умножитель частоты | 1979 |

|

SU813728A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 1972 |

|

SU357668A1 |

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Устройство для умножения частоты следования периодических импульсов | 1981 |

|

SU1005285A2 |

| Устройство для умножения частоты следования периодических импульсов | 1975 |

|

SU544112A2 |

| Умножитель частоты повторения импульсов | 1977 |

|

SU687602A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Устройство для умножения частотыСлЕдОВАНия пЕРиОдичЕСКиХиМпульСОВ | 1979 |

|

SU824419A2 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

Авторы

Даты

1980-10-07—Публикация

1978-10-04—Подача