коэффициентом счета, а выход второго элемента И - ей счетным входом 1182667 второго счетчика с переменным коэффициентом счета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменнымКОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU801254A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1982 |

|

SU1072266A1 |

| Устройство для преобразования средней частоты пачки импульсов | 1980 |

|

SU906000A1 |

| Цифровое устройство для обработки информации частотных датчиков | 1984 |

|

SU1239622A1 |

| Делитель частоты следования импульсов с переменным дробным коэффициентом деления | 1989 |

|

SU1653155A1 |

| Умножитель частоты следования импульсов | 1988 |

|

SU1547050A1 |

| Делитель частоты с переменным коэффициентом деления | 1987 |

|

SU1444939A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1070694A1 |

| Устройство для умножения частоты следования периодических импульсов | 1978 |

|

SU769720A1 |

ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ, содержащий счетчик с постоянным коэффициентом счета, два счетчика с переменным коэффициентом счета, два элемента ИЛИ, триггер коммутации, два запоминающих триггера, два элемента И-НЕ, три элемента И, первые входы которых соединены с входной шиной, второй вход первого элемента И со« динен с нулевым выходом триггера коммутации, единичный выход которого соединен с вторым входом второго элемента И, выход счетчика с постоянным коэффициентом счета соединен со счетным входом первого счетчика с -переменным коэффициентом счета, выход которого подключен к 5-входам триггера коммутации и первого запоминающего триггера, единичный выход которого соединен с вторым входом третьего элемента И, выход второго счетчшса с переменным коэффициентом счета подключен к R -входу триггера коммутации и к 6-входу второго запоминающего триггера, единичный выход которого соединен с третьим входом третьего элемента И, выход которого подключен к выходной шине и к первым входам первого и второго элементов И-НЕ, вторые входы которых соединены с выходами соответственно первого и второго элементов ИЛИ, а выходы - с R-входами соответствующих запоминающих триггеров, шина кода коэффициента деления десятки соединена с соответствующими информационными входами первого счетчика с переменным коэффициентом счета и входами первого элемента ИЛИ, а шина кода коэффициента деления единицы с соответствующими информационными входами второго счетчика О) с переменным коэффициентом счета и входами второго элемента ИЛИ, о тл и чающийся тем, что, с целью повьшения быстродействия и-точности при одновременном упрощении, введены.дополнительные S- и R-входы и триггер коммутации и дополнительные 5-входы и запоминающие триггеры, причем дополнительный 6-вход триг- гера коммутации соединен с выходом первого элемента ИЛИ, с входом сброса счетчика с постоянным коэффициентом счета и с дополнительным 5-вх6дом первого запоминающего триг-; гера, дополнительный R-вход триггера коммутации соединен с вы:4одом второго элемента ИЛИ и с дополнительным 5-входом второго запоминающего триггера, а нулевые выходы первого и второго запоминающих триггеров подключены к входам установки соответствующих счетчиков с переменным коэффициентом счета, при этом выход первого элемента И соединен со счетным входом счетчика с постоянным

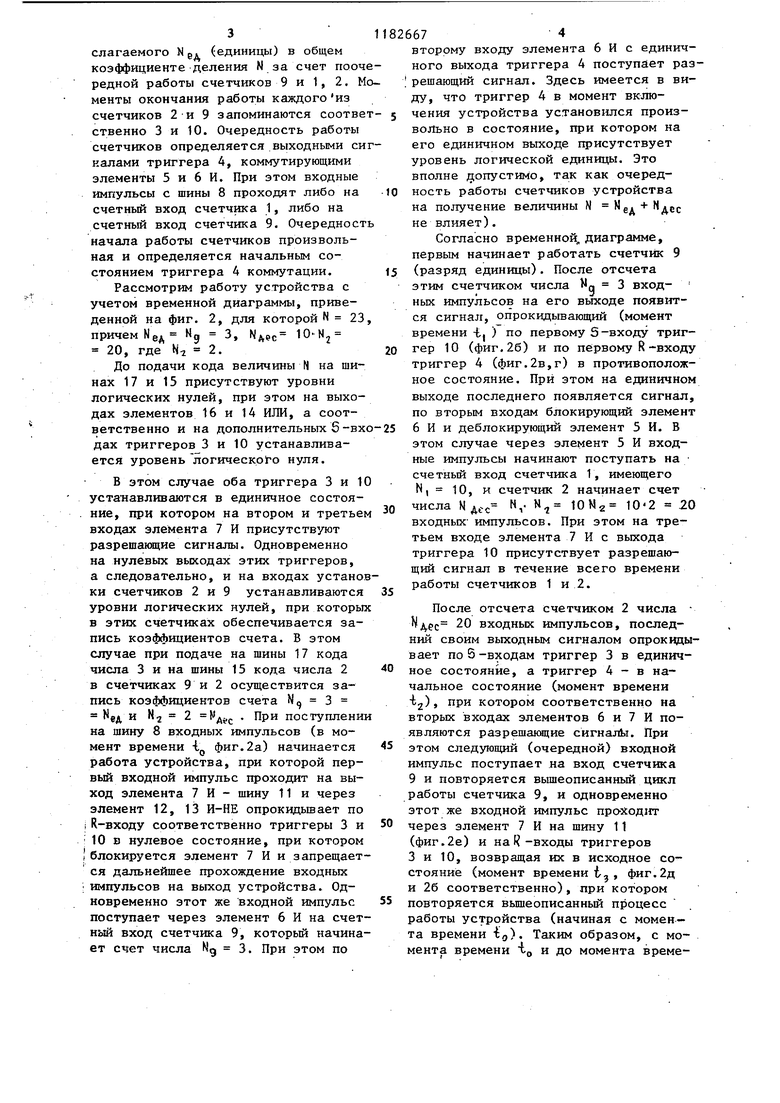

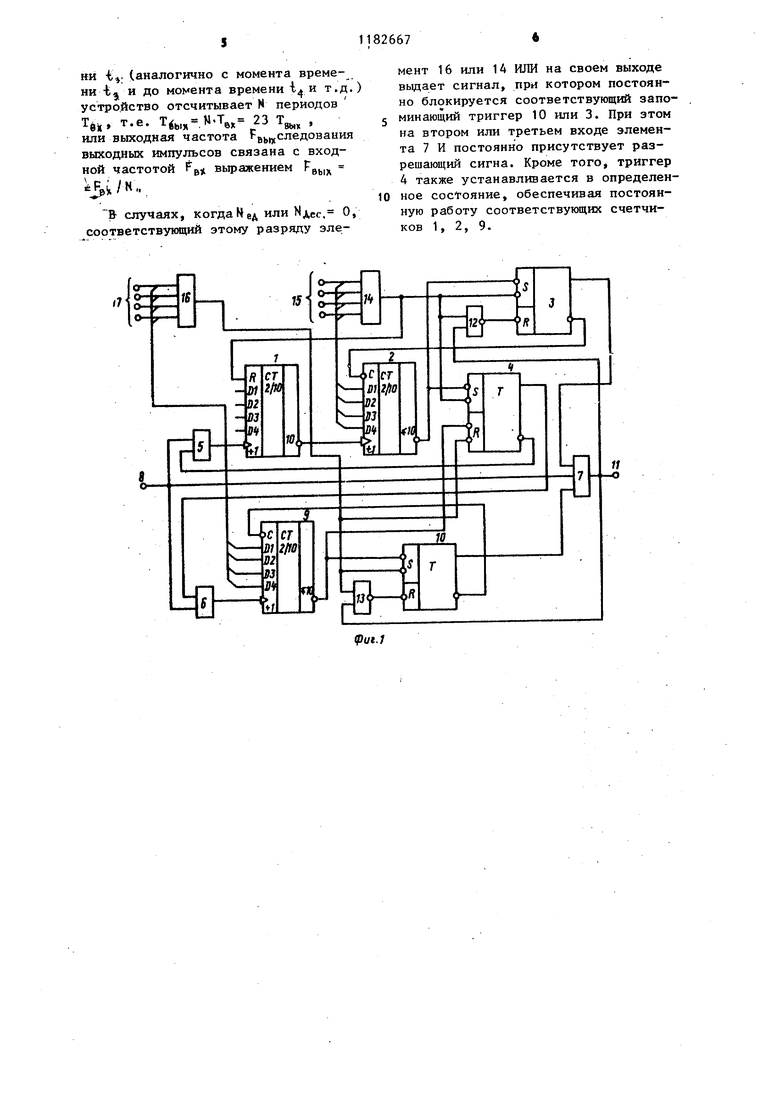

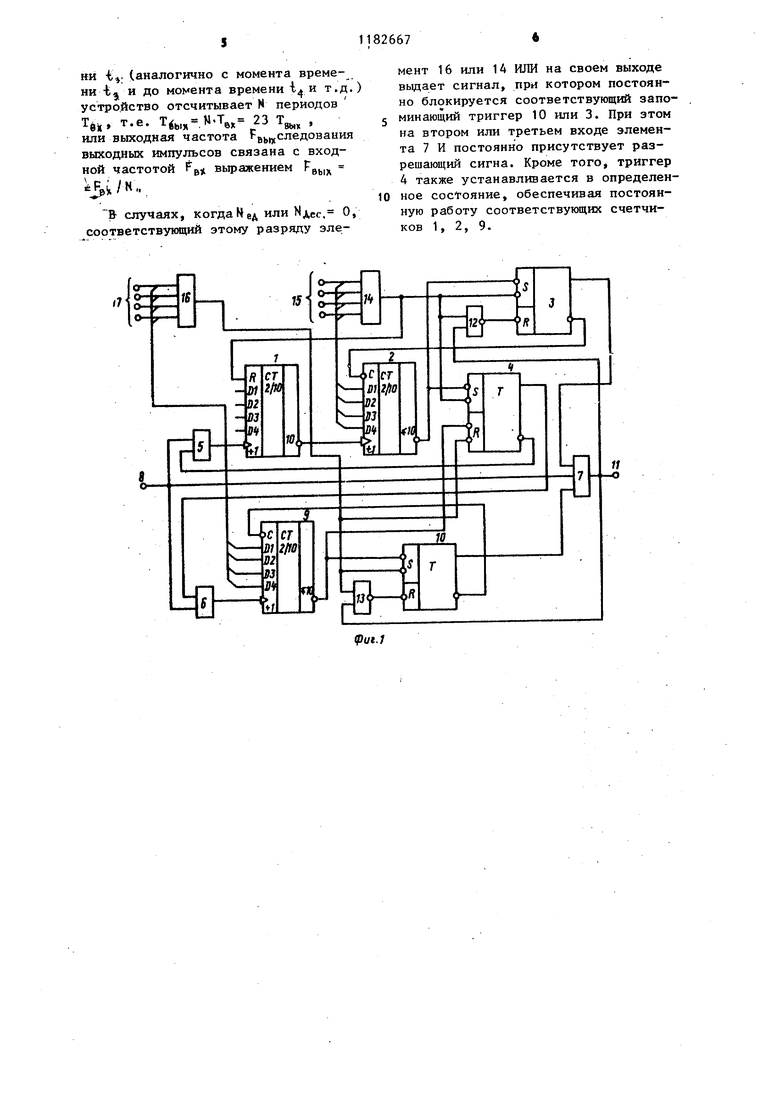

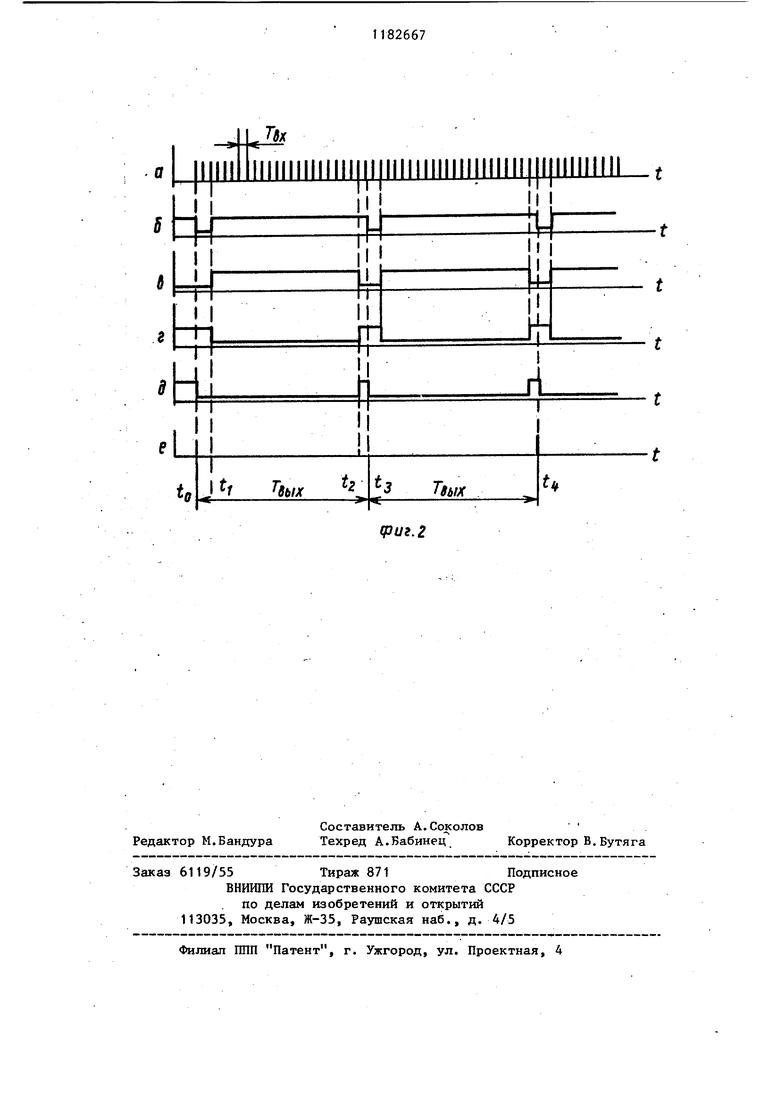

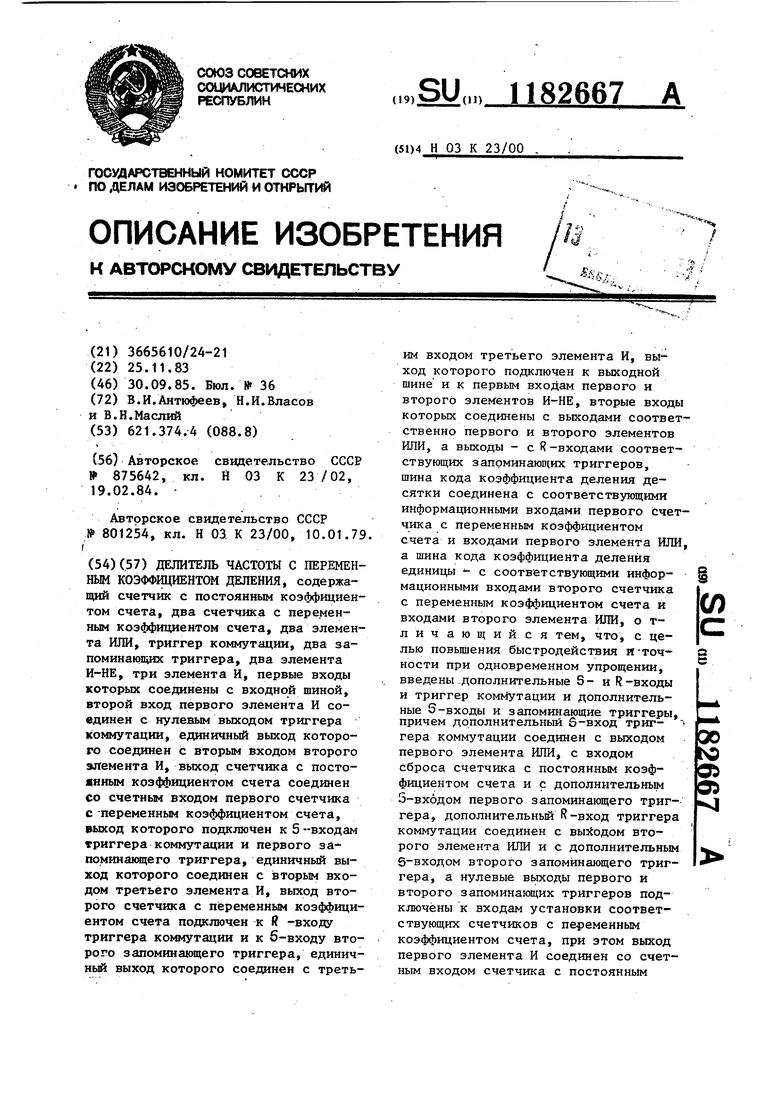

Изобретение относится к импульсной технике и может быть использова но в цифровых синтеэаторах частоты приемно-передаилцей аппаратуры, в устройствах дискретной автоматики и вычислительной техники. Цель иэобретения - повышение быс родействия и точности при одновременном упрощении устройства. На фиг. 1 приведена электрическа функциональная схема делителя часто ты с переменным коэффициент деления на фиг. 2 - временные диаграммы, по ясняющие его работу. Устройство содержит счетчик 1 с постоянным коэффициентом счета, выход которого подключен к счетному входу первого счетчика 2 с переменньм коэффициентом счета, выход кото рого соединен с S-входами первого запоминающего триггера 3 и триггера 4 коммутации, первый, второй и третий элементы 5, б и 7 И, первые вхо ды которых соединены с входной шино 8, выход первого элемента 5 И соеди нен со счётным входом счетчика 1с постоянным г.оэффициентом счета, выход второго элемента 6 И соединен со счетным входом второго счетчика 9 с переменным коэффициентом счета, выход которого подключен к R-входу Триггера 4 коммутации и S-входу второго запоминающего триггера 10, единичные выходы первого и второго запоминающих триггеров 3 и 10 подключены соответственно ко второму и третьему входам третьего элемента 7 И, выход которого подключен к выходной шине 11 и к первым входам первого и второго элементов 12 и 13 И-НЕ, выходы которых подключены к R-входам соответственно первого , и второго запоминающих триггеров 3 и 10, нулевой выход первого запоминающего триггера 3 соединен с входом установки счетчика 2 с переменлым коэффициентом счета, а нулевой выход второго запоминающего триггер 10 соединен с входом установки второго счетчика 9 с переменным коэффициентом счета, нулевой и единичный выходы триггера 4 коммутации соединен с вторыми входами соответственно первого и второго элементов 5 и 6 И, дополнительные S-входы первого запоминающего триггера 3 и триггера коммутации 4 соединены мелду собой и подключены ко второму входу второго элемента 12 И-НЕ, к входу сброса счетчика 1 с постоянным коэффициентом счета и к выходу первого элемента 14 ИЛИ, входы которого соединены с информационньп4И входами первого счетчика 2 с переменным коэффициентом счета и с шиной 15 кода коэффициента деления десятки, дополнительный S-вход второго запоминающего триггера 10 и дополнительный R-вход триггера 4 коммутации соединены с вторьм входом второго элемента 13 И-НЕ и подключены к выходу второго элемента 16 ИЛИ, входы которого соединены с информационными входами второго счетчика 9 с переменным коэффициентом счета и с шиной 17 кода коэффициента деления единиц1ьГ. : Устройство работает следующим образом. Счетчик 1 имеет постоянный коэффициент N, 10 счета. Счетчики 2 и 9 имеют переменные коэффициенты N2 и Nq счета соответственно от 1 до 10, которые устанавливаются с помощью сигналов двоичного кода на шинах 15 и .17 соответственно. Общий коэффициент деления устройства определяется из выражения N N,Nj+N,,MON.i+N, , 10 N,, N, Аес , NBA-Kg. Последовательно включенные счетчики 1 и 2 обеспечивают получение слагаемого Nдec (десятки), а счетчик 9 3слагаемого N ед (единицы) в общем коэффициенте деления N за счет пооч редкой работы счетчиков 9 и 1, 2. М менты окончания работы каждогоиз счетчиков 2 и 9 запоминаются соотве ственно 3 и 10. Очередность работы счетчиков определяется выходными си калами триггера 4, коммутирующими элементы 5 и 6 И. При этом входные импульсы с шины 8 проходят либо на счетный вход счетчика 1, либо на счетный вход счетчика 9. Очередност начала работы счетчиков произвольная и определяется начальньм состоянием триггера 4 коммутации. Рассмотрим работу устройства с учетом временной диаграммы, приведенной на фиг. 2, для которой N 23 причем Мед д 3, 10-N2 20, где N7 2. До подачи кода величины N на шинах 17 и 15 присутствуют уровни логических нулей, при этом на выходах элементов 16 и 14 ИЛИ, а соответственно и на дополнительных 6-вх дах триггеров 3 и 10 устанавливается уровень логического нуля. В этом случае оба триггера 3 и 1 устанавливаются в единичное состоявходах элемента 7 И присутствуют разрешающие сигналы. Одновременно на нулевых выходах этих триггеров, а следовательно, и на входах устано ки счетчиков 2 и 9 устанавливаются уровни логических нулей, при которы в этих счетчиках обеспечивается запись коэффициентов счета. В этом случае при подаче на шины 17 кода числа 3 и на шины 15 кода числа 2 в счетчиках 9 и 2 осуществится запись коэффициентов счета N 3 ед и N 2 Vf(. При поступлени на шину 8 входных импульсов (в момент времени -1, фиг.2а) начинается работа устройства, при которой первый входной импульс проходит на выход элемента 7 И - шину 11 и через элемент 12, 13 И-НЕ опрокидьшает по IR-входу соответственно триггеры 3 и 10 в нулевое состояние, при котором I блокируется элемент 7 И и запрещает ся дальнейшее прохождение входных импульсов на выход устройства. Одновременно этот же входной импульс поступает через элемент 6 И на счет ный вход счетчика 9, который начина ет счет числа Мд 3. При этом по 6674 второму входу элемента 6 И с единичнего выхода триггера 4 поступает разрешающий сигнал. Здесь имеется в виду, что триггер 4 в момент включения устройства установился произвольно в состояние, при котором на его единичном выходе присутствует уровень логической единицы. Это вполне g;oпycтимo, так как очередность работы счетчиков устройства на получение величины N ед + Ндсс не влияет). Согласно временной, диаграмме, первым начинает работать счетчик 9 (разряд единицы). После отсчета этим счетчиком числа Ng 3 входных импульсов на его выходе появится сигнал, опрокидывающий (момент времени -tj ) по первому S-входу триггер 10 (фиг.26) и по первому R-входу триггер 4 (фиг.2в,г) в противоположное состояние. При этом на единичном выходе последнего появляется сигнал, по вторым входам блокирующий элемент 6 И и деблокирующий элемент 5 И. В этом случае через элемент 5 И входные импульсы начинают поступать на счетный вход счетчика 1, имеющего N, 10, и счетчик 2 начинает счет числа N дес - , 10 N2 102 20 входных- импульсов. При этом на третьем входе элемента 7 И с выхода триггера 10 присутствует разрешающий сигнал в течение всего времени работы счетчиков 1 и 2. После отсчета счетчиком 2 числа Лес 20 входных импульсов, последний своим выходным сигналом опрокидывает по 5-входам триггер 3 в единичное состояние, а триггер 4 - в начальное состояние (момент времени tj) при котором соответственно на вторых входах элементов 6 и 7 И появляются разрешакщие сигналЬ. При этом следующий (очередной) входной импульс поступает на вход счетчика 9 и повторяется вышеописанный цикл работы счетчика 9, и одновременно этот же входной импульс про-Ходит через элемент 7 И на шину 11 (фиг.2е) и наR-входы триггеров 3 и 10, возвращая их в исходное состояние (момент времени tj, фиг.2д и 26 соответственно), при котором повторяется вышеописанный процесс работы устройства (начиная с момента времени ig). Таким образом, с момента времени t и до момента времени i. (аналогично с момента времени-t и до момента времени i и т.д. устройство отсчитывает И периодов Тех. т.е. T,,,.N.V 23 Т, , или выходная частота Гвь1хСледования выходных импульсов связана с входной частотой f в выражением 3i. / N. ,

& случаях, когда Мед или Нд,ес. О, соответствующий этому разряду элемент 16 или 14 ИЛИ на своем выходе выдает сигнал, при котором постоянно блокируется соответствующий запоминающий триггер 10 или 3. При этом на втором или третьем входе элемента 7 И постоянно присутствует разрешающий сигна. Кроме того, триггер 4 также устанавливается в определенное состояние, обеспечивая постоянную работу соответствующих счетчиков 1, 2, 9.

7

СГ

г/ю

и,

(риг.2

| Делитель частоты следования импульсов | 1980 |

|

SU875642A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты с переменнымКОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU801254A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| / | |||

Авторы

Даты

1985-09-30—Публикация

1983-11-25—Подача