Изобретение относится к радиотех нике и может быть ИСПОЛЬЗОЕШНО в цифровых синтезаторах частоты приемопередающей аппаратуры, в устройствах дискретной автоматики и вычислительной техники. Известен делитель частоты следования импульсов С- переменным коэффициентом деления, содержащий счетчик с., постоянным коэффициентом пересчета, первый счетчик с переменным коэффициентом пересчета с первой схемой установки, входы которых через элементы совпадения свя заны с источником входного сигнала и с выходами триггера коммутации а также триггер управления, инвертор, логические элементы И и ИЛИ, второйсчетчик с переменным коэффициентом перес.чета и с второй схемой установки m ,: В указанном устройстве суммарная задержка выходного сигнала затягивает время переключения триггера ко мутации в конце каждого цикла деления, в связи с чем не полностью используется быстродействие счетчик и в результате этого известный дели тель с переменным коэффициентом деления имеет пониженное быстродействие, а коэффициент деления имеет ог раниченный диапазон изменения .Нар более близким к предлагаемому является делитель частоты следования импульсов с переменным коэффициентом деления, содержащий элемент совпадения, триггер коммутации, еди ничный выход которого соединен с пеЕ)Вым входом выходного элемента И и два разряда, первый из которых вк чает в себя счетчик импульсов с пер менным коэффициентом счета, разрядные входы которого соединены с раз,рядными входами арифметического бло ка и с шиной установки кода коэффиц ента деления данного , а выход - с первымS-входом триггера .ЭТОГ9 же разряда, единичный выход (которого соединен с. первым входом элемента . совпадения , второй |эазря5д. состоит из первого и второгоэлементов И, счетчика импульсов с по стоянным коэффициентом счета и счётчика импульсов.с переменным коэффициентом счета, разрядные входы которого соединены с разрядными входами арифметического блока и с ьшной установки кода коэффициента деления этого же разряда, а выход .с первым 5-входом триггера данного разрйда., выход которого соединен с вторым входом элемента .совпадения, инвертора и элементы ИЛИ {2 . Недостаток известного устройства - ограниченный диапазон изменения коэффициента деления. Цель изобретения -г увеличение коэффициента деления. Поставленная цель достигается тем что в делитель частоты следования импульсов с переменным коэффициентом деления, содержащий элемент совпадения, триггер коммутахади, единичный выход которого соединен с первым входом выходного элемента И, и два разряда первый из которых включает в себя счетчик импульсов с переменным коэффициентом счета, разрядные входы которого соединены с соответствукадими разрядными входами арифметического блока и с шинами установки кода коэффициента деления данного разряда, а выход с первым 3-входом триггера того же разрядаj единичный выход которого соединен с. первым входом элемента совпадения, рторой разряд состоит из первого и второго элемента И, счетчика импульсов с постоянным коэффициентом счета, счетчика с пе.ременным коэффициентом .счета, разрядные входы которого соединены с разрядными входами арифметического блока и с шинами установки кода коэффициента деления этого же разряда, а выход - с первымS-входом триггера данного разряда, единичный выход которого соединен с вторым входрм элемента совпадения, вве-дены N-2 разряда, аналогичных второму разряду, причем в каждый разряд, начиная с второго, введены дополнительный триггер и третий элемент И,. при этом первый вход первого элемента И соединен.с входной шиной, вторым входом выходного элемента И и первым входом второго элемента И данного разряда, остальные входы - , с единичными выходами триггеров и дополнительных триггеров предыдущих разрядов, начиная с второго, а выход со счетным входом счетчика импульсов с постоянным коэффициентом счета и с первым входом третьего элемен- j та И, второй вход которого соединен; с. вторым входом второго элемента И и с единичным выходом дополнительного триггера, нулевой выход которого подключен к входу перезаписи коэффициента деления счетчика,импу.дьсов с постоянным коэффициентом счета,S-вход - к выходу счетчика импульсов с постоянным коэффициентом счета, а R -вход - к выходу третьего элемента И, счетный вход счетчика импульсов с переменным коэффициентом счета соединен с выходом второго элемента И, а вход установки коэффициента счета - с нулевым выходом .триггера, второй 3-вход которого соединен с выходом арифметического блока того же разряда, а J -вход - с нулевым выходом триггера коммутации,S -вход которого соединен с элемента совпадения, а Яввхрд. г с выходом выходного элемента И, при этом в первом разряде счетный вход счетчика импульсов с переменным коэффициентом счета соединен с входной шиной, а,вход установки коэффициента счета - с нулевым выходом триггера этого же разряда, второйS-вход которого соединен с выходом арифметического блока этого же разрядаj аR-вход - с нулевым выходом триггера коммутации

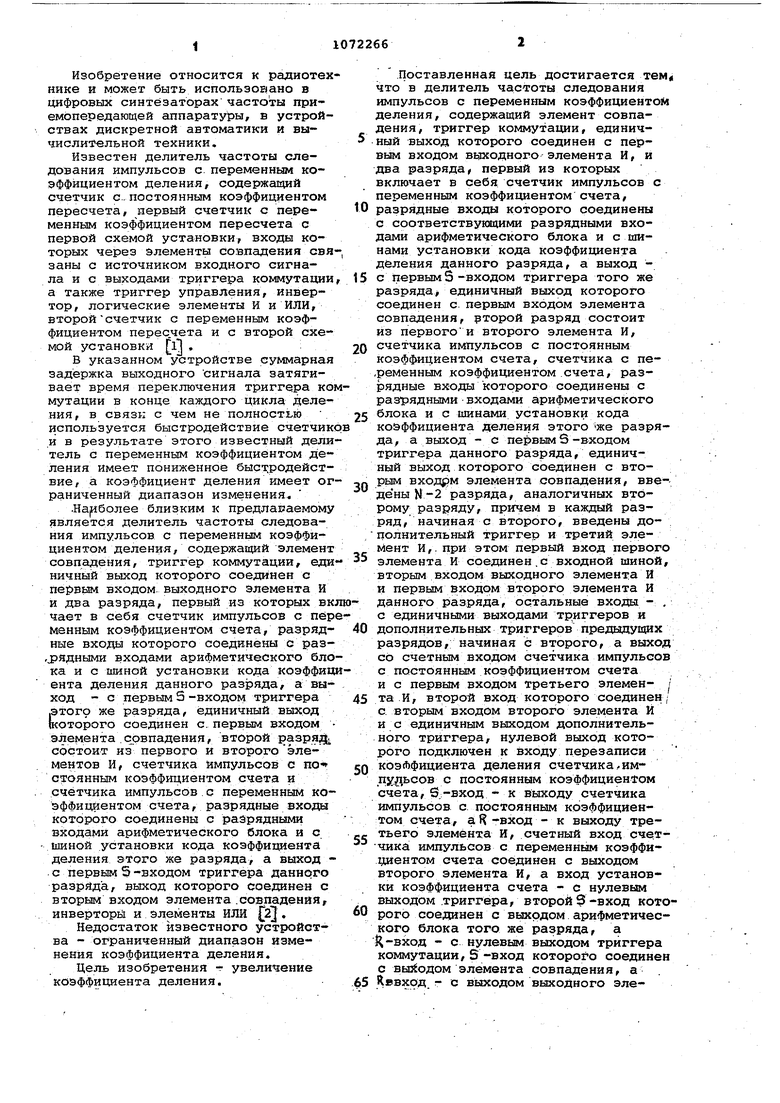

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - схема выполнения арифметического блока.

Устройство содержит с 1 по N разряды, при этом первый, разряд включает в себЯ|Счетчик 1-1 импульсов с переменным коэффнщ1ентом счета, триггер 1-2 и арифметический блок 1-3, разрядные входы Которого соединены с разрядными входами счетчика 1-1 и гииной 1-4 установки кода коэффициента деления/ а выход - с первым 5-входом триггера , разряда с 2 по Nyсостоят из счетчиков 2-1 -,N-1 импульсов с переменным коэффициентом счета, триггеров 2-2 si- 2, а рифметических блоков 2-3 - N каждаай из входов.которых соединен с одним из разрядных входов соответствующего из 2-1 - W-1 счётчика этого же разряда и одной из шин из 2-4 -N -4 установки кода коэффици ента деления -

Кроме того/ разряды с 2 по N включают в себя счетчики 2-5 -N -5 импульсов с. постоянным коэффициентом .счета f дополнительные триггеры . -1ij-6, первые элементы И 2-7 ,К-7 isTOfBie элементы И 2-8 -.N -8, третьи элементы и 2-9 - .

Делитель частоты следования имвульоозВ содержит также выходной элшчбНФ И 10, ттэиггер 11 коммута1даи.элемент 12 совпадения, входную шину 13.

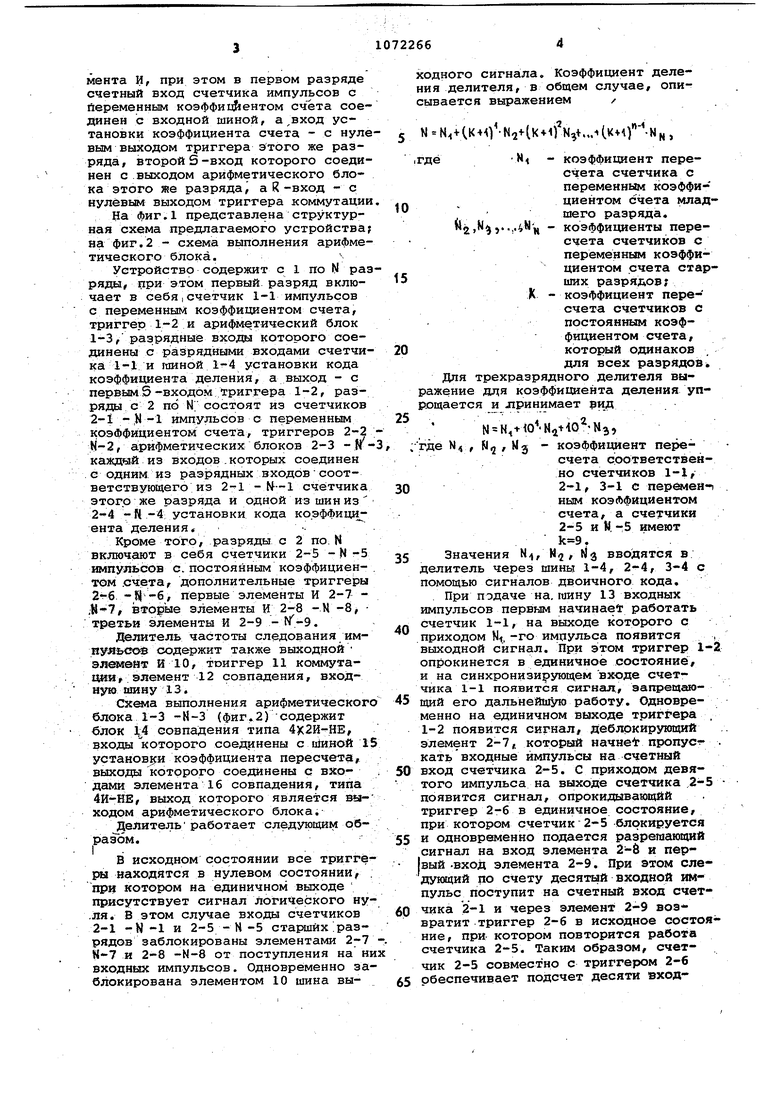

Схетда выполнения арифметического блока 1-3 -Й-3 (фиг.2) содержит блок 1;4 совпадения типа 4Х2И-НБ, входыкоторого соединены с иШной 15 установлен коэффициента пересчета, выходы IcoTOporo соединены с входами элемента 16 совпадения, типа 4И-КЕ, выход которого является вы-; ходом арифметического блока.

Делитель; работает следующим образом.

В исходном состоянии все триггера находятся в нулевом состоянииу npst котором на единичном выходе присутствует сигнал логического ну.ля. В этом случае входы счетчиков 2-1 -N-1 и 2-5 -N-5 старийх разрядов заблокированы элементами 2-7 N-7 и 2-8 -N-8 от поступления на ни входных импульсов. Одновременно заблокирована элементом 10 шина выходного сигнала. Коэффициент деления делителя, в общем случае/ описывается выражением /

5 м м,нк+л-Ка1-1к 1)к..Чки),

Hi

- коэффициент пере1гдесчета счетчика с переменным коэффициентом счета младo шего разряда. 2 ;4н коэффициенты пересчета счетчиков с переменным коэффициентом счета стар5ших разрядов;

К коэффициент пересчета счетчиков с постоянным коэффициентом счета/

0 который одинаков для всех разрядов. Для трехразрядного делителя выражение для коэффициента деления упрощается и лринимает ряд

5

N ., /где N), Nrj/Mj - коэффициент пересчета соответственно счетчиков 1-1/ 2-1, 3-1 с

0 ным коэффициентом счета/ а счетчики 2-5 и К-5 имеют ,

Значения N-(/ Н , IJg вводятся в

5 делитель через шины 1-4, 2-4/ 3-4 с помощью сигналов двоичного кода. При подаче на, шину 13 входных импульсов первым нач:инае работать счетчик 1-1, на выходе которого с

0 приходом Mi, -го импульса появится , ВЕЛходной сигнал. При этом триггер 1-12 опрокинется в единичное состояние/ и на синхронизирующем входе счетчика 1-1 появится сигнал/ запрещаю5щий его дальнейшую работу. Одновременно на единичном выходе триггера , 1-2 появится сигнал/ деблокирующий элемент 2-7, который начнет пропус- - . кать входные импульсы на счетный

0 вход счетчика 2-5. С приходом девятого импульса на выходе счетчика 2-5 появится сигнал/ опрокидагвающйй триггер 2-6 в единичное состояние/ при котором счетчик 2-5 блокируется и одновременно подается разрешающий

5 сигнал на вход элемента 2-S и -вход элемента 2-9. При этом следующий по счету десятый входной импульс поступит на счетный вход счетчика 2-1 и через элемент 2-9 воз0вратит триггер 2-6 в исходное состояние, при котором повторятся работа счетчика 2-5. Таким образом, счетчик 2-5 совместно с триггером 2-6 обеспечивает подсчет десяти вход5 .ных импульсов, последний из которых поступает на счетный вход счетчика 2-1. Последний, после, подсчета чис,ла Н2 импульсов, опрокинет в единич ное состояние триггер 2-2. При этом счетчик 2 заблокируется по входу ус тановки коэффициента счета, а на второй вход (в следующем разряде) элемента 3-7 поступит разрешающий, сигнал с единичного выхода триггера 2-2. В этом случае поступление разрешающего сигнала на вход элемента 3-7 с единичного выхода триггера 2-6 обеспечивает прохождение на счетный вход счетчика 3-5 каждого десятого входного импульса, поступающего на вход элемента 3-7. Дальнейшая работа элементов третьего ра ряда аналогична описанной работе элементов второго разряда, причем после прохождения числа N импульсов триггер 3-2 опрокинется в единичное состояние и на всех входах элемента 12 будут присутствовать разрешающие сигналы, при которых на единичном входе триггера 11 появится сигнал, переключающий его в , единичное состояние. В этом случае на первом входе элемента 10 появится разрешающий сигнал, обеспечивающий прохождение N-го входного импульса на выход делителя. Триггеры 1-2, 2-2, N -2 возвращаются в исходное состояние сигналом с нулевого выхода триггера. 11, д. сам - выходным импульсом делителя, поступающим на его R -вход. Таким образом, каждый предыдущий разряд делителя дает разрешение для работы последующего разряда, при этом каждый разряд работает от входных импульсов. Если в каком-либо разряде, величина коэффициента деления , то триггер этого разряда переключается сигналом с выхода арифметического блока того же разряда, а счетчик с переменным коэффициентом .счета этого разряда из работы исключается. Использование в каждом старшем разряде дополнительного триггера от личает предлагаемый делитель частоты с переменным коэффициентом деления от устройства-гпрототипа. Данный делитель частоты с переменным коэффициентом деления обла;дает рядом технических преимуществ по сравнению с базовым объектом. Так базовый объект имеет общий коэффициент деления N (б), описываемый выражением ,..Н54Мз Ыдёс-ьНед, (1) в Котором величины Nj и Ng могут принимать значения от 1 до 10. При этом общий максимальный коэлфидаент деления N (б) оказывается равным 1К 10Nc -fNo 10-ЮИО Ш2.| 5)макс макс макс .. В предлагаемом делителе частоты с переменным коэффициентом деления общий коэффициент деления N описывается выражением , (kH)N2HKM -M.yt..(KM)-.NN, (J где k 9 -.коэффициент пересчета счетчиков с постоянным коэффициентом счета; N,,N,,N,,.,., коэффициенты пересчета счетчиков с переменным коэффициентом счета, причем каждый из них может принимать значение от 1 до 10 В этом случае выражение (3) для максимального значения коэффициента деления JMOIKC. примет вид .j lO+10. 10 -ЫО. 10 + . . .+10 ) где п - количество десятичных разрядов заданного значения числа в десятичной системе счисления. Из сравнения выражений (2) и (4) следует, что если в базовом объекте NC6)waKc. 110/ то в предлагаемом устройстве-N g NCS j ja g и принципиально ничем не ограничено, так как величина п может принимать любое целочисленное значение. Конструктивно в предлагаемом делителе частоты количество разрядов (п) ограничивается числом входов реального элемента 12 совпадения. Максимальное количество входов такого типа элемента (из отечественных серийных микросхем) равно . С учетом вышеизложенного и согласно вьгражению (4) максимальный коэффициент деления предлагаемого делителя частоты определяется как NMa КС 10+10-1 о +10 «102 + . ..+10 . 10+10 +10 +... 111 110 Д5;. где . Из сра внения 2 и 5. следует, что практически (с .учетом современной отечественной элементной базы) выигрыш в увеличении коэффициента делег:ия при использовании .предлагаемого делителя частоты, по сравнению с базовым объектом, составит NMQKC 111 III 110 ,п,п,л, -, п6 /Х.Ч т&П5 1010101 (6) при этом быстродействие предлага.емого устройстване понижается.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1547057A2 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1732465A1 |

| Делитель частоты с переменным коэффициентом деления | 1977 |

|

SU678673A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1160560A1 |

| Устройство для преобразования средней частоты пачки импульсов | 1980 |

|

SU906000A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1985 |

|

SU1292177A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1307587A1 |

| Устройство для контроля качества канала связи | 1979 |

|

SU856023A1 |

| Делитель частоты следования импульсов | 1982 |

|

SU1045400A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕЛОВАНИЯ ИМПУЛЬСОВ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ, содержащий элемент совпадения, триггер коммутации, единичный выход которого соединен с первым входом.выходного элемента И и два разряда, первый из которых включает в себя счетчик импульсов .с переменным коэффициентом счета, разрядные входы которого соединены с соответствующими разрядными входами арифметического блока и шинами уста-ч новки кода коэффициента деления данного разряда, а выход - спеременным S-входом триггера того же разряда, единичный выход которого соединен с первым входом элемента совпадения, в.торой разряд состоит из первого и второго элементов И, счетчика импульсов с постоянным коэффициентом счета и счетчика импульсов с г.--Переменным коэффициентом счета, разрядные входы которого соединены с соответствующими разрядными входами арифметического блока и шинами установки кода коэффициента деления этого же разряда, а выход с первым 5-входом триггера данного разряда, единичный выход которого соединен с вторым входом элемента совпадения, отличающийс я тем, что, с целью увеличения коэффициента деления, в него введены N -2 разряда, аналогичных второму разряду, в каждый разряд, начиная с второго, введены дополнительный триггер и третий элемент И, при.этом первый йход первого элемента И соединен с входной шиной, вторым входом выходного элемента И и первым входом:второго элемента И данного разряда, остальные входы с единичными выходами триггеров и дополнительных триггеров предыдущих разрядов, начиная с вторюго, а выход - со счетным входом счетчика импульсов с постоянным коэффихщентом счета и с первым входом третьего элемента И, второй вход которого соединен с вторым входом второго элемента И и с единичным выходом . дополнительного триггера, нулевой j выход которого подключен к входу ne-j резаписи коэффициента деления счетчика импульсов с постоянным КОЭФФИ- циентом счета, S-вход - к выходу jwn . счетчика импульсов с постоянным коэффициентом счета, а I -вход - к выхо-й : ду третьего элемента И, счетный вход. счетчика импульсов с переменным коэффициентом счета соединен с выходом второго элемента И, а вход э установки коэффициента счета - с нулевым ВЕЛходом триггера, второй 5-вход которого соединен с выходом ю арифметического блока того же разряда , а i -вход - с нулевым выходом ю триггера коммутации ,§-вход которого, соединен с выходом элемента совпадения, а R-вход - с выходом вькодного элемента И, при этом в первом разряде счетный вход счетчика импульсов с переменным коэффициентом счета соединен с входной шиной, а вход установки коэффициента, счета с нулевым выхЪдом триггера этого же разряда, - второй З-вход которого соединен с выходом арифметического блока этого же разряда, а R.-вход - . с нулевым выходом триггера коммута.ции.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ДЕЛИТЕЛЬ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМДЕЛЕНИЯ | 1972 |

|

SU421132A1 |

| rf: , 2..Авторское свидетельство СССР № 801254, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-02-07—Публикация

1982-04-08—Подача