:о

2. Делитель частоты по, п. 1, отличающийся тем, что управляемый делитель частоты с коэффициентом деления К+1 содержит счетные триггеры, единичный выход каждого из которых подключен к счетному входу последующего счетного триггера нулевой выход каждого счетного триггера соединен с первым входом соответствующего элемента И-НЕ, вторые входы которых соединены с соответствующими управляющими входами, выходы элементов И-НЕ подключещл к соответствующим входам многовхоДового элемента И-НЕ, вькод которого соединен с входом управления коммутатора импульсов, запоминающего сигнал управления, вход коммутации которого соединен с сигнальным входом, первый выход коммутатора импульсов, запоминающего сигнал управления, подключён к счетному входу первого счетного триггера, а второй выход соединен с нулевыми входами йсех счетных триггеров и с сигнальным выходом управляемого делителя частоты с коэффициентом деления К+1.

3. Делитель частоты по п, 2, отличающийся тем, что коммутатор импульсов, запоминающий сигнал управления делителя частоты с коэффициентом деления К+1 содержит первый элемент И-НЕ, выход которого соединен с первыми входами второго и третьего элементов И-НЕ, второй вход второго элемента- И-НЕ соединен с входом зпправления коммутатора, запоминакнцего сигнал управления , и через первый инвертор - с первым входом четвертого элемента И-НЕ, второй вход которого подключен к выходу третьего элемента И-НЕ и к первому входу первого элемента И-НЕ, второй вход которого соединен с втот рым входом третьего элемента И-НЕ и с выходом второго инвертора, выходы второго и четвертого элементов И-НЕ подключены к третьим входам соответственно первого и третьего элементов И-НЕ, а вход второго инвертора соединен с входом коммутации коммутатора, запоминающего сигнал управления, первый и второй, выходы которого соединены соответственно с выходами третьего и первого элементов И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты | 1989 |

|

SU1698985A1 |

| Управляемый делитель частоты | 1988 |

|

SU1598175A2 |

| Преобразователь частота-код | 1983 |

|

SU1129543A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Генератор функций | 1984 |

|

SU1166148A2 |

| Устройство для измерения параметров радиоимпульсов | 1980 |

|

SU938206A1 |

| Устройство для управления шаговым двигателем | 1990 |

|

SU1693708A1 |

| Преобразователь отношения двух частот в код | 1976 |

|

SU660231A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

1. УПPABЛЯE ЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С КОЭФФИЩ1ЕНТОМДЕЛЕНИЯ Hi, содержащий первый управляемый делитель частоты, сигнальный выход которого соединен с входом второго управляемого делителя частоты с коэффициентом деления К, управляющие входы которого соединены с шинами управления, сигнальный вход первого управляемого делителя частоты соединен с входной шиной, а выход второго управляемого делителя частоты с коэффициентом деления К соединен с выходной щиной, отли-чающийся тем, что, с целью упрощения, поразрядные выходы второго управляемого делителя частоты с коэффициентом дек ления К соединены с управляющими входами первого управляемого делителя частоты, коэффициент деления котороSf го выбран равным К+1.

Изобретение относится к импульсной технике и может быть использовано в автоматика и вычислительной технике.

Известен управляемый делитель тоты (УДЧ) с коэффициентом деления

K

i, содержащий два УДЧ с коэффициен . тами деления К, вычитатель импульса

из серии: элементы И, элементы ИЛИ, элемент НЕ и шины управления lj.

Недостаток известного технического решения заключается в сложности его схемотехнической реализации.

Наиболее близким к изобретению

является УДЧ с коэффициентом деле к.,:

ния2Г1, содержащий три УДЧ с коэффициентами деления К и счетчики импульсов 2.20 Однако и данное техническое решение характеризуется

сложностью его схемотехнической реализации.

Цель изоЬретения - упрощение управляемого делителя частоты с коэф... К фициентом деления Hi.

Поставленная цель достигается тем что в управляемом делителе час ... к ,

тоты с коэффициентом деления Si.i со1

держащем первый управляемьгй делитель частоты, сигнальный выход которого соединен с входом второго управляемого делителя частоты с коэффициентом деления К, управляющие входы которого соединены с шинами управления сигнальный вход первого управляемого делителя частоты соединен с входной шиной, а выхрд второго управляемого делителя частоты с коэффициентом деления К соединен с;выходной шиной.

поразрядные выходы второго управлявмого делителя частоты с коэффициентом деления К соединены с управляющими входами первого управляемого делителя, частоты, коэффициент деления которого выбран равным К+1, причем управляемый делитель частоты с коэффициентом деления К+1 содержит счетные триггеры, единичный выход каждого из которых подключен к счетному вхрду последующего счетного триггера нулевой выход каждого счетного триггера соединен с первым входом соответствующего элемента И-НЕ, вторые входы которых соединены с соответствукящши управляющими входами, выходы элементов И-НЕ подключены к соответствующим входам многовходового элемента И-НЕ, выход которого соединен с входом управления коммутатора импульсов, запоминающего сигнал управления, вход коммутации которого соединен с сигнальным входом, первый выход коммутатора импульсов, запоминающего сигнал упрайления, подключен к счетному входу первого счетного триггера, а второй выход соединен с нулевыми входами всех счетных триггеров и с сигнальным выходом управляемого делителя частоты с коэффициентом деления К+1, а коммутатор импульсов, запоминающий сигнал управления, делитель частоты с коэффициентом деления К+1 содержит первый элемент И-НЕ, выход которого соединен с первыми входаь и второго и третьего элементов И-НЕ, второй вход второго элемента И-НЕ соединен с входом управления коммутатора, запоминающего сигнал управления, и через первый инвертор - с первым входом четвертого элемента И-НЕ, второй вход которого подключен к выходу третьего элемента И-НЕ и к первому входу первого элемента И-НЕ, второй вход которого соединен с вторым

входом третьего элемента И-НЕ и с -I . выходом второго инвертора, выходы

второго и четвертого элементов И-НЕ подключены к третьим входам соответственно первого и третьего эле- ментов И-HEj а вход второго инвертора соединен с входом коммутации коммутатора, запоминающего сигнал управления, первый и второй выходы которого соединены соответственно с выходами третьего и первого элементов И-НЕ.

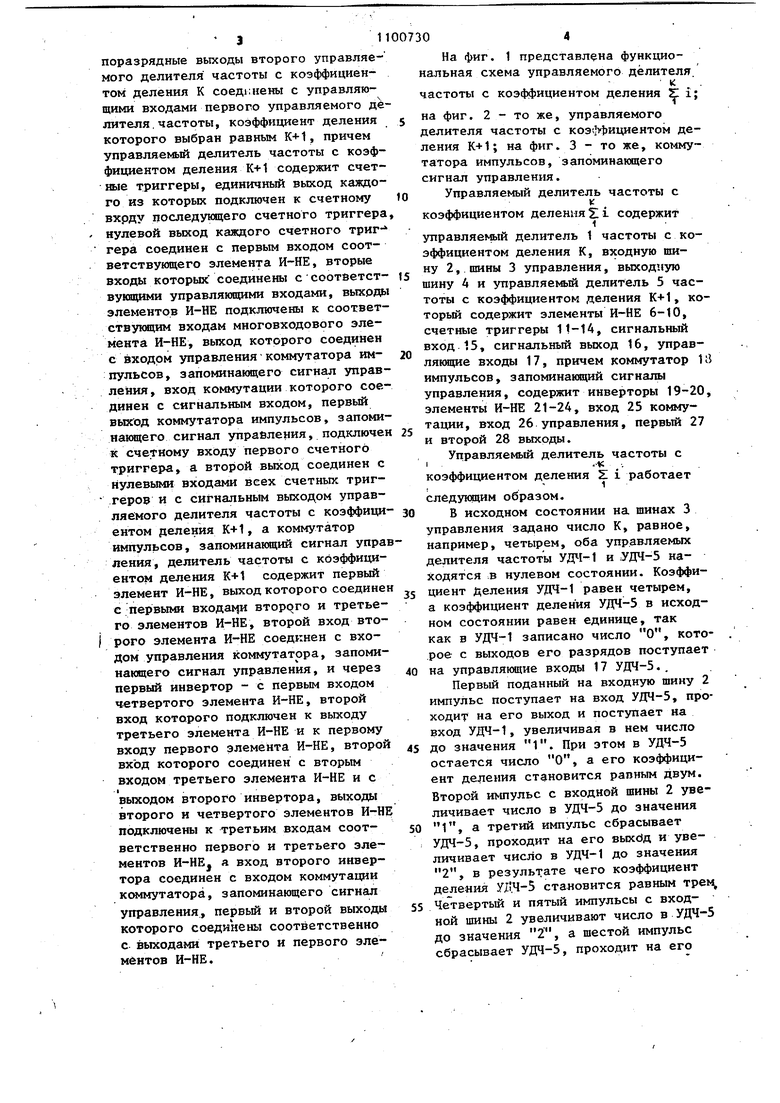

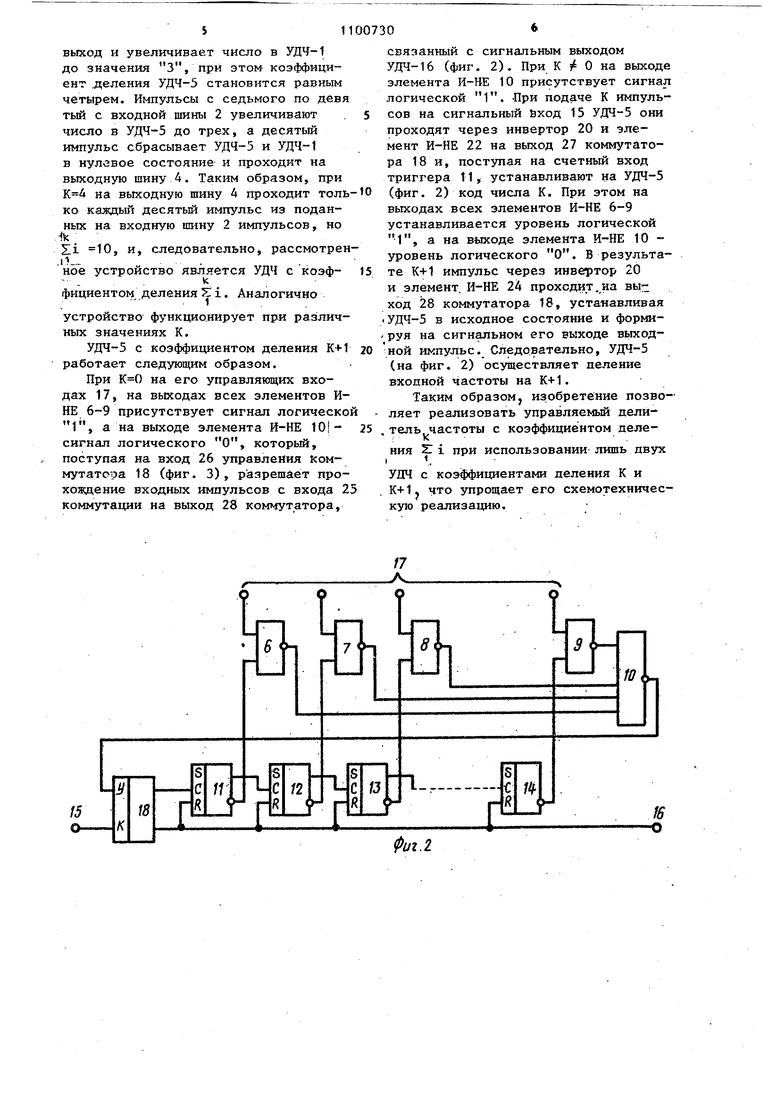

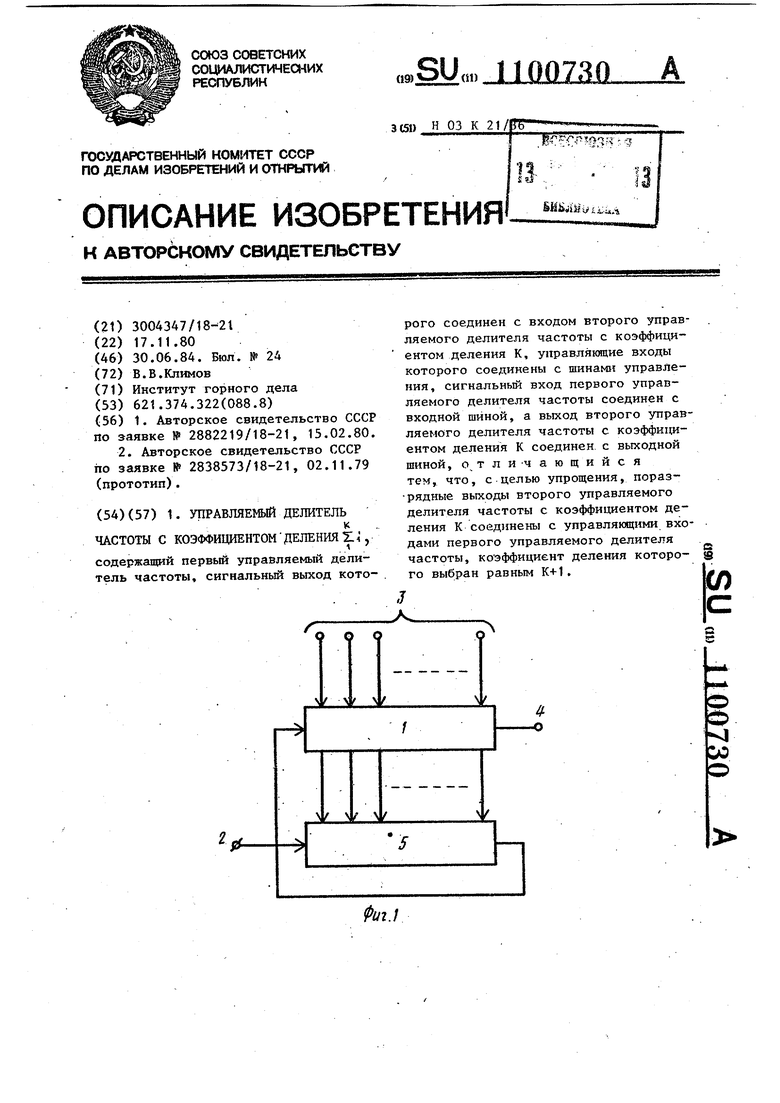

На фиг. 1 представлена функциональная схема управляемого делителя

к частоты с коэффициентом деления

i;

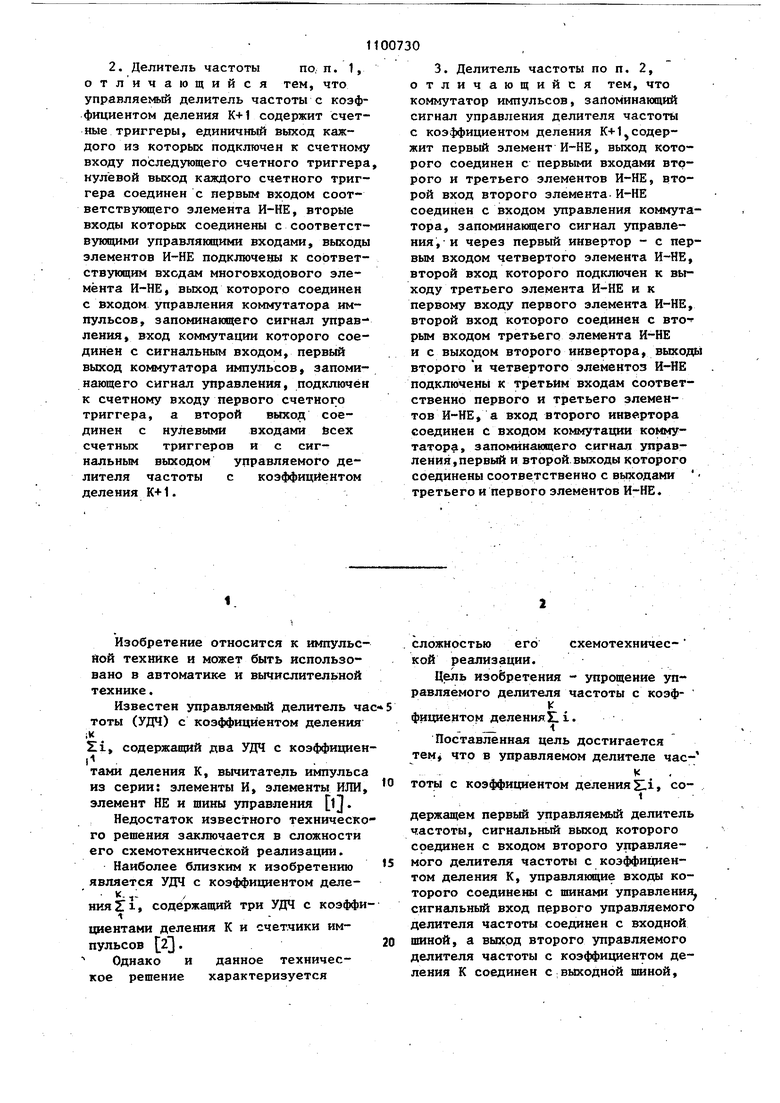

на фиг. 2 - то же, управляемого делителя частоты с коэ ициентом деления К+1; на фиг. 3 - то же, коммутатора импульсов, запоминагацего сигнал управления.

Управляемый делитель частоты с

к коэффициентом деления 2 i содержит

управляе1Ф1й делитель 1 частоты с коэффициентом деления К, входную шину 2 , шины 3 управления, выходмую шину 4 и управляемый делитель 5 частоты с коэффициентом деления К+1, который содержит элементы И-НЕ 6-10, счетные триггеры 11-14, сигнальный вход 15, сигнальный выход 16, управлякшще входы 17, причем коммутатор 1 импульсов, запоминающий сигнагш управления, содержит инверторы 19-20 элементы И-НЕ 21-24, вход 25 коммутации, вход 26 управления, первый 27

и второй 28 .

Управляемый делитель частоты с

Z i

коэффициентом деления

работает

1

следуиядим образом.

В исходном состоянии на шинах 3 управления задано число К, равное, например, четырем, оба управляемых делителя частоты УДЧ-1 и :УДЧ-5 находятся в нулевом состоянии. Коэффициент Деления УДЧ-1 равен четырем, а коэффициент деления УДЧ-5 в исходном состоянии равен единице, так как в УДЧ-1 записано число О, которое с выходов его разрядов поступает на управляющие входы 17 УДЧ-5..

Первый поданный на входную шину 2 импульс поступает на вход УДЧ-5, проходит на его выход и поступает на вход УДЧ-1, увеличивая в нем число до значения 1. При этом в УДЧ-5 остается число О, а его коэффициент деления становится рапным двум. Второй импульс с входной шины 2 увеличивает число в УДЧ-5 до значения 1, а третий импульс сбрасывает УДЧ-5, проходит на его выхбд и увеличивает число в УДЧ-1 до значения 2, в результате чего коэффициент деления УДЧ-5 становится равным трец Че твертый и пятый импульсы с входной шины 2 увеличивают число в УДЧ-5

а шестой импульс

до значения

сбрасывает УДЧ-5, проходит на его 5 выход и увеличивает число в УДЧ-1 до значения 3, при этом коэффициент деления УДЧ-5 становится равным четырем. Импульсы с седьмого по дев тый с входной шины 2 увеличивают число в УДЧ-5 до трех, а десятый импульс сбрасывает УДЧ-5 и УДЧ-1 в нулевое состояние и проходит на выходную шину 4. Таким образом, при на выходную шину А проходит тол ко каждьц десятый импульс из поданных на входную шину 2 импульсов, но -fk Ei 10, и следовательно, рассмотре .ii ное устройство является УДЧ с коэф - , . фициентом деления S i. Аналогично устройство функционирует при различных значениях К. УДЧ-5 с коэффициентом деления K+ работает следующим образом. При на его управляющих входах 17, на выходах всех элементов ИНЕ 6-9 присутствует сигнал логическо 1, а на выходе элемента И-НЕ 10|сигнал логического О, который, поступая на вход 26 управления коммутатора 18 (фиг. 3), разрешает прохождение входных импульсов с входа 2 коммутации на выход 28 коммутатора. 0 связанный с сигнальным выходом УДЧ-16 (фиг. 2). При К О на выходе элемента И-НЕ 10 присутствует сигнал логической 1. -При подаче К импульсов на сигнальный йход 15 УДЧ-5 они проходят через инвертор 20 и элемент И-НЕ 22 на выход 27 коммутатора 18 и, поступая на счетный вход триггера t1, устанавливают на УДЧ-5 (фиг. 2) код числа К. При этом на выходах всех элементов И-НЕ 6-9 устанавливается уровень логической 1, а на выходе элемента И-НЕ 10 уровень логического О. В результате К+1 импульс через инвертор 20 и элемент. И-НЕ 24 проходит.на выход 28 коммутатора 18, устанавливая УДЧ-5 в исходное состояние и формируя на сигнальном его выходе выходной импульс. Следовательно, УДЧ-5 (на фиг. 2) осуществляет деление входной частоты на К+1. Таким образом, изобретение позволяет реализовать управляемый делйтель частоты с коэффициентом деления 5: i при использовании лишь двух УДЧ с коэффициентами деления К и К+1. цто упрощает его схемотехническую реализацию.

/99LQ

27

.

о

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР по заявке № 2882219/18-21, 15.02.80 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ принудительного сброса груза и устройство для его осуществления | 2023 |

|

RU2838573C1 |

Авторы

Даты

1984-06-30—Публикация

1980-11-17—Подача