1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для автом тической проверки точности работы интерполяторов, предназначенны для интерполяции сигналов изме-г рительных преобразователей перемещений.

Известно устройство для проверки интерполятора, содержащее блок управления, блок памяти и логический блок 1.

Недостатками устройства являются низкая точность работы и ограниченные-функциональные возможности.

Наиболее близКИМ по технической сущности к изобретению является устройство для контроля интерполятора, содержащее блок регистрации, генератор импульсов, выхЬд которого соед|1н ен со входом делителя частоты и с ,входом триггера, подключенного другим входом к выходу интерполятора 2.

Недостатком этого устройства является низкое быстродействие.

.Целью изобретения является повышение точности работы устройстваПоставленная цель достигается тем что устройство содержит интегратор, частотные фильтры и фазорасщепитель, вход которого подключен к выходу делителя частоты, выходы - через частотные фильтры ко входам интерполятора, вход интегратора соединен с выходом триггера, а выход - со- входом блока регистра.ции.

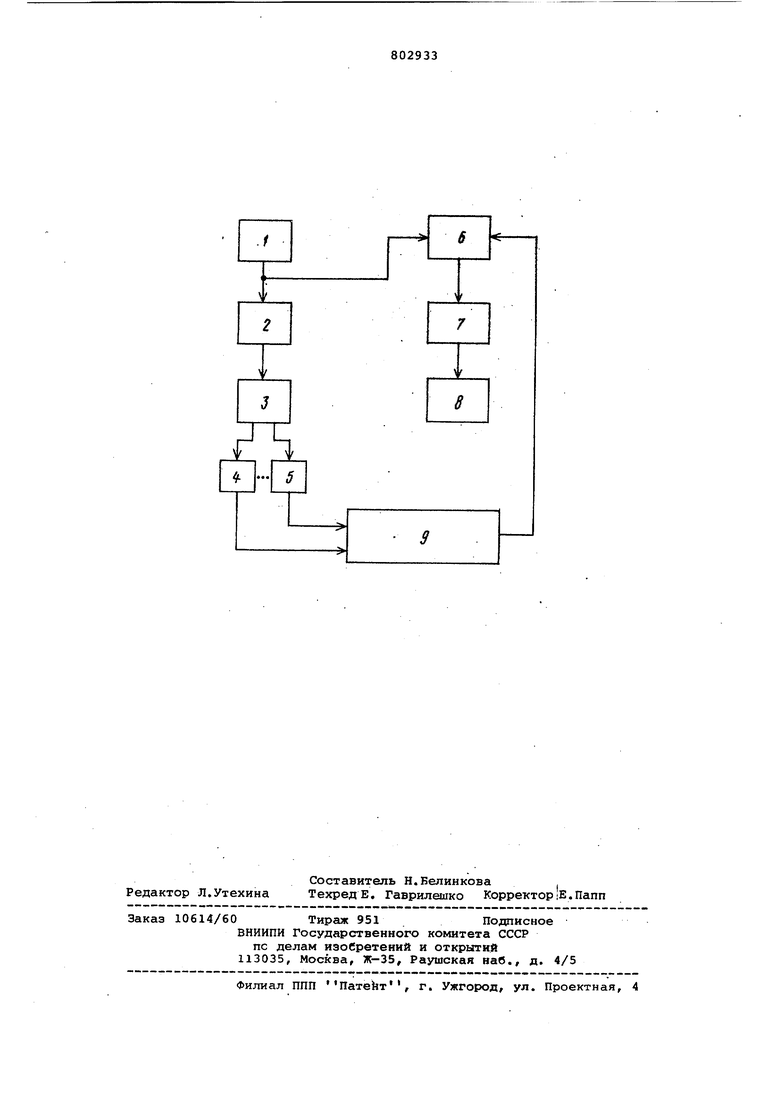

функциональная схема устройства

0 показана на чертеже.

Устройство содержит генератор импульсов-. 1 f делитель частоты 2, фазорасщепитель 3, частотные фильтjaj 4 и 5, триггер 6, интегратор 7,

5 блок регистрации 8 и интерполятор 9,

Устройство работает следующим

образом.

Генератор 1 формирует последова0тельность импульсов с частотой fe. Эта частота делится на ti в делителе 2 Далее сигнал поступает на фазорасщепитель 3, на выходах которого рбразуются две последоват(эльности

5 ймпуЛ1Гсов - синусоидальная и косинусоидальная. Принцип работы фазоврЪщателя 3 может быть любым. На- пример, он может быть построен на двух счетных триггерах,каждый из

0 которых срабатывает либо от переднего, либо от заднего фронтов прямо/ угольных сигналов частоты fo/n, поступающих на вход фазорасщепите/ ля 3, При этом его выходные ортогональные сигналы имеют частоту в два раза меньшую, т.е. /2п.:

На выходах фазорасщепителя установлены соответственно фильтры 4 и 5, которые выделяют первую гармонику, т„е. на их выходах образуются соответственно синусоидальный и коси ну соидальный гармонические сигналы. Эти два сигнала поступают на входа проверяемого интерполятора 9. На его выходе .. (как устройства внутришагового делителя) образуется последовательность коротких импульсов, расстояние между которыми по оси времени в некоторое число раз (равное коэффициенту интерполяции) меньше периода входного сигнала. Поэтому практически интерполятор представляет собой умножитель частоты. Если предположить, что фазорасщепитель 3 обеспечивает разделение фаз без изменения частоты, то на вход интерполятора поступают ортогональные сигналы частоты fo/n. При коэЛфициенте интерполяции, равном ti, -на его выходе последовательность коротких импульсов имеет частоту fo . Понятно, что коэфйициент интерполяции проверяемого интерполятора известен-, и исходя из него, выбирается коэффициент деления делителя 2. Сигналы с выхода интерполятора поступают на один из входов триггера б, на другой вход которого подается прямоугольное напряжение с выхода генератора 1. В триггере б Фронтом Гнапример, .-передним) импульсов с генератора 1 триггер, переводите из исходного логического состояния в другое, а, фронтом импульсов с выхода контролируемого интерполятора 9 триггер б возвращается обратно в исходное логическое состояние. Т.е.,если интерполятор 9 не облгщает погрешностью {это значит, что расстояние по оси времени между короткими импульсами на выходе интерполятора одинаковы, т.е. внутришаговое (внутри периода) деление производится точно и равномерно, то на выходе триггера б йюрмируются прямоугольные импульсм одинаковой длительности. Поэтому на выходе интегратора 7 оР аэуется постоянное напряжение, котс«рое принимается занулевую линиюотсчета. Она регистрируется самопишущим прибором .блока 8 (или другим регистрирую«им устройством) , под ключенныМнй- выход интегратора 7.

Если интерполятор характеризуется погрешностью, т.е. расстояния по оси времени между короткими импульсами на выходе неодинаковы (внутришаговое деление производится неравномерно) , то прямоугольные импульсы на выходе триггера б имеют неодинаковую длительность, которая меняется в течение .периода g пропорционально погроиности. Т.е. на выходе триггера имеет мести , ишротно-импульсная модуляция (ШИМ). При интегрировании ШИМ-импульсов на выходе интегратора 7 образуется кривая погрешности, фиксируемая блоком 8. Запись этой кривой на самописец осуществляется автоматически. Интерполятор предназначен для внутришагового деления шага. измерительного преобразователя

5 перемещений.

Например, круговой Лотоэлектрический измерительный преобразователь, имеет 10800 штрихов - это значит, что величина шага равна

0 120,угловым секундам, при интepfтoляции на 40 частей - величина шага на выходе интерполятора равна 3 угловым секундам. Триггер 6 и интегратор 7 практически чувствительг

5 ны к одному градусу, т.е. к 1/360 части шага, что в данном случае составляет 1/120 часть угловой секунды, т.е. погре1чность интерполятора (например, предназначенного

0 для работы с измерительными преобразователйми с указсСяным числом штрихов), регистрируется с точностью, меньшей сотой доли угловой секунды. При этом запись информации осуществляется автоматически на самописце.

Таким образом, точность работы предложенно.го устройства значительно повышена.

Формула изобретения

Устройство для контроля интерполятора, содержащее блок регистрации, генератор импульсов, выход

которого соединен со входом делителя частоты и с первым входом триг гера, подключенного другим входом к выходу интерполятора, о т л и чающееся тем, что, с целью повышения точности работы устройства, оно содержит интегратор, частотные фильтры и фазорасщепитель, вход которого подключен к выходу

делителя частоты, выходы - через частотные фильтры ко входам интерполятора, вход интегратора соединен с выходом триггера, а выход со входом блока регистрации. Источники информации,

принятые; во внимание при экспертизе

1.Авторское свидетельство СССР №,392535, кл.- G 06 G 7/30, 1970.

2.Авторское свидетельство СССР № 339930, кл. G 06 G 7/30, 1970

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интерполятора | 1981 |

|

SU1013913A2 |

| Устройство для контроля интерполятора | 1983 |

|

SU1107109A2 |

| Преобразователь угла поворота вала в код | 1981 |

|

SU963034A1 |

| Преобразователь перемещения в код | 1988 |

|

SU1562969A1 |

| Преобразователь перемещения в код | 1981 |

|

SU997064A2 |

| Устройство для интерполяции сигналов измерительных преобразователей | 1977 |

|

SU752139A1 |

| Преобразователь перемещения в код | 1980 |

|

SU911583A1 |

| Преобразователь код-частота гармонического сигнала | 1984 |

|

SU1195449A2 |

| Датчик скорости, направления вращения и углового положения вала | 1988 |

|

SU1654972A1 |

| Устройство для контроля преобразователей угла поворота вала в код | 1982 |

|

SU1027749A1 |

Авторы

Даты

1981-02-07—Публикация

1979-03-26—Подача