(54) СПОСОБ СИНХРОНИЗАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации | 1981 |

|

SU1159173A1 |

| Устройство синхронизации | 1981 |

|

SU1125759A1 |

| Устройство дискретной автоподстройки фазы тактовых импульсов | 1983 |

|

SU1141581A1 |

| Устройство синхронизации | 1979 |

|

SU873440A1 |

| Устройство дискретной автоподстройки фазы тактовых импульсов | 1981 |

|

SU1062878A1 |

| ВСЕСОЮаНАЯ i | 1973 |

|

SU372717A1 |

| Устройство дискретной фазовой синхронизации | 1985 |

|

SU1338097A1 |

| Устройство автоподстройки фазы тактовых импульсов | 1986 |

|

SU1527718A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| Способ автоподстройки фазы тактовых импульсов и устройство для его осуществления | 1976 |

|

SU640436A1 |

t

Изобретение относится к технике связи и может использоваться для дискретной автоподстройки фазы тактовых импульсов местного генератора под фазу значащих моментов принимаемого сигнала.

Известен способ синхронизации, заключающийся в формировании основной опорной последовательности импульсов, формировании m опорных последовательностей, сдвинутых одна относительно другой на величину -к формировании тактовых импульсов путем деления частоты одной из опорных последовательностей, определении направления и величины отклонения фазы тактовых импульсов от фазы значащих моментов принимаемого сигнала и коррекции фазы тактовых импульсов 1.

Известно также устройство для осуществления способа, содержащее последовательно соединенные блок выделения значащих моментов и фазовый дискриминатор и последовательно соединенные задающий генератор и формирователь опорных последовательностей, а также делитель частоты, выход которого подключен к другому входу фазового дискриминатора и блок исключения, выход /которого подключен к входу делителя частоты, причем выход задающего генератора подключен к другому входу блока выделения значащих моментов и третьему входу фазового дискриминатора 2.

Однако, такой способ и устройство для его осуществления имеют невысокую точность синхронизации.

Цель изобретения - повыщение точности синхронизации.

Для этого в способе синхронизации, заключающемся в формировании основной опорной последовательности импульсов, формировании m опорных последовательностей, сдвинутых одна относительно другой на величину п формировании тактовых импульсов путем деления частоты одной из опорных последовательностей, определении направления и величины отклонения фазы тактовых импульсов от фазы значащих моментов принимаемого сигнала и коррекции фазы тактовых импульсов перед коррекцией фазы тактовых импульсов, определяют момент времени начала и окончания процесса выбора последовательностей, участвующих в коррекции и выбирают число последовательностей и сдвиг по фазе между ними и запоминают последнюю последовательность

из выбранных, а в устройство для осуществления способа, содержащее последовательно соединенные блок выделения значащих моментов и фазовый дискриминатор и последовательно соединенные задающий генератор и формирователь опорных последовательностей, а также делитель частоты, выход которого :одключен к другому входу фазового дискриминатора и блок исключения, выход которого подключен к входу делителя частоты, причем выход задающего генератора подключен к другому входу блока выделения значащих моментов и третьему входу фазового дискриминатора, введены блок выбора опорной последовательности, формирователь сигнала переключения и элемент И-НЕ, причем разрядные выходы формирователя опорных последовательностей через блок выбора опорной последовательности подключен к другому входу делителя частоты, входу формирователя сигнала переключения и к, входу блока управления, выходы которого подключены к другим входам блока выбора опорной последовательности, а выходы фазового дискриминатора яодключены к другим входам формирователя сигнала переключения, выходы которого подключены соответственно к входам блока исключения и входам элемента И-НЕ, другой вход которого соединен с выходом блока исключения, а выход элемента И-НЕ подключен к другому входу блока управления.

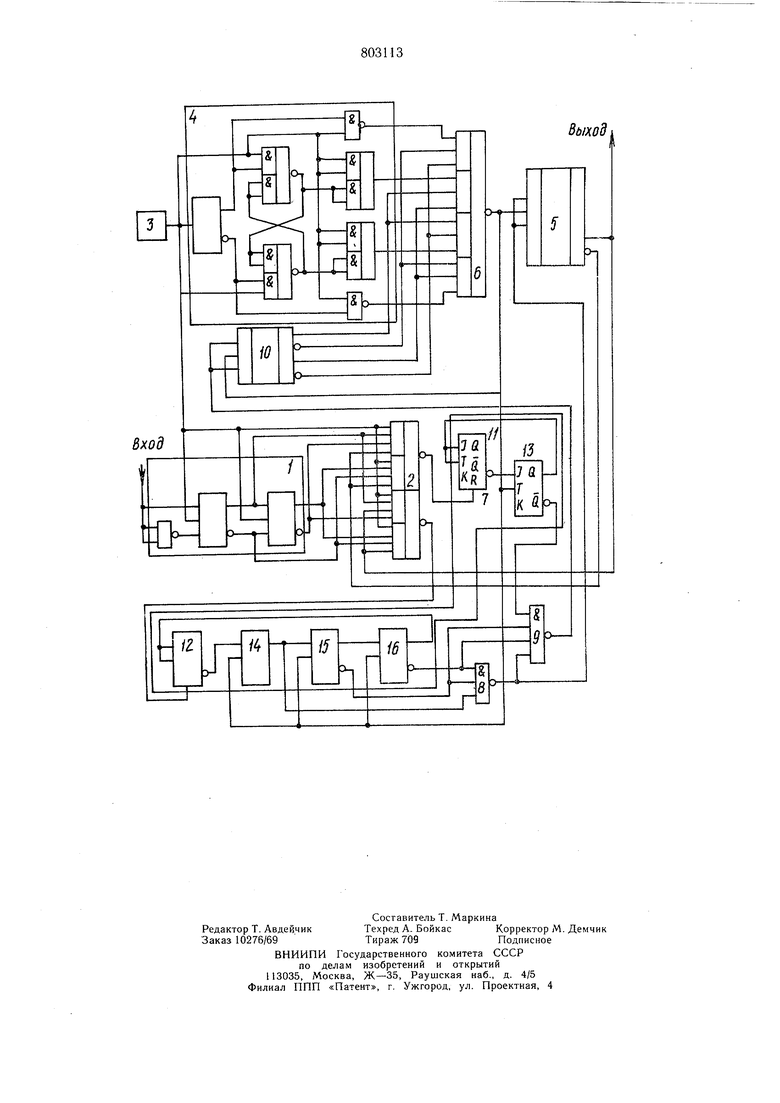

На чертеже дана структурная электрическая схема устройства.

Устройство содержит блок 1 выделения значащих моментов, фазовый дискриминатор 2, задающий генератор 3, формирователь 4 опорных последовательностей, делитель 5 частоты, блок 6 выбора опорной -последовательности, формирователь 7 сигнала переключения, блок 8 исключения, элемент И- НЕ 9 и блок 10 управления.

Работает устройство следующим образом.

отсутствии входного сигнала на выходе блока 1 потенциал равен 0.

Сигналы с выходов фазового дискриминатора 2 поступают соответственно на R-вход первого триггера 11 формирователя 7 при отставании фазы тактовых импульсов Т от фазы значащих моментов входного сигнала и на вход триггера 12 формирователя 7 при опережении фазы тактовых импульсов фазы значащих моментов входного сигнала, так как сигнал с выхода блока 1 равен «О, то фазовый дискриминатор 2 не мещает работе триггеров 11 - 16. Под воздействием импульсов блока 6 триггеры 11, 13 должны соответственно установиться в состоянии I и О, а триггеры 12-16 должны установиться соответственно в состоянии «1, «О, «О, «О. Таким образом, на выходе элемента И-НЕ 9 будет иметь место потенциал, «О, так как на его выходы поданы потенциалы «1.

На выходе блока 8 потенциал «1, т. е. блок 8 не мещает работе делителя 5.

Поскольку на выходе элемента И-НЕ сигнал «О, то блок 10 находится в каком-то одном из четырех состояний (например, в состоянии 01). Под воздействием импульсов с выхода блока 6 блок 10 не переключается, так как блок 10 - синхронный счетчик на четыре. В этом случае на выход блока 6 будет проходить последовательность с выхода формирователя 4 из которой путем деления получаются тактовые импульсы. В таком состоянии будет находиться устройство до прихода значащего момента входного сигнала.

После прихода фронта информации на выходе фазового дискриминатора 2 будет иметь место отрицательный импульс, длительность которого равна половине периода следования импульсов задающего генератора 3. Этим импульсом триггер 11 (спадом фронта этого импульса) устанавливается в состояние О, а триггер 13 под воздействием импульса с выхода блока 6 - в состоянии «1. Следующий тактовый импульс с выхода блока 6 своим спадом фронта переводит триггер 13 в состояние 0. Одновременно с ним в состояние «О переходит и триггер 11. На выходе элемента И-НЕ 9 появится потенциал, равный 1, длительность которого равна периоду последовательности с выхода блока 6. Этот потенциал попадает на вход блока 10. Под воздействием этого потенциала и импульса с выхода блока 6, блок 10 переходит в следующее состояние, а именно: из 01 в 11 (так как это синхронный счетчик), тем самым на выход блока 6 будет проходить последовательность с выхода формирователя 4.

Триггеры 12-16 в этом случае участвуют, т. к. имеет место отставание фазы тактовых импульсов от фазы значащих моментов входного сигнала. В этом случае нет необходимости иметь элементы, быстродействие которых больще fj, т. к. суммарная задержка при переключении последовательностей равна задержке при переключении синхронного счетчика блока 10, что равно для существующих элементов периоду следования импульсов задающей частоты fg. Следовательно, при отставании фазы тактовых импульсов от фазы значащих моментов входного сигнала делитель 5 будет нормально работать и при переходе с одной последовательности формирователя 4 на другую последовательность.

При опережении фазы значащих моментов входного сигнала импульс с выхода фазового дискриминатора 2 устанавливает триггер 12 в состояние «О, а триггер 13, 14 под воздействием импульса с выхода блока 6 устанавливается в состояние «1. На выходе блока 8 формируется потенциал «О, делитель 5 останавливается, на выходе элемента И-НЕ 9 формируется потенциал «1. Блок 10 под воздействием этого импульса и следующего импульса с выхода блока 6 переходит из состояния 01 в состояние 11, при этом на выходе блока 6 появится импульс последовательности с выхода формирователя 4 со сдвигом по фазе равным 3/2 - относительно предыдущего.° Кроме того, импульс с выхода блока 6 произведет запись «1 в триггер 15, а в триггер 14 - «О. Поэтому «О на выходе блока 8 будет отменен, и делитель 5 может переключаться под воздействием импульсов с выхода блока 6. Потенциал «1 на выходе элемента И-НЕ 9 сохранится. Под воздействием этого потенциала и первого импульса последовательности с выхода формирователя 4 блок 10 перейдет из состояния 11 в состояние 00. На выход блока 6 будет проходить последовательность с выхода формирователя 4 со сдвигом по фазе равным 3/2 f-. Одновременно под воздействием импульсов последовательности с формирователя 41запишется в триггер 16 и триггер 14, а триггер 15 перейдет в состояние «О. Потенциал «1 на выходе элемента И-НЕ 9 сохранится. Под воздействием этого потенциала и первого импульса последовательности блок 10 перейдет из состояния 00 в состояние 10. Одновременно с этим в триггеры 14 и 16 запищется а в триггер 12 - «1. В триггере 15 состояние «О уже записано на предыдущем щаге. Поскольку с выхода элемента И-НЕ 9 уже поступает потенциал «О, блок 10 больще переключаться не будет. Таким образом, из последовательности импульсов, поступающих с выхода формировйтеля 4, будет сформировано деление тактОвых импульсов. Фаза тактовых импульсов п(рд воздействием исключения и трех перек ючений сместится в сторону отставания н& величину 1/2 периода частоты f. В этом случае также нет необходимости иметь быстродействие элементов больще, чем fo, так как задержек при переключении столько же, сколько и в предыдущем случае. Задержки при исключении существенную роль не играют. Таким образом, в данном устройстве реализован щаг подстройки,. равный половине периода следования импульсов задающей частоты fo, причем быстродействие элементов устройства не превыщает эту заданную частоту fo. Предложенный способ синхронизации позволяет реализовать щаг коррекции фазы тактовых импульсов любой желаемой величины без увеличения задающей частоты. Формула изобретения 1. Способ синхронизации, заключающийся в формировании основной опорной последовательности импульсов, формировании m опорных последовательностей, сдвинутых одна относительно другой на величину г; формировании тактовых импульсов путем деления частоты одной из опорных последовательностей, определении направления и величины отклонения фазы тактовых импульсов, от фазы значащих моментов принимаемого сигнала и коррекции фазы тактовых импульсов, отличающийся тем, что, с целью повыщения точности синхронизации, перед коррекцией фазы тактовых импульсов, определяют момент времени начала и окончания процесса выбора последовательностей, участвующих в коррекции и выбирают число последовательностей и сдвиг по фазе между ними и запоминают последнюю последовательность из выбранных. 2. Устройство для осуществления способа, содержащее последовательно соединенные блок выделения значащих моментов и фазовь1Й дискриминатор и последовательно соединенные задающий генератор и формирователь опорных последовательностей, а также делитель частоты, выход которого подключен к другому входу фазового дискриминатора и блок исключения, выход которого подключен к входу делителя частоты, причем выход задающего генератора подключен к другому входу блока выделенкя значащих моментов и третьему входу фазового дискриминатора, отличающееся тем, что, введены блок выбора опорной последовательности, формирователь сигнала переключения и элемент И-НЕ, причем разрядные выходы формирователя опорных последовательностей через блок выбора опорной последовательности подключен к другому входу делителя частоты, входу формирователя сигнала переключения и к входу блока управления, выходы которого подключены к другим входам блока выбора опорной последовательности, а выходы фазового дискриминатора подключены к другим входам формирователя сигнала переключения, выходы которого подключены соответственно к входам блока исключения и входам элемента И-НЕ, другой вход которого соединен с выходом блока исключения, а выход элемента И-НЕ подключен к другому входу блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по завке № 2635156/09, кл. Н 04 L 7/08, 1978, (прототип). 2.Авторское свидетельство СССР 598260, кл. Н 04 L 7/00, 1976 (протоип).

Авторы

Даты

1981-02-07—Публикация

1979-01-05—Подача