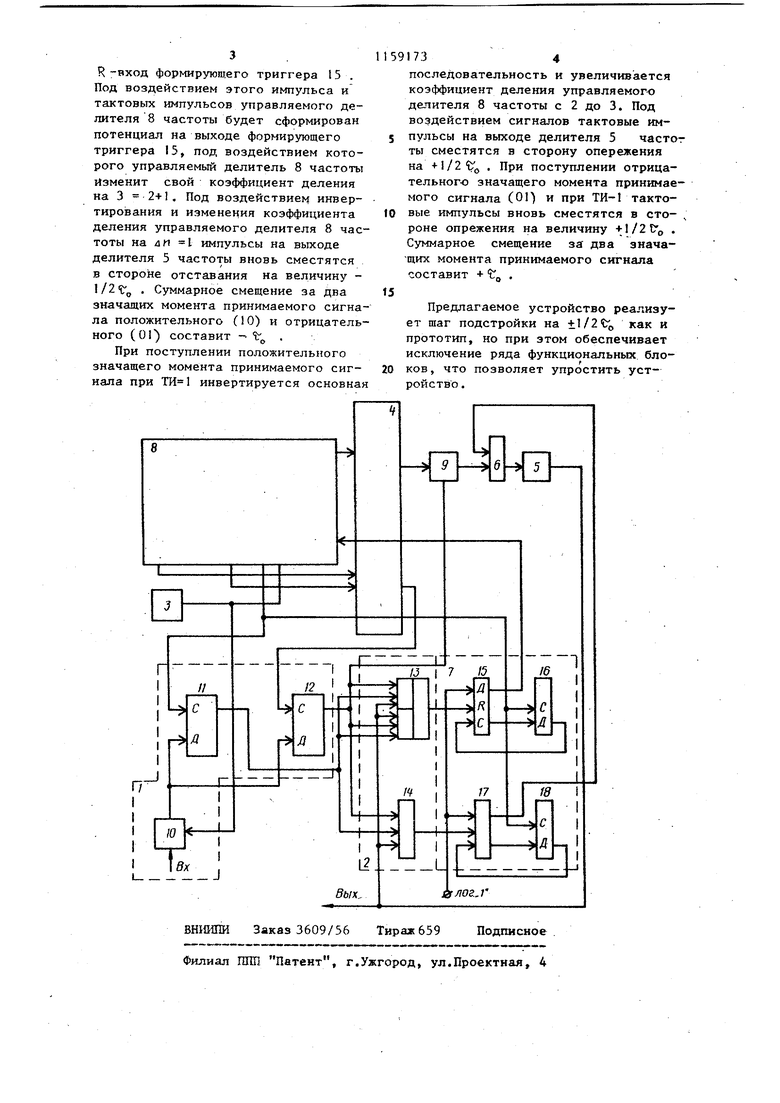

Изобретение относится к технике связи, а именно к синхронизации при емника с передатчиком и предназначе для дискретной автоподстройки фазы тактовых импульсов местного генера тора под фазу значащих моментов при нимаемого сигнала. Цель изобретения - упрощение уст ройства путем исключения ряда функциональных блоков. На чертеже представлена структур ная электрическая схема устройства синхронизации. Устройство синхронизации содержи блок 1 выделения значащих моментов, фазовый дискриминатор 2, опорный ге нератор 3, формирователь 4 импульсных последовательностей, делитель 5 частоты, блок 6 исключения,импульсЬ блок 7 управления, управляемый дели тель 8 частоты и сумматор 9 по моду лю два, причем блок 1 выделения зна чащих моментов 1 содержит блок 10 согласования,триггеры 1 1 и 12 задержки, фазовый дискриминатор 2 содержи элемент 2И-ШШ-НЕ 13 и ИЛИ-НЕ 14 (измерители отклонений), а блок 7 управления содержит формирующие триггеры 15-18. Устройство синхронизации работает следующим образом. При отсутствии входного сигнала на выходах триггеров 11 и 12 задержки блока I выделения значащих моментов потенциал равен О, так как триггеры 1I и 12 задержки включены в регистровом режиме, следовательно на вьпсодах элемента 2ИИЛИ-НЕ 13 и ИЛИ-НЕ 14 фазового дискриминатора 2 будут образованы узкие положительные импульсы как при ТИ О, так и при ТИ 1, где ТИ - выходной сигнал делителя 5 частоты, следовательно, формирующие триггеры 15-18 блока 7 управления будут находиться в исходном состоянии и не окажут воздействия на управляемый делитель 8 частоты и на блок 6 исключения импульсов. Таким образом, управляемый делитель 8 частоты разделит на и 2 частоту опорного генератора 3, кото рая пройдет без изменения формирователь 4, сумматор 9 и блок 6 исклю чения и будет разделена на в де лителе 5 частоты. Тем самым будут сформированы тактовые импульсы ТИ на его выходе. Следовательно, коэффициент ния устройства синхронизации при отсутствии принимаемого сигна.па будет равен к п 4. Пусть поступает принимаемая информация, совпадающая с (значащие моменты входного сигнала совпадают с ). В этом случае на выходе триггеров 11 и 12 задержки блока 1 выделения значащих моментов будут сформированы импульсы. В момент времени, совпадающий с фронтом сигнала триггера 11 блока I выделения значащих моментов принимаемого сигнала Сположительный значащий момент), начинается инвертирование основной последовательности импульсов, сформированной формирователем 4 импульсных последовательностей. Кроме того, на выходе элемента ИЛИ-НЕ 14 фазового дискриминатора 2 будет сформирован положительный импульс, поступающий на R-вход формирующего триггера 17. На R-вход формирующего триггера 15 положительный импульс поступать не будет, следовательно, при положительном значащем фронте и при формирующие триггеры 15 и 16 не мешают работе устройства синхронизации. При положительном значащем моменте принимаемого сигнала и при (соответственно фазовым дискриминатором 2 измерено отрицательное отклонение фазы ТИ от фазы значащего момента) совершается инвертирование основной последовательности, при этом на второй вход сумматора 9 подан потенциал равный 1 и исключение импульса основной последовательности под воздействием потенциала равного О на входе блока 6 импульсов. При воздействии этих сигналов будет иметь место сигнал на входе делителя 5 частоты, который среагирует на это таким образом, что фаза ТИ сдвинется в стороне отстаивания на величину - /2 , При поступлении отрицательного значащего момента принимаемого сигнала состояния триггеров 11 и 12 - 01 и при вновь будет происходить инвертирование основной последовательности, кроме того, в данной ситуации будет сформирован положительный импульс на выходе элемента 2И-ИЛИ-НЕ 13 фазового дискриминатора 2. Этот положительный импульс поступит на R-вход формирующего триггера 15 . Под воздействием этого импульса и тактовых импульсов управляемого делителя 8 частоты будет сформирован потенциал на выходе формирующего триггера 15, под воздействием которого управляемый делитель 8 частоты Изменит свой коэффициент деления на 3 2+1, Под воздействием инвертир01вания и изменения коэффициента деления управляемого делителя 8 час тоты на ли 1 импульсы на выходе делителя 5 частоты вновь сместятся в стороне отставания на величину . Суммарное смещение за два значащих момента принимаемого сигна ла положительного (10) и отрицатель ного (01) составит - t . При поступлении положительного значащего момента принимаемого сигнала при инвертируется основна 1734 последовательность и увеличивается коэффициент деления управляемого делителя 8 частоты с 2 до 3. Под воздействием сигналов тактовые импульсы на выходе делителя 5 часто: ты сместятся в сторону опережения на +1/2 . При поступлении отрицательного значащего момента принимаемого сигнала (ОП и при ТИ- тактовые импульсы вновь сместятся в стороне опрежения на величину +l/2t . Суммарное смещение за два значащих момента принимаемого сигнала составит + Предлагаемое устройство реализует шаг подстройки на tl/ZtTo как и прототип, но при этом обеспечивает исключение ряда функциональных блоков, что позволяет упростить устройство.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ синхронизации и устройстводля ЕгО ОСущЕСТВлЕНия | 1979 |

|

SU803113A1 |

| Устройство синхронизации | 1981 |

|

SU1125759A1 |

| Устройство дискретной автоподстройки фазы тактовых импульсов | 1983 |

|

SU1141581A1 |

| Устройство автоподстройки фазы тактовых импульсов | 1986 |

|

SU1527718A1 |

| Устройство синхронизации | 1979 |

|

SU873440A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство синхронизации импульсных приемников | 1976 |

|

SU605327A1 |

| УСТРОЙСТВО КОНТРОЛЯ СИНХРОНИЗМА КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1993 |

|

RU2057395C1 |

| Устройство для автоподстройки фазы тактовых импульсов | 1990 |

|

SU1811017A1 |

УСТРОЙСТВО СИНХРОНИЗАЦИИ, содержащее последовательно соединенные блок вьщеления значащих моментов, фазовый дискриминатор, блок управления, блок исключения импульсов и делитель частоты, выход которого подключен к второму входу фазового дис- криминатора, а также опорный генератору выход которого подключен к управляющим входам формирователя импульсных последовательностей и блока вьщеления значащих моментов, отличающееся тем, что, с целью упрощения устройства путем исключения ряда функциональных блоков, введены сумматор по модулю два и управляемый делитель частоты, при этом первый выход формирователя импульсных последовательностей через сумматор по модулю два подключен к . другому входу блока исключения импульсов, а выход опорного генератора че рез управляемьЕй делитель частоты подключен к дополнительным входам формирователей импульсных последовательностей, один из которых объединен с дополнительными управляющими входами блока выделения значащих моментов и блока управления, причем к другому входу блока выделения значащих моментов подключен другой выход (Л формирователя импульсных последовательс ностей, причем Дополнительный выход блока вьзделения значащих моментов соединен с другим входом сумматора по модулю два, а дополнительный выход блока управления - с дополнителыйм входом управляемого делителя частоты.

| Электростатический двигатель | 1978 |

|

SU694962A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ синхронизации и устройстводля ЕгО ОСущЕСТВлЕНия | 1979 |

|

SU803113A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-05-30—Публикация

1981-04-08—Подача