;54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное трехканальное устройство приоритета | 1982 |

|

SU1091369A1 |

| Устройство приоритета | 1982 |

|

SU1128254A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Многоканальное устройство для контроля резервированного регистра сдвига | 1980 |

|

SU936037A1 |

| Устройство для прерывания резервированной вычислительной системы | 1991 |

|

SU1824636A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для управления очередностью обслуживания | 1987 |

|

SU1481765A2 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Устройство контроля и управления реконфигурацией | 1984 |

|

SU1213554A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в системах обработки данных для управления доступом к коллективно используемому ресурсу.

Известно многоканальное устройство приоритета, содержащее блок управления, элемент ИЛИ, а в каждом канапе - триггер, три элемента И, три элемента ИЛИ, два элемента НЕ 13...

Однако устройство требует для своей реализации элементы ИЛИ с различным числом входов, причем с увеличением числа каналов возрастает количество входов у элементов ИЛИ.

Наиболее близким к изобретению по технической сущности и достигаемому результату является многоканальное устройство приоритета, содержащее узел управления, выполненный в виде триггера, четырех элементов И и двух элементов НЕ, а каждый канал ус- ройства выполнен в виде триггера шести элементов И и четырех элементов НЕ 2.

Недостаток устройства состоит в том, что одна или более заявок, поступающих с частотой, равной частоте работы устройства, может обрабатываться непрерывно в то время, как

заявки с более низкими частотами поступления в это время не обрабатываются. Кроме того, использование этого устройства в троированных структуpax не представляется возможным из-за того, что наличие одного отказа в устройстве приводит к отказу всего канала системы. Таким образом, устройство имеет малое быстродействие и низ-кую надежность.

Цель изобретения - повышение быстродействия и надежности.

Поставленная цель достигается тем, что в многоканальное устройство приоритета, содержащее блок управления, выполненный в виде четырех элементов И и первого триггера, первый вход которого соединен с выходом первого элемента И блока управления, а второй вход - с выходом второго элемента И блока управления, а каждый канал выполнен в виде первого триггера и трех элементов И, третий и последующие каналы содержат дополнительно

5 элемент И и два элемента НЕ, второй канал содержит второй дополнительный элемент И, причем первый вход первого триггера канала соединен с соответствующим запросным входом устройства, второй вход первого триггера

анала .соединен с выходом первого лемента И канала, первый выход пер-ого триггера второго канала соединен первым входом пятого элемента И того канала, в блок управления ввеены мажоритарный элемент, второй третий триггеры, а в каждый канал ведены мажоритарный элемент, второй и третий триггеры, в первый канал введен один элемент ИЛИ, а во второй и последующие каналы - два элемента ИЛИ, причем выход мажоритарного элемента блока управления соединен с первыми входами второго и третьего эле;:ементов И первого канала, вторые входы KOTOptJX соединены соответственно со вторым и первым выходами первого триггера первого канала, выход третьего элемента И блока управления соединен с третьими вxoдa 1и вторых элементов И каналов, выход мажоритарного i;vTeMeHTa канала соединен с первым входом первого элемента И канала, выход третьего элемента И канала соединен в первом канале - с первым входом элемента ИЛИ/ во втором и последующем каналах - с первым входом первого элемента ИЛИ, выход мажоритарного элемента канала соединен в первом канале .- со вторым входом элемента ИЛИ, во втором и последующих каналах - со. вторым входом первого элемента ИЛИ, выход элемента ИЛИ первого канала соединен с перв ми входами второго и третьего элементов И второго канала,выход первого элемента ИЛИ канала соединен с первыми входами второго и третьего элементов И последующего канала, первый выход первого триггера первого канала соединен с первыми входами второго элемента ИЛИ и четвертого э.пемента И второго канала и со вторым входом пятого элемента И второго канала, выход пятого элемента И второго канала соединен с первыми входами второго элемента ИЛИ последующих каналов и четвертого элемента И последующих каналов, вторые входы первых элементов И каналов соединены с первым тактовым вводом устройства, выход второго элемента И канала соединен с первым входом второго триггера канала, первый выход второго триггера канала соединен с. первым входом третьего триггера канала, выход третьего триггера канала соединен с первьлм входом мажоритарного элемента канала и с соответствугощим выходом первой группы разрешающих выходов устройства, вторые и третьи входы мажоритарного элемента канала соединены с соответствующими входами первой и второй групп информационных всодов. устройства, выход мажоритарного элемента канала соединен с соответствующим выходом второй группы раэрешающих выходов устройства, вторые входы вторых триггеров каналов соединены с выходом второго элемента И блока управления, первый, выход третьего триггера блока управления соединен с первым входом третьего элеме.нта И блока управления, со счетным входом второго триггера блока управления, со счетными входами третих триггеров каналов, и с первым управляющим выходом устройства, второй выход первого триггера канагла (кроме первого канала) соединен со вторым входом четвертого элемента И канала выход четвертого элемента И канала, через первый элемент НЕ канала соединен со вторым входом второго элемента И канала, первый выход первого триггера канала (кроме первого канала) через второй элемент НЕ канала соединен со вторым входом второго элемента ИЛИ канала, выход второго элемента ИЛИ канала соединен со вторым входом третьего элемента И канала, выход первого элемента ИЛИ последнего канала соединен с первым входом первого элемента И блока управления, .выход третьего элемента И блока управления соединен со вторым входом первого элемента И. блока управления, второй тактовый вход устройства соединен с первым входом второго элемента И блока управления и со вторым входом третьего элемента И блока управления, второй выход третьего триггера блока управления соединен со вторым входом второго элемента И блока управления, выход первого триггера блока управления и первый управляющий вход устройства соединены с пэрвым входом второго трк-ггера блока управления, выход, второго триггера блока управления соединен со вторым управляющим выходом устройства и с первым входом мажоритарного элемента блока управления, второй и третийвходы мажоритарного элемента блока управления соединены соответственно с первым и вторым разрешающими входами устройства, ё. третий и четвертый управляющие входы устройства через четвертый элемент И блока управления соединены со счетным входом третьего триггера блока управления.

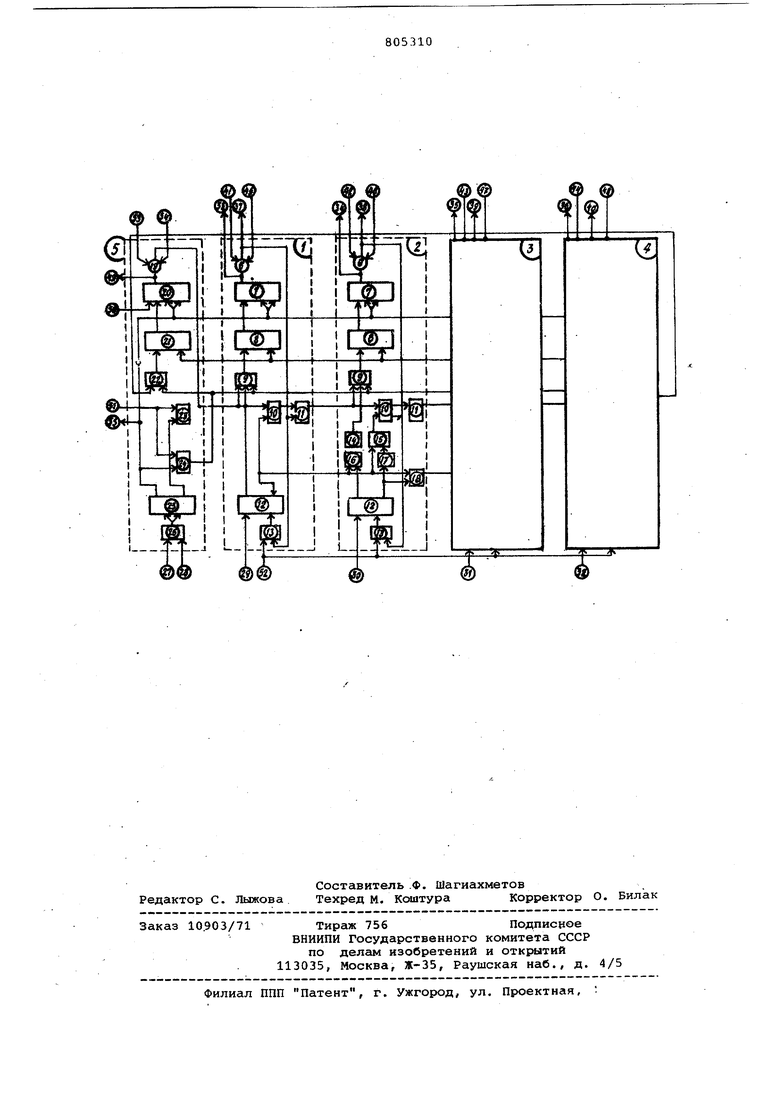

На чертеже представлена структурная схема устройства.

Мно1 оканальное устройство приоритета содержит каналы 1-4, блок 5 управления, каждый канал содержит мажоритарный элемент 6, третий триггер 7, второй триггер 8, второй элемент И 9, третий элемент И 10, пер-вый-элемент ИЛИ 11, второй и последующие каналы содержат первый .триггер 12, первый элемент И 13, первый элемент НЕ 14,. в.торой элемент ИЛИ 15 четвертый элемент И 16, второй элемент НЕ 17, только второй канал содержит пятый элемент И 18, блок 5 управления содержит мажоритарный элемент 19,-второй триггер 20, пер

вый триггер 21, первый элемелт И 22 второй элемент И 23, третий элемент И 24, третий триггер 25, четвертый элемент И 26, третий 27 и четвертый 28 управляющие входы, запросныевходы 29-32, выходы 33-36, образующие первую группу разрешающих выходов устройства, выходы 37-40, обраэукяцие вторую группу разрешающих выходов устройства, входы 41-44, образующие первую группу информационных входов устройства, входы 45-48, образукндие вторую группу информационных входов устройства, второй управляющий выход 49, первый управляющий вход 50, первый тактовый вход 51, второй тактовый вход 52, первый 53 и второй 54 разЕ ешаквдие входы, первый управляющий выход 55.

Триггеры 7 каналов 1-4 образуют вспомогательный регистр устройства, триггеры 8 каналов 1-4 образуют буферный регистр устройства, триггеры 12 каналов 1-4 образуют регистр индикации заявок устройства, элементы И 10, ИЛИ 11 образуют цепь переноса.

Устройство работает следующим образом.

В исходном состоянии все триггеры устройства находятся в нулевом состоянии. .При подаче импульсов запуска на вход 50устройства, при наличии разрешающего потенциала на входе 28 и при подаче тактовых сигналов на входы 52, 51, 27 триггер.20 блока 5 управления устанавливается в единичное состояние, а затем устанавливается в единичное состояние триггер 21 блока 5 управления, после чего потверждается состояние триггера 20 блока 5 управления и триггер 21 блок управления 5 устанавливается в нулевое состояние и т.д. Этот режим является режиг« Ом ожидания и по цепи сквозного переноса (т.е. через элементы И 10., ИЛИ 11 каналов 1-4) циркулирует сигнал переноса от выхода элемента 19 до входа элемента И 22 блока5 управления.

При поступлении на входы 29-32 синалов заявок устанавливаются в единичное состояние соответствующие триггера 12 регистра индикации заявок и сигнал сквозного переноса через Один из элементов И 9 каналов 1-4 устанавливает в единичное состояние Эриггер 8 соответствующего канала 2, единичное состояние которого является разрешением установки в 1 соответствующего триггера 7 каналов 1-4.

обеспечения приоритетной обработки заявок по входам 29 и 30, частота поступления которых может быть невысокой, но реакция на них должна быть малой, предусмотрен приоритетны элемент И 18, выходной сигнал которого блокирует установку в единичное

состояние соответствующих триггеров, начиная с канала 3 устройства, н организует передачу сигнала сквозного переноса на вход элемента И 22 блока 5 управления для установки триггера 21 блока 5 управления в единичное состояние. Время обработки заявок по каждому входу при условии отсутствия заявок по остальным входам в устройстве равно 2TQ, где TQ - цикл работы устройства, и не зависит

o от числа каналов устройства.

Принцип работы устройства, заключающийся в том, что после обработки некоторой заявки устройство переходит в режим анализа наличия заявки

5 в следующем канале., что обеспечивается наличием цепи сквозного переноса и соответствующего соединения ее входов и выходов с выходами и входами триггеров регистра индикации

0 заявок и вспомогательного регистра, позволяет обрабатывать заяржи болееравномерно по -мере их поступления, что приводит к увеличению быстродействия устройства.

Наличие мажоритарных элементов 6

5 в канале 1-4 позволяет использовать устройство в троированных резервированных структурах за счет того, что выходы мажоритарных элементов соединены с цепями сброса триг0геров индикации соответствующих заявок, а выходные сигналы этих м 1жоритарНых сигналов позволяют сформировать сигнальа сквозного переноса только при. наличии этих сигналов более,

5 чем в двух каналах устройства.

Таким образом, введением мажоритарных элементов, кромеобеспечения надежных выходных сигналов устройства, организуется его надежная внутренняя

0 синхронизация.

Формула изобретения

Многоканальное устройство Приоритета, . содержащее блок управления, выполненный- в виде четырех элементов И и первого триггера, первый вход которого соединен с выходом первого элемента И блока управления, а второй вход - с выходом второго элемента И блока управления, а каждый канал выполнен в виде первого триггера и трех элементов И, третий и последующие кайалы содержат дополнительно элемент И и два элемента НЕ, второй канал содержит второй дополнительный элемент И, причем первый вход первого триггера канала соединен с соответствунвдим запросным входом устройства, второй вход первого триггера канала соединён с выходом первого элемента И канала, первый выход первого триггера второго канала соединен с.первым входом пятого элемента И этого канала, отличающееся тем, что, с целью повышения быстродействия и надежности, блок управления содержит мажоритарный элемент, второй и третий триггеры, а каждый канал содержитмажоритарный элемент, второй и третий триггеры, первый канал содержит элемент ИЛИ, второй и последующие каналы содержат два элемента ИЛИ, причем.выход мажоритарного элемента блока управления соединен с первыми входами второго и трет его элементов И первого канала, вторые входы которых соединены соответственно со вторым и первым выходами первого триггера первого канала, выход третьего элемен та И блока управления соединенС третьими входами вторых элементов И каналов, выход Мажоритарного элемента канала соедине с первым входом первого элемента И канала, выход третьего элемента И канала соединен в первом канале - с nepBfcivi входом элемента ИЛИ, во втором и последующих каналах - с первым входом первого элемента ИЛИ, выход мажоритарного элемента канала соединен в первом канале - со вторым входом элемента ИЛИ, во втором и последующих каналах - со вторым входом первого элемента ИЛИ, выход элемента ИЛИ первого канала соединен с первым входами второго и третьего элементов И второго канала, выход первого элемента ИЛИ канала соединен с первыми входами второго и третьего элементов И последующего канала, первый выход первого триггера первого канала соединен с первыми входами второго элемента ИЛИ и четвертого элемента И второго канала и со вторым входом пятого элемента И второго канала выход пятого элемента И второго канала соединен с первыми входами второго элемента ИЛИ последующих канало и четвертого элемента И последукядих каналов, вторые входы первых элементов И каналов соединены с первым так товым входом устройства, выход второго элемента И канала соединен с первым входом второго триггера канала, первый выход второго Tpjfrrepa ка нала соединён с первым входом третьего триггера канала, выход третьего триггера канала соединен с первым входом мажоритарного элемента канала и с соответствующим выходом первой группы разрешающих выходов устройства, вторые и третьи входы мажоритарного элемента канала соединены с соответствующими входами первой и второй групп информационных входов устройства, выход мажоритарного элемента канала соединен с соответствующим выходом второй группы рг1арешающих выходов устройства, вторые -входы вторых триггеров каналов соединены с выходом второго элемента И блока управления, первый выход третьего триггера блока управления соединен с первым входом третьего элемента И блока управления, со счетньоь входом второго триггера блока управления, со счетными входами третьих триггеров каналов, с первым управляющим выходом устройства, второй выход первйго триггера канала (кроме первого канала) соединен со вторым входом четвертого элемента И канала, выход четвертого элемент И канала через первый элемент НЕ канала соединен со вторым выходом второго элемента И канала, первый выход первого триггера канала (кроме первого канала) через второй элемент НЕ канала соединен со вторым входом второго элемента ИЛИ канала, выход второго элемента ИЛИ канала соединен со вторым входом третьего элемента И канала, выход первого элемента ИЛИ последнего канала соединен с первым входом первого элемента И блока управления, выход третьего элемента И блока управления соединен со вторым входом первого элемента И блока управления, второй тактовый вход устройства.соединен с первым входом второго элемента И блока управления и со вторым входом третьего элемента И блока управления, второй .выход третьего триггера блока управления соединен со вторым входом второго элемента И блока управления, выход первого триггера блока управления и первый управляющий вход устройства соединены с первым входом второго триггера блока управления, выход второго триггера блока управления соединен со вторым управляющим выходом устройства и с первым входом мажоритарного элемента блока управления, второй и третий входы мажоритарного элемента блока управления соединены соответственно с первым и вторым разрешающими входами устройства, а третийи четвертый управляющие входы устройства через четвертый элемент И блока управления соединены со рчетным входом третьего триггера блока управления. Источники информации, принятые во внимаание при экспертизе 1.Авторское свидетельство СССР 209049, кл. G 06 F 9/18, 1972. 2.Авторское свидетельство СССР № 474807, кл. G 06 F 9/18, 1975 (прототип).

Авторы

Даты

1981-02-15—Публикация

1978-06-19—Подача