Изобретение относится к вычислительной технике и может быть исполь зовано для распределения задач по вычислителям-. Известно устройство для обслуживания запросов, содержащее регистры схемы записи, схему сравнения и схе му выборки l 1. Недостаток устройства состоит в том, что оно обладает ограниченными функциональными возможностями, так как перестройка порядка обслуживани может быть осуществлена только по одному параметру - номеру запроса. Наиболее близким по технической сущности к предлагаемому является устройство для обслуживания запросов , содержащее блок памяти с регис ром числа, соединенный с блоком настройки, регистр ресусрса, выход которого соединен с первым входом у ла сравнения, второй вход которогд соединен с первым выходом регистра числа блока памяти, блок местного у равления, соединенный с блоками па- мяти и настройки 2. Однако прямое использование тако го устройства в разрабатываемой циф ровой интегрирующей структуре является нерациональным, так как оно распределяет основную память между задачами, исходя лишь из наличия оставшегося ресурса, а именно, назначает на решение очередную задачу из некоторой их последовательности, если эта задача обеспечена ресурсами. Ни время решения, ни соотношения 1рангов задач, которые в каждый данный момент могут быть назначены на решение, не учитываются. (Здесь и ниже под ранге задачи понимается потребное для решения количество ресурсов, Например интеграторов, ячеек памяти и ПР). Таким образом, недостаток устройства - ограниченные функциональные возможности. Цель изобретения - расширение функциональных возможностей за счет увеличения числа учитываемых параметров запросов. Поставленная цепь достигается тем, что в устройство для обслуживания запросов, содержсццее блок памяти, выход которого соединен с регистром числа, блок настройки, первый и второй входы - выходы которого соединены соответственно со входом выходсял блока памяти и с первым входом - выходом блока управления, регистр ресурса,, выход которого и первый выход регистра числа соединены со входами схемы сравнения, приче первый разрешающий выход блока управления соединен со входом блока памяти, введены сумматор- вычитатель, регистры ранга и номера, два блока выбора наибольшего числа и два узла обнаружения нулевого кода, причем первый выход регистра числа соединен с первым входом первого блока выбора наибольшего числа, первый и iiToрой входы-выходы, второй вход и выход которого соединены соответственно со вторым входом-выходом .блока управления, со входом-выхо юм второго блока выбора наибольшего числа, с выходом схемы сравнения и со входом регистра ранга, первый-четвертый входы и выход сумматора-вычитателя соединены соответственно с выходом регистра ресурса,. с выходом блока настройки, с выходом регистра ранга, со вторым разрешакяцим выходом блока управления и со входом регистра реcypca,v второй и третий выходы регистра числа соединены соответственно со входом второго блока выбора наибольшего числа и с информационным входом регистра номера, управляющий вход и выход которого соединены соответственно с третьим раэрешэю:дим выходом блока управления и со входом блока настройки, выход регистра ранга череэ первый узел обнаружения нулевого, кода, а третий выход регистра числа .- череэ второй узел обнаружения нулевого кода соединены соответственно с первым и вторым запускакздими входами блока управления.

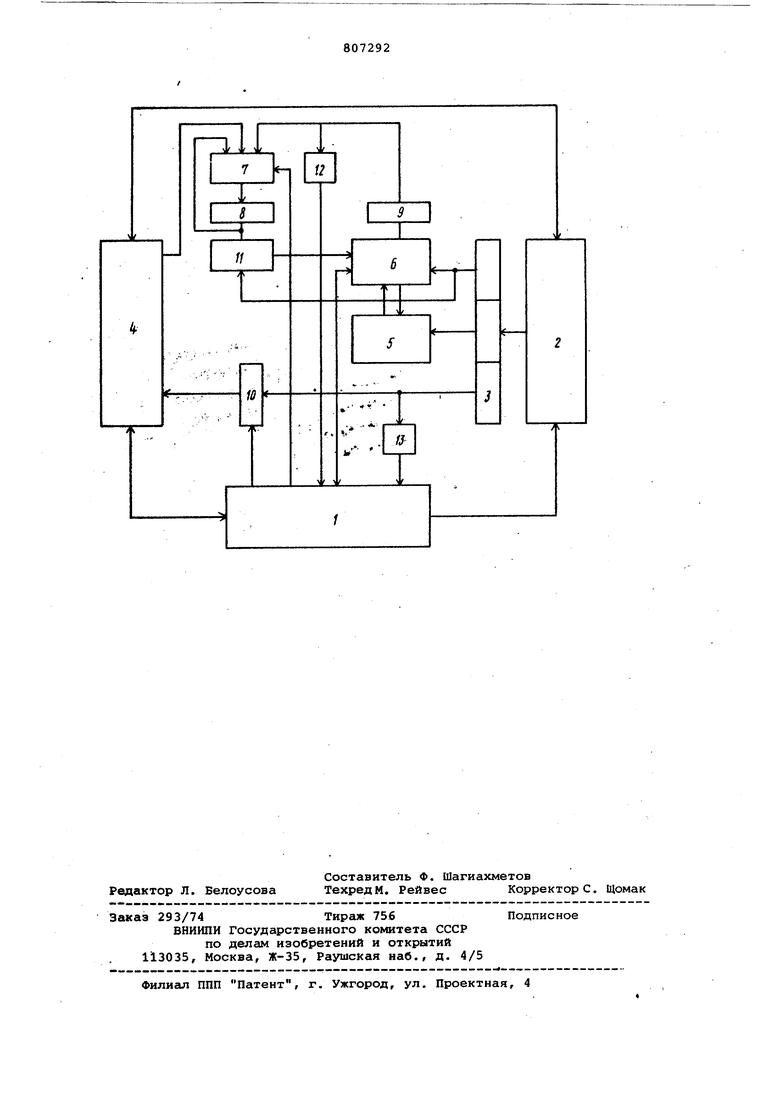

Структурная схема устройства представлена на чертеже.

Устройство для обслуживания запросов содержит блок 1 управления, блок 2 памяти, регистр 3 ч-исла, блок 4 настройки, блоки 5 и б выбора наибольшего числа, сумматор-вычитатель 7, регистр 8 ресурса, регистр 9 ранга , регистр 10 номера, схему 11 сравнения, и узлы 12 и 13 обнаружения нулевого кода.

Устройство работает следующим образом.

В блок 2 памяти заносится пакет , которые необходимо решить на однородной вычислительной системе, в Частности на цифровой интегрирующей структуре. Каждая задача харакгтеризуется рангом, т.е. числом цеобходимых для решения процессоров (микропроцессоров, интеграторов) и временем решения. Предлагаемое устройство должно распределить задачи по процессорам, чтобы пакет задач был решен за минимально возможное время.

Суть работы устройства заключается в том, что осуществляется поиск задач максимального ранга, не превышающего количество свободных ресурсов, а из выбранных задач выбирается с наибольшим временем решения. Эта задача и назначается для решения.

Для этого блок 1 поочередно выбирает из блока 2 в регистр 3 ячейки с параметрами каждой задачи, т.е. со значениями ран.га, времени решения и порядкового номера. Далее происходит три сравнения - ранг задачи в схеме 11 сравнения сравнивается со значением ресурса (числом свободных продессоров,- ячеек памяти и т.п.), хранимого в регистре 8, ранг задачи в блоке б сравнивается с максима.пьнь)М рангом из рангов раыее опрошенных задач, обеспеченных ресурсом врег-ет -задачи в блоке 5 сравнивается мак-.: имальны временем из времен ранее опрошенных задач. Если ранг задачи больше значения ресурса (т.е. процессоры заняты под другие задачи) то результаты двух других сравнений не учитываются, а задача игнорируется. ЕСЛИ ранг Зсщачи равен или меньше значения ресурса, то схема 11 сравнения вьщает разрешение блоку б произвести учет своего результата сравнения. Здесь могут быть три случая, анализ которьр производит блок 1 т ранг задачи меньше, больше и равен максимальному рангу предыдущих задач. В первом случае ЗсЩача иг5горг р -ется. Во втором случав параметры задачи запоминаются в блоках 5 и 6 и э регистре 10. В третьем случае блок б учитывает результат сравнения в блоке 5 и запоминаются параметры задачи с большим временем решения.

Таким o6pa3c s, после опроса всех задач в блоке б будет храниться значение максимального ранга из рангоэ задач, обеспеченных ресурсами, а в .регистре 10 хранится номер соответствующей задачи. Ранг заносится в регистр 9, а номер задачи из регистра 10 отсылается в блок 4 настройки, который, обращаясь по этому номеру к блоку 2, извлекает из него всю настроечную информацию данной задачи и производит настройку процессоров и системы коммутации вычислительной системы. Затем с помощью сумматора-вычитателя 7 из значения регистра 8 вычитается значение регистра 9.

Далее цикл опроса параметров задач начинается сначала, в результате чего аыбирается новая задача. Так будет продолжаться до тех пор, пока достаточно ресурсов.

Если ресурс меньше, чем минимальный ранг задач, то в регистре 9 будут записаны нули, что отметит узел 12, и блок 1 остановит работу устройства. Работа устройства возобновляется при поступлении из блока 4 сигнала об освобождении некоторого количества ресурсов (т.е. о решении хотя бы одной из задач). При этом с помощью сумматора-вычитатедя 7 к значению ресусрса в регистре 8 присуммируется число освободившихся ре сурсов. Работа устройства будет продолжаться до тех пор, пока узел 13 не сообщит в блок 1, что задач в блоке 2 нет. Работа такого узла заключает ся в фиксации хотя бы одного отличного от нуля номера задачи. Если вс номера задач, извлекаемых при опросе блока 2 нулевые, то это свидетельст вует о том, что задач больше нет. Блок 1 исключает очередную назначен ную для решения задачу из блока 2. Таким образом, изобретение имеет более широкие функциональные возмож ности, так как при обслуживании зап сов, каковыми являются параметры за дач, позволяет учесть соотношение, рангов и времен решения задач. Наиболее наглядно эффективность устройства проявляется при использо вании его в системе, когда ресурсами являются отдельные ЭВМ. В этом случае изобретение позволяет производить такое распределение задач по площадям (ранг х время решения), что время простоя отдельных ЭВМ стр мится к нулю. Формула изобретения Устройство для обслуживания запросов, содержащее блок памяти, выход которого соединен с регистром числа, блок настройки, первый и вто рой входы - выходы которого соеди,иены соответственно со входом-выхо|дом блока памяти и с первым входомвыходом блока управления, регистр ресурса, выход которого и первый выход регистра числа соединены со входами схемы сравнения, причем пер вый разрешающий выход блока управЛенин соединен со входом блока памяти , о тличающееся тем, что, с целью расширения функциональных возможностей за счет увеличения числа учитываемых параметров запросов, оно содержит сумматор-вычитатель, регистры ранга и номера, два блока выбора наибольшего числа и два узла обнаружения нулевого кода, причем первый выход регистра числа соединен с первым входом первого блока выбора наибольшего числа, первый и второй входы-выходы, второй вход и выход которого соединены соответственно со вторым входом-выходом блока управления, со входомвыходом второго блока выбора наибольшего числа, с выходом схемы сравне-т ния и со входом регистра ранга, первый - четвертый входы и выход сумматора-вычитателя соединены соответственно с выходом регистра ресурса, с выходом блока настройки, с выходом регистра ранга, со вторым разрешающим выходом блока управления и со входом регистра ресурса, второй и третий выходы регистра числа соединены соответственно со входом второго блока выбора наибольшего числа и с информационным входом регистра номера, управляющий вход и выход которого соединены соответственно с гЕретьим разрешающим выходом блока управления и со входом блока настройки, выход регистра ранга через первый узел обнаружения нулевого кода, а третий выход регистра числа - через второй узел обнаружения нулевого кода соединены соответственно с первым и вторым запу скающими входами блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 467346, КЛ. 6 06 F 9/18, 1975. 2.Патент Японии 51-37740, КЛ. G 06 F 9/18, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления прерыванием программ | 1983 |

|

SU1096647A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Устройство для сжатия информации | 1985 |

|

SU1392584A1 |

| Ранговый обнаружитель сигналов | 1981 |

|

SU970291A1 |

| СПОСОБ ОБНАРУЖЕНИЯ СИГНАЛОВ С ПОСТОЯННЫМ УРОВНЕМ ЛОЖНЫХ ТРЕВОГ (ВАРИАНТЫ) | 2008 |

|

RU2392637C1 |

| УСТРОЙСТВО ДЛЯ РАНГОВОЙ ФИЛЬТРАЦИИ | 1990 |

|

RU2015551C1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для сжатия данных | 1987 |

|

SU1522268A1 |

Авторы

Даты

1981-02-23—Публикация

1978-05-03—Подача