буферной памяти, блок 2 программной диспетчеризацрШ5блок 3 nporpa viHoro управления, блоки 4-7 обработки дан- 1-яых„ Наличие модифицированной стра- 1ШЧНОЙ адресации позволяет записать многократно используемые данные в блоки буферной памяти различных блоков обработки таким образом что за время выполнения одной команды яа указанной процедуре одновременно по

Изобретение относится / к вычислительной технике и может бь1ть использовано для обработки сигналов с йы- сокой производительностью, в частности, в геофизике S особенно дл1я выпол- нения таких времяемких процедур как конволюция, различного рода фильтраций, на которых возможно распараллеливание вычислений на нескольких ус- ройствах обработки данных,

Цель изобретения - упрощение раллельного процессора,

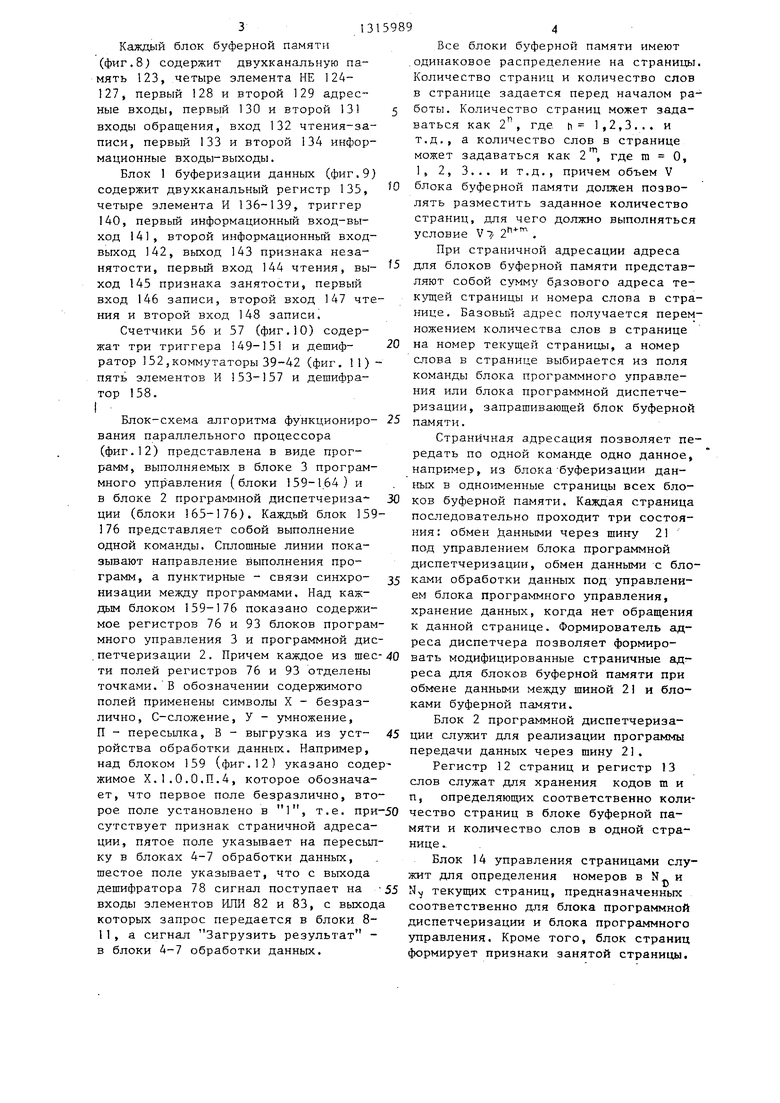

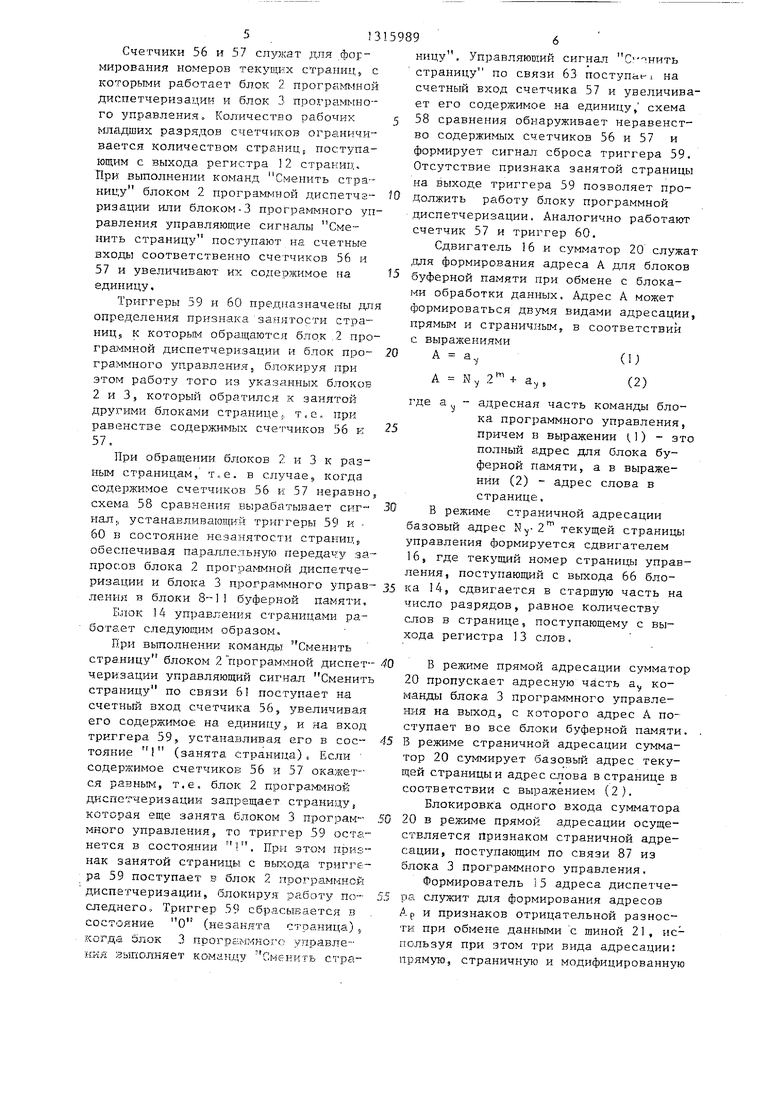

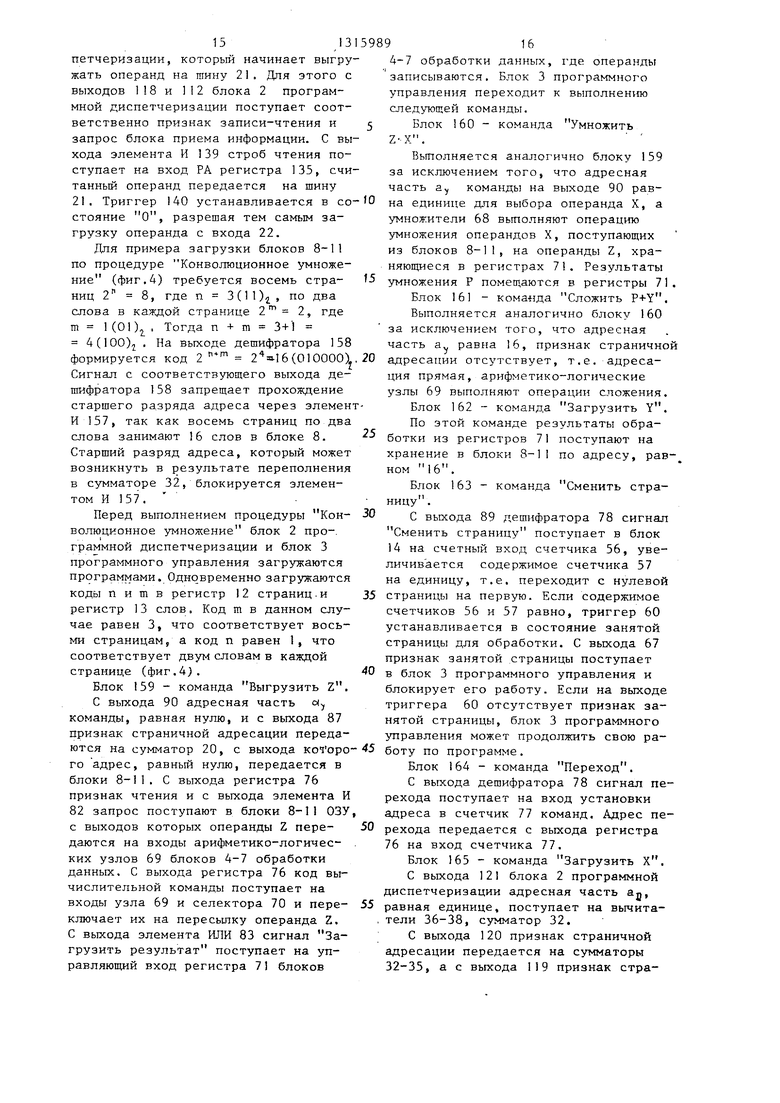

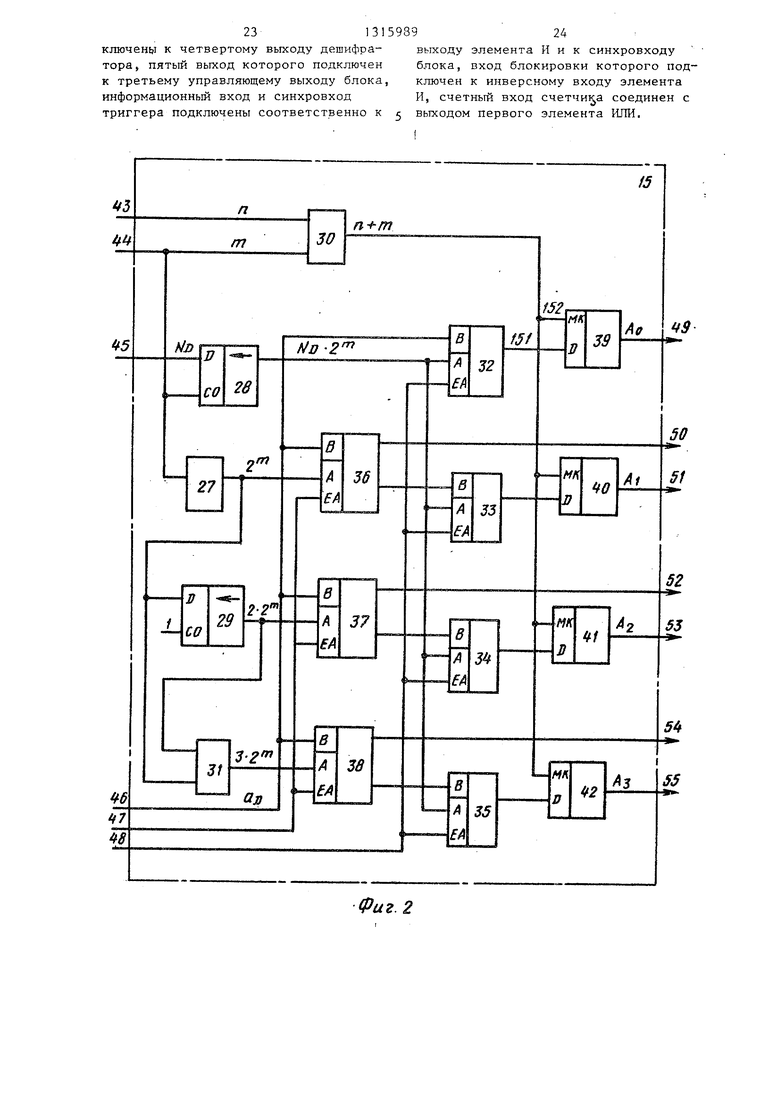

На фиг,1 предстанлена схема парал ле;льного процессора;, на - схема формирователя адреса диспетчера; на фи1 ,3 - схема блока з правления страницами;, на фиг.4 - схема загруз-ки буферных ОЗУ на процедуре Конво- люционное умножение ; на, фиг, 5 - схема устройства, обработки данных; на фиг,6 - схема блока программного управления; на фиг„7 - схема блока прю- грамг-шой диспетчеризации; на фиг.8 - схема буферной памяти; на йтг,9 схема блока буферизаггии данных; на фиг. 10 схема счетчика; на фиг. 11 - схема KOMt-iyTaTopai, на. фи:(.12 - схема алгоритма функционирования парап:- лельиого процессора.

Параллельный процессор содержит блок 1 буферизации данных, блок 2 программной диспетчеризащЕИ, блок 3 программного управления, четыре блок 4-7 обработки данкькс, четыре блока 8-1 буферной памяти,, регистр 2 страниц, регистр 3 слов, блок 14 управления страницамиS формирователь 15 адреса диспетчера,, сдвигатель 16з три элемента И 17-19, суьз- атор 20, вторую шину 21 данных, первугс шину

лучаются четыре промежуточных результата и исключается необходимость обмена данньми непосредственно между устройствами обработки данных. Кроме того, аппаратная реализация страничной адресации и наличие блоков буферной памяти позволяют параллельно с обменом выполнять обработку данных и упростить програм1 1ирование. 2 3 . п. ф-льг, ) 2 ил.

22 данньк,, вход 23 загрузки программ диспетчеризации, вход 24 загрузки програьш управления, первый 25 и второй 26 настроечные входы.

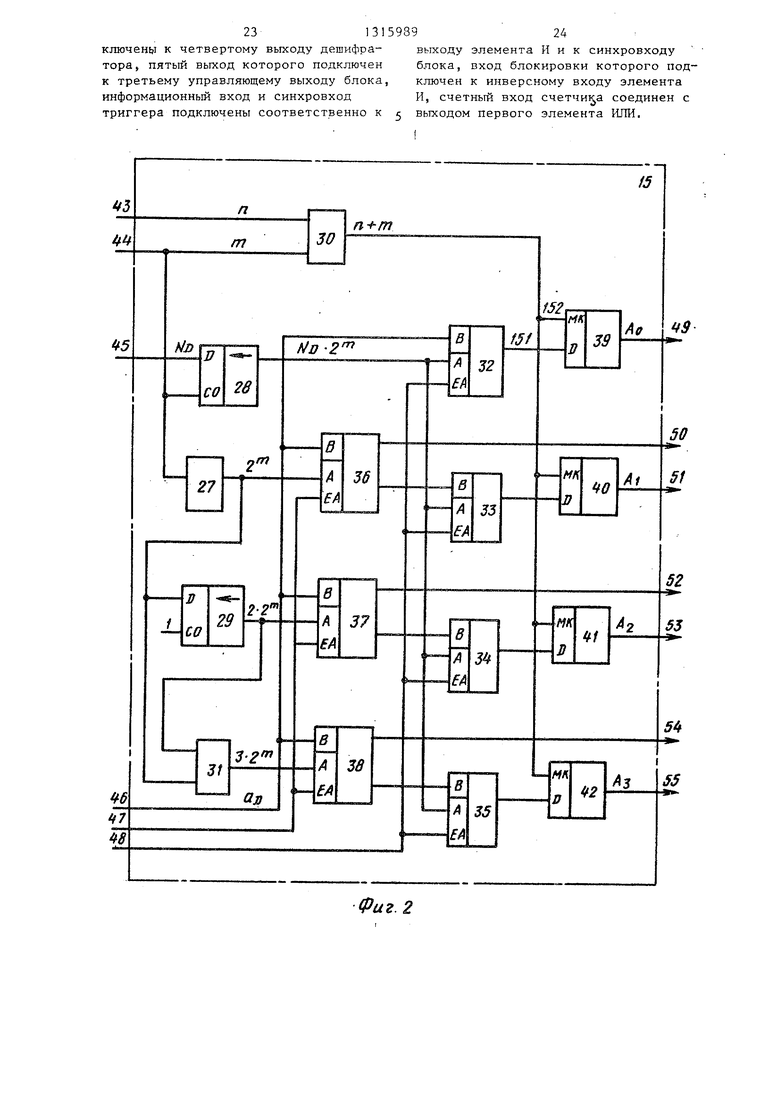

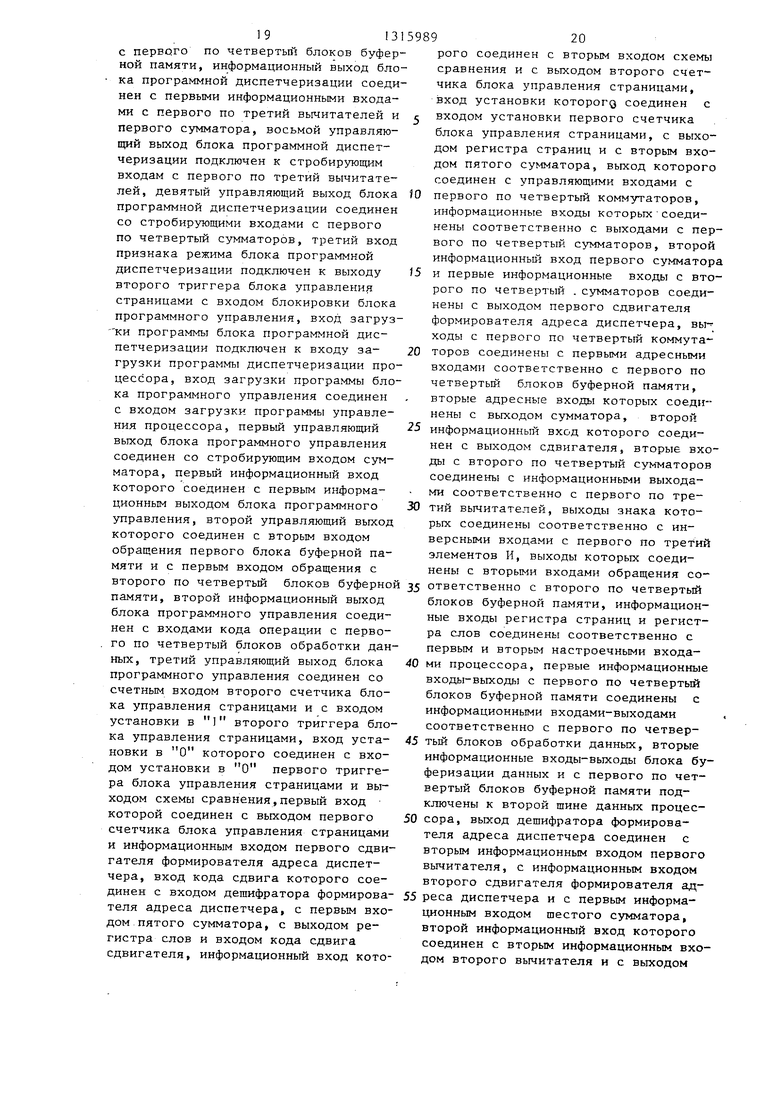

Формирователь 15 адреса диспетчера (фиг,2) содержит дешифратор 27, сдвигатель 28 и 29, сумматоры 30-35, вы- читатели 36-38 коммутаторы 39-42, входы 43-48 и выходы 49-55.

Блок 14 управления страницами (фиг.З) содержит первый 56 и второй 57 счетчики, схему 58 сравнения, первьш 59 к второй 60 триггеры} входы 61-63 и Е;ЬГХОДЫ 64-67.

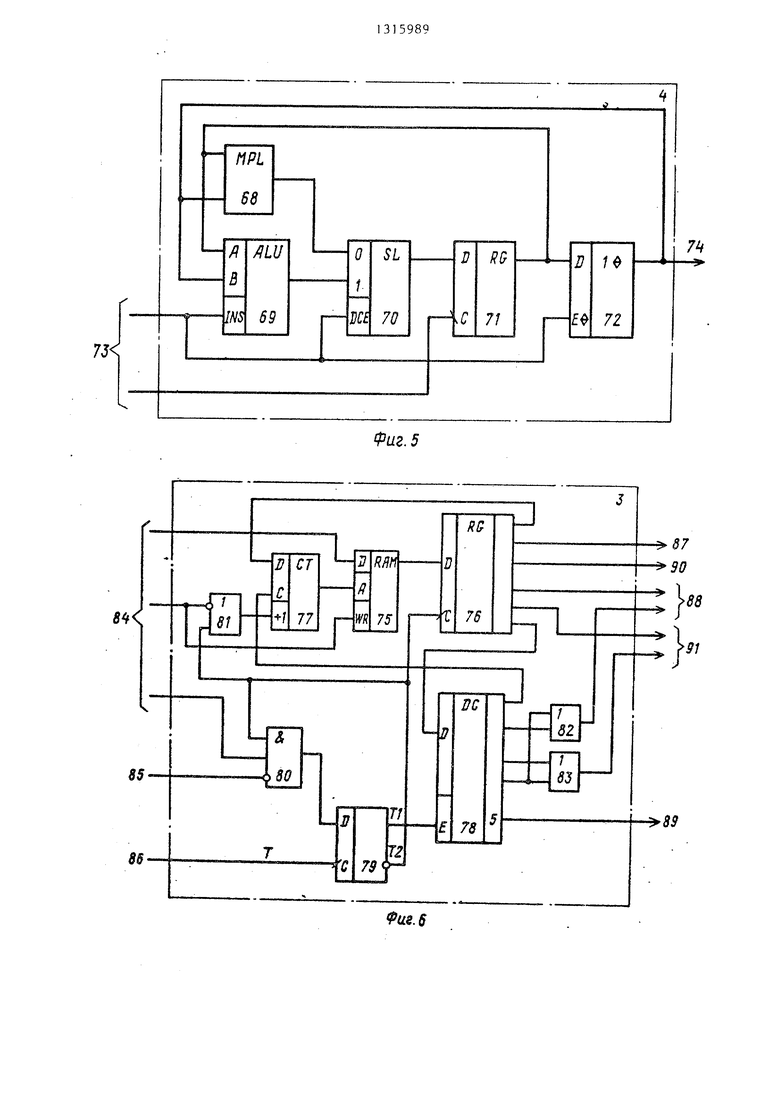

Блок обработки данных (фиг.5) содержит умновитель 68, арифметико-логический узел 69, селектор 70, регистр 71, узел 72 двунаправленной передачи данных; вход 73 кода операции и информационный вход-выход 74,

Блок 3 программного управления (фиг.6) содержит память 75j регистр 76, счетчик 77S дешифратор 78, три- гер 79, элемент И 80, элементы ИЛИ 81 -83, вход 84 загрузки, вход 85 бло кировки, синхровход 86, первый 87,второй 88 и третий 89 управляющие выходы, первый 90 и второй 91 информационные выходы.

Блок 2 программной диспетчеризации (фиг.7) содержит память 92, регистр 93s счетчик 94, дешифратор 95, триггер 96, элементы И 97-99, элементы ИЛИ 100-106, генератор 107 импульсов,, вход 108 загрузки программ, первый 109, второй ПО и третий 111 входы признака режима, с первого по де- сятый 112-120 управляющие выходы, информационный выход 121 и синхроны- ход 122.

3131

Каждый блок буферной памяти (фиг.8) содержит двухканальную память 123, четыре элемента НЕ 124- 127, первый 128 и второй 129 адресные входы, первый 130 и второй 13 входы обращения, вход 132 чтения-записи, первый 133 и второй 134 информационные входы-выходы.

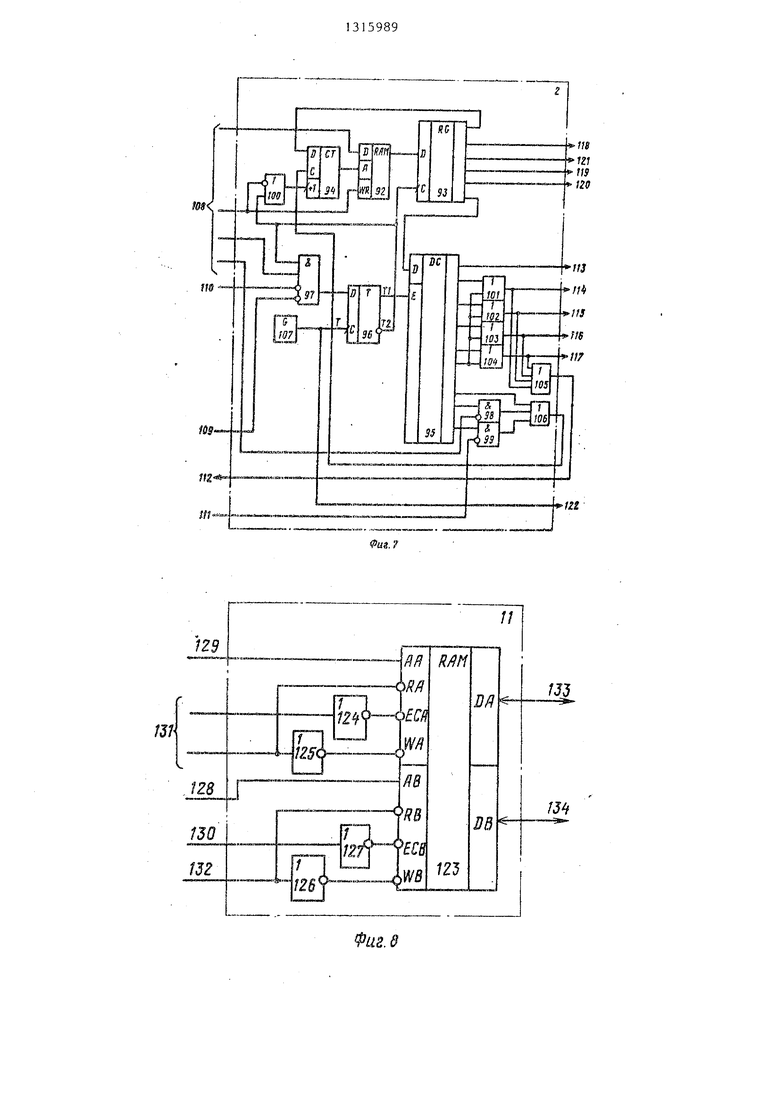

Блок 1 буферизации данных (фиг.9} содержит двухканальный регистр 135, четыре элемента И 136-139, триггер 140, первый информационный вход-выход 141, второй информационный вход- выход 142, выход 143 признака незанятости, первьш вход 144 чтения, вы- ход 145 признака занятости, первый вход 146 записи, второй вход 147 чтения и второй вход 148 записи.

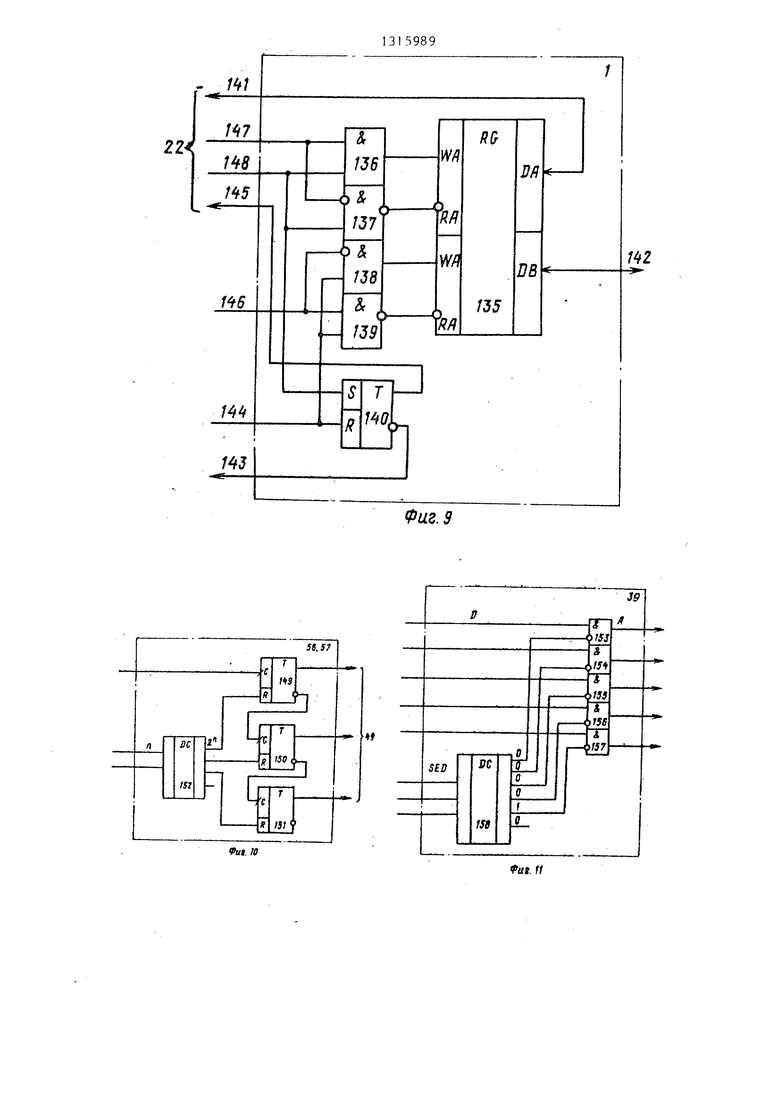

Счетчики 56 и 57 (фиг.10) содержат три триггера 149-151 и дешиф- ратор 152,коммутаторы 39-42 (фиг, 1) пять элементов И 153-157 и дешифратор 158.

Блок-схема алгоритма функциониро- вания параллельного процессора (фиг.12) представлена в виде программ, выполняемых в блоке 3 программного управления (блоки 159-1.64) и в блоке 2 программной диспетчериза- ции (блоки 165-176). Каждый блок 159- 176 представляет собой выполнение одной команды. Сплошные линии показывают направление выполнения программ, а пунктирные - связи синхро- низации между программами. Над каждым блоком 159-176 показано содержимое регистров 76 и 93 блоков программного управления 3 и программной диспетчеризации 2. Причем каждое из шеети полей регистров 76 и 93 отделены точками. Б обозначении содержимого полей применены символы X - безразлично, С-сложение, У - умножение, П - пересылка, В - выгрузка из уст- ройства обработки данных. Например, над блоком 159 (фиг.12) указано содержимое X.1.0.0.П.4, которое обозначает, что первое поле безразлично, второе поле установлено в 1, т.е. присутствует признак страничной адресации, пятое поле указывает на пересыпку в блоках 4-7 обработки данных, шестое поле указывает, что с выхода дешифратора 78 сигнал поступает на входы элементов ИЛИ 82 и 83, с выхода которых запрос передается в блоки 8- 1I, а сигнал Загрузить результат - в блоки 4-7 обработки данных.

Все блоки буферной памяти имеют .одинаковое распределение на страницы. Количество страниц и количество слов в странице задается перед началом работы. Количество страниц может задаваться как 2, где ri 1,2,3... и т.д., а количество слов в странице может задаваться как 2 , где m О,

U 2, 3... и т.д., причем объем V блока буферной памяти должен позволять разместить заданное количество страниц, для чего должно выполняться условие V7/ ,

При страничной адресации адреса для блоков буферной памяти представляют собой сумму базового адреса текущей страницы и номера слова в странице. Базовый адрес получается перемножением количества слов в странице на номер текущей страницы, а номер слова в странице выбирается из поля команды блока программного управления или блока программной диспетчеризации, запрашивающей блок буферной памяти.

Страничная адресация позволяет передать по одной команде одно данное, например, из блока-буферизации данных в одноименные страницы всех блоков буферной памяти. Каждая страница последовательно проходит три состояния: обмен данными через шину 21 пад управлением блока программной диспетчеризации, обмен данными с блоками обработки данных под управлением блока программного управления, хранение данных, когда нет обращения к данной странице. Формирователь адреса диспетчера позволяет формировать модифицированные страничные адреса для блоков буферной памяти при обмене данными между шиной 21 и блоками буферной памяти.

Блок 2 программной диспетчеризации служит для реализации программы передачи данных через шину 21,

Регистр 12 страниц и регистр 13 слов служат для хранения кодов m и п, определяющих соответственно количество страниц в блоке буферной памяти и количество слов в одной странице ..

Блок 4 управления страницами служит для определения номеров в N. и N текущих страниц, предназначенных соответственно для блока программной диспетчеризации и блока программного управления. Кроме того, блок страниц формирует признаки занятой страницы.

513

Счетчики 56 и 57 для формирования номеров текущих страниц, с которыми работает блок 2 программной диспетчеризации и блок 3 программного управления. Количество рабочих младших разрядов счетчиков ограничивается количеством страницj ноступа- ющим с выхода регистра 12 страниц. При выполнении команд Сменить страницу блоком 2 программной диспетча- риэации или блоком-3 программного управления управляющие сигнгшы Сменить страницу поступают на счетньге входы соответственно счетчиков 56 и 57 и увеличивают их содержимое на единицу.

Триггеры 59 и 60 предназначены ;для определения признака занятости страницу к которым обращаются блок ,2 про- грсшмной диспетчеризации и блок программного управления, блокируя при этом работу того из заказанных блоков 2 и 3, который обратился к занятой другими блоками странице,, т.е. при равенстве содержимых счетчиков 56 к 57.

При обращении блоков 2 и 3 к раз ным страницам, т„е. в случае, когда содержимое счетчиков 56 и 57 неравно схема 58 сравнения вырабатывает сигнал,, устанавливающий триггеры 59 и 60 в состояние незанятости страницj обеспечивая параллельную передачу запросов блока 2 программной диспетчеризации и блока 3 программного управ- лених; в блоки 8-11 буферной пам:яти.

Блок 4 управления страницами работает следующим образом.

При вьтолнении команды Сменить страницу блоком 2 программной диспетчеризации управляющий сигнал Сменить страницу по связи 61 поступает на счетный вход счетчика 56, увеличивая его содержимое на единицу, и на вход триггера 59, устанавливая его в состояние 1 (занята страница). Если содержимое счетчиков 56 и 57 окажет-- ся равным, т.е. блок 2 программной диспетчеризации запрещает страницу, которая еще занята блоком 3 программного управления, то триггер 59 оста нется в состоянии I. При этом признак занятой страницы: с выхода триггера 59 поступает в блок 2 программной диспетчериэаи 1И, блокиру; работу последнего. Триггер 59 сбрасывается в

состоян:яе О (незанята страница) , :когд 2 блок 3 программного у:аравле- :ккй зьшолняет команд:/ Сменить стра96

ницу. Управляющий сигнал С :нить страницу по связи 63 поступаем на счетный вход счетчика 57 и увеличивает его содержимое на единицу, схема

58 сравнения обнаруживает неравенство содержимых счетчиков 56 и 57 и формирует сигнал: сброса триггера 59. Отсутствие признака занятой страницы на выходе триггера 39 позволяет продолжить работу блоку программной диспетчеризации. Аналогично работают счетчик 57 и триггер 60.

СдБигатель 16 и сумматор 20 служат ,ау1я формирования адреса А для блоков

буферной памяти при обмене с блоками обработки данных. Адрес А может формироваться двумя видами адресации, прямым и страничны -, в соответствий с выражениями

20 А а.,

А Ny + а,,.

(и

(2)

где а - адресная часть команды блока программного управления, причем в выражении (, 1) это полный адрес для блока буферной памяти, а в выражении (2) - адрес слова в странице.

в режиме стра.ничной адресации базовый адрес текущей страницы управления формируется сдвигателем 16, где текущий номер страницы управления, поступающий с выхода 66 бло- ка 14, сдвигается в старшую часть на число разрядов, равное количеству слов в странице, поступающему с выхода регистра 13 слов.

В режиме прямой адресации сумматор 20 пропускает адресную часть а команды блока. 3 программного управления на выходэ с которого адрес А поступает во все блоки буферной памяти.

В режиме страничной адресации сумматор 20 суммирует адрес текущей страницы и адрес слова в странице в соответствии с выражением (2).

Блокировка одного входа сумматора

20 в режиме прямой адресации осуществляется пр:изнаком страничной адресации, посту:г1ающим по связи 87 из блока 3 программного управления.

Формирователь 15 адреса диспетчера служит для формирования адресов Ар и признаков отрицательной разности при обмене данными с щиной 21, используя при этом три вида адресации: прямую, страничную и модифицированную

страничную в соответствии с выражением

Ае

Ае Ае N

де а - е N. 2

+ а,

(3) (4) е-2 5)

С

адресная часть команды блока 2 программной диспетчеризации; Оадрес блока буферной памяти, принимает значения О, , 2, 3 соответственно для блоков 8-11.

J5

Базовый адрес N-.-2 текущей страницы диспетчеризации формируется,в сдвигателе 28, где текущий номер страницы NJJ диспетчеризации, поступающий с выхода 65 блока 14, сдвигает25

ся в старшую часть на число разрядов, 20 соответствии с выражением (3) признаки модифицированной страничной адресации на выходе 119 и страничной адресации на выходе 20 отсутствуют, вычитатели 36-38 и сумматоры 32-35 выполняют функцию пропускания адресной ajj части команды без искажения,

Элементы И 17-19 служат для блокировки запросов блоков 8-1 с целью предотвращения запирания полезной информации, когда разность , вычисляемая вычитателями 36-38, оказывается отрицательной. Для этого вы- читат ели 36-38 с выходов знака передают признаки отрицательной разности на входы элементов И 17-19, которые блокируют передачу запросов блоков 8-11. Если на входах элементов И 17- 19 отсутствуют признаки отрицательной разности, запросы с их выходов поступают в блоки 8-11.

равное количеству m слов в странице, поступающему с выхода регистра 13 слов.

Вычитатели 36-38 предназначены для вычисления разности е 2 в соответствии с выражением (5). На один из входов вычитателей поступает адрес ад, а на другие входы - смещение е-2. Для блоков 8-11 смещение соответственно равно 0,2, 2-2, 3-2.

Дешифратор 27 определяет количество слов 2. в одной странице. Величина количества слов в двух страницах 2-2 получается сдвигом в сдвигателе 29 величины 2 на один разряд в сторону старших разрядов.

Сумматор 31 формирует величину 3-2 количества Слов в трех страницах, суммируя величины 2 и 2-2 , Сумматоры 32-35 служат для суммирования разности и базового адреса Njj 2 в соответствии с выражением (5). При вычислении адреса в вычитателях 36- 38 могут быть переполнения в старшие разряды адресов, которые не выходят в область страничного распределения адресов буферов. Для обнуления этих старших разрядов адреса служат коммутаторы 39-42. Число разрядов адреса .п + т, отведенное под страничную адресацию, определяет сумматор 30. С выходов коммутаторов 39-42 адреса А-, А, Ал, А поступают соответственно в блоки 8-11.

Для вычисления модифицированного страничного адреса в соответствии с выражением (5) с выхода 119 блока 2

30

35

40

Параллельный процессор функционирует следующим образом.

Программы блока 2 программной г диспетчеризации и блока 3 программного управления пишутся на алгоритмическом языке и транслируются на язык загрузки. Перед выполнением задачи (процедуры) рабочие программы загружаются в память программ блока 3 программного управления через вход 24 и блока 2 программной диспетчеризации через вход 23, одновременно загружаются коды п и m в регистр 12 страниц и регистр 13 слов.

Кроме того, перед решением задачи счетчики 56 и 57 блока 14 обнуляются, подготавливая работу с нулевыми страницами блоков 8-11. Триггер 59 уста50

55

программной диспетчеризации признак модифицированной страничной адресации поступает на управляющие входы ЕЛ вычитателей 36-38, разрешая этим прохождение величин 2, 2-2, 3-2 на входы А, Аналогично с выхода 120 блока 2 программной диспетчеризации признак страничной адресации поступает на управляющие входы ЕА сумматоров 32-35, разрешая этим прохождение величины N.,- 2 на входы А.

Для вычисления страничного адреса в соответствии с выражением (,4) признак модифицированной страничной ад- ресации на выходе 119 отсутствует, вычитатели 36-38 выполняют функцию ЬропусканИя адресной ац части команды на выход.

Для вычисления прямого адреса в

25

20

30

35

40

Параллельный процессор функционирует следующим образом.

Программы блока 2 программной г диспетчеризации и блока 3 программного управления пишутся на алгоритмическом языке и транслируются на язык загрузки. Перед выполнением задачи (процедуры) рабочие программы загружаются в память программ блока 3 программного управления через вход 24 и блока 2 программной диспетчеризации через вход 23, одновременно загружаются коды п и m в регистр 12 страниц и регистр 13 слов.

Кроме того, перед решением задачи счетчики 56 и 57 блока 14 обнуляются, подготавливая работу с нулевыми страницами блоков 8-11. Триггер 59 уста0

5

навлнвается в состояние С (незанята страница )5 с выхода 64 признак незанятой страниць передается в блок 2 программной диспетчеризации, разретэ. тем самьм выполнение программы последнего. Триггер 60 устанавливается в состояние (занята страница), с выхода 67 признак занятой страницы передается в блок 3 программного управления, блокируя выполнение программы последнего.

Для решения задачи на входы 23 и 24 блоков программной диспетчеризации 2 и программного управления 3 поступают с гналы Разрешить работу

Программа блока 2 программной дис петчеризации начинает загружать входные операнды из блока I ь блоки 8-11 Для этого адресная часть а,у команды с выхода 12 блока 2 программной диспетчеризации поступает в формирова- тель 15 адреса диспетчера на входы вычитателей 36-38 и вход сумматора 32, далее на сумматоры 33-35 и коммутаторы 39-42 с целью формирования адресов для блоков 8-11 С выходов 119 и 120 блока 2 программной диспетчеризации признаки модифицированной страничной адресации и страничной адресации поступают в формирователь 15 адреса диспетчера на входы вычитателей 36-38 и сумматоров 32-35 для переключения режимов адреса1дии выражения (З Ig (4) и (5), указанных Б команде блока 2 программной диспетчеризации, С выходов 114-117 блока 2 программной диспетчеризации запросы через элементы И 17-19 поступают в блоки 8-1 для осуществления записи входных операндов в нулевые страницы, С выхода 18 блока 2 программной диспетчеризации признак записи-чтения поступает в блоки 8-11 и , причем блоки 8-1 выполняют запись с шины 21, а блок 1 - чтение операндов на. шину 21.

После загрузки нулевь х страниц блок программной диспетчеризации выполняет команду Сменить страницу, в этом случае с выхода ПЗ сигнал Сменить страницу поступает в блок 14 на счетный вход счетчика 56 и ус- танавливает его в состояние первой страницы. Счетчик 57 по пре;«нему установлен в состояние нулевой страницы, поэтому элемент 58 сравнения дает сигнал сброса триггеров 59 и 60 в состояние О (незанята страница). Блок 2 программной диспетчеризации

598910

начинает загрузку первой .ы и т.д. Блок 3 программного уииавле- ния разблокировывается и начинает выГ олнять программу обработки данных в 5 нулевых страницах. При этом управляющие сигналы с выхода блока 3 программного управления поступают в блоки 4-7 обработки данных и блоки 8-11. С выхода 90 блока 3 программного уп- 1G равления адресная часть а,, команды поступает на сумматор 20, с выхода которого адрес поступает в блоки 8- 1. С выхода 87 блока 3 программного управления признак страничной адJ5 ресации поступает на стробирующий вход сумматора 20 ,цля переключения режимов адресации выражения (1) и (2), указанных в команде блока 3 программного управления. С выхода 88

0 блока 3 программного управления запрос и признак чтения поступают на соответствующие входы блоков 8-11. Блоки 8-1 осуществляют чтение операндов из нулевых страниц и передают по свя5 зям 133 в блоки 4-7 обработки данных для обработки. Одновременно код вычислительной команды поступает в бло- -ки 4-7 обработки данных с выхода 91 блока 3 программного управления. Ре- зультаты обработки возвращаются в нулевые страницы, после чего блок 3 программного шравления выполняет команду Сменить страницу. На выходе 89 блока программного управления 35 сигнал Сменить страницу поступает на счетный вход счетчика 57, который устанавливается в состояние первой страницы, н, если она уже загружена блоком 2 программной диспетчеризации, 0 начинается обработка первой страницы. Через вход-выход 22 поступают вход- операнды и возвращаются результаты обработки. С выхода 144 и входа 109 блока программной диспетчеризации. 5 осуществляется запрос блока для обмена с шиной 2, С выхода 122 блока 2 программной дипетчеризации осуществляется диспетчеризация работы блока 3 программного управления. 0 ,

Пример загрузки буферньгх ОЗУ на процедуре Конволюционное умножение показан на фиг.2 и 4, В блоках 8-11 г:. задается восемь страниц по два сяо„ .

;ва в каждой странице, причем входной операнд Z загрулсается по нулево-- му адресу в странице, а X - по пер в ому.

1113

Блок- 2 программной диспетчеризации осуществляет первую загрузку нулевой -страницы в следующей последовательности.

Выполняются четыре команды загрузки Х , Xj, Xj и Х одновременно во все блоки 8-11 в режиме модифицированной страничной адресации, при этом адреса а задаются соответственно 1, 3, 5, 7. Получаем, что Х загружается только в нулевую страницу блока

8, а, например, X

1-3

- в блоки 9-11

соответственно в страницы 3, 2, 1. Затем выполняется команды загрузки операнда одновременно во все блоки 8-11 в режиме страничной адресации, при этом адрес ад равен нулю. После этого нулевая страница сменяется и передается на обработку.

Первая страница загружается двумя командами блока 2 программной диспетчеризации. Первая команда загружает X в режиме модифицированной страничной адресации с адресом а, равным 7, а вторая команда загружает Z, Загрузка последующих страниц аналогична загрузке первой страницы. После такой .загрузки входные данные X и Z собраны парами, готовыми для перемножения и подсуммирования.

Блок 3 программного управления пересылает данные из блоков 8-11 в блоки 4-7 обработки данных в режиме страничной адресации. Промежуточные результаты подсуммирования Y , Ул, , YJ и 4 хранятся в области с прямой адресацией по адресу 16 в блоках 8-11.,

Блок 4 обработки данных функционирует следующим образом.

Если необходима обработка данных блоке 4 обработки данных, блок 3 программного управления с выхода 91 передает код вычислительной команды на управляющие входы арифметико-логического узла 69, селектора 70 и узла 72 Например, необходимо вьшолнить вычисления Z X+Y. Первый операнд Z выгружается из блока 8 и по связи 133 поступает на вход В -арифметико-логического узла 69, который вьтолняет команду пропускания операнда на выход, селектор 70 пропускает операнд Z на вход регистра 71. По сигналу Загрузить результат, поступающему с выхода блока 3 программного управления, операнд Z записьшается в регистр 71. Умножение Z-X осуществля98912

ется на умножителе 68, причем операнд Z поступает с выхода регистра 71, а операнд X - из блока 8 по связи 133. Результат умножения записыва- с ется в регистр 71. Аналогично выполняется суммирование произведения с операндом У на арифметико-логическом узле 69. Результат суммирования записывается в регистр 71. Для передачи

o результата вычислений с выхода регистра 71 в блок 8 команда передачи поступает на управляющий вход Е узла 72.

Блок 3 программного управления

5 функционирует следующим образом.

Вначале память 75 загружается необходимыми для работы программами. После загрузки программы в память 75 счетчик 77 сбрасывается в состояние

0 О, поступает сигнал Разрешить работу БПУ на вход элемента И 80. Если на выходе 67 блока 14 отсутствует признак занятой страницы для обработки, элемент И ВО разблокирует триг5 гер 79, с выхода которого тактовые сигналы Т1, Т2 начинают поступать на -узлы блока 3 программного управления.

По каждому тактовому сигналу Т2 осуществляется загрузка очередной ко0 манды в регистр 76, а также приращение на единицу адреса команд в счетчике 77. По этому адресу из памяти 75 вЪ бирается следующая команда. Во время прохождения тактового сигнала

5 Т1 осуществляется исполнение текущих команд, загруженных в регистр 76. I

Разряды регистра 76 распределены на шесть полей.

Первое поле - адрес перехода передается в счетчик 77 для осуществления перехода по адресам программы. Второе поле - признак страничной адресации передается на стробирующий вход сумматора 20 и служит для переключения сумматора 20 с прямой адресации на страничную в соответствии с выражениями (I) и (2). Третье поле - адресная часть а команды передается

,. на вход сумматора 20 и служит для указания адреса в блоках 8-11. Четвертое поле - признак записи-чтения передается в блоки 8-11. При наличии этого признака блоки 8-11 осуществляют запись информации, передаваемой из блоков 4-7 обработки данных, а при отсутствии признака осуществляется чтение. Пятое поле - код вычислительной команды передается в блоки

5

5

1313

4-7 обработки данных для перестройки устройства на требуемое вычисление. Шестое поле -- код команды, передается на дешифратор 78для дешифрированргя :пяти команд блока 3 программного управления «

Блок 2 програм1 1ной диспетчеризации функционирует следующий образом.

Вначале память 92 загру ;ается необходимыми для работы программами. После загрузки .памяти 92 счетчик 94 сбрасывается в состояние 0 Поступает сигнал Разрешить работу БВД на вход элемента И 97, Если на выходе 64 блока 14 отсутствует признак занятой страницы для обмена с шиной 2 к из блока 1 по связи 109 не поступает признак закрытого регистра, то элемент И 97 разблокирует триггер 96,, с вькода которого тз.ктовые сигналы Т1 и Т2 начинают поступать на узлы блока 2 программной диспетчеризации. По каясцому тактовому сигналу Т2 осуществляется загрузка очередной команды в регистр 93, а также приращение на единицу адреса в счетчике 94 в По этому адресу из памяти 92 выбирается следующая команда. Во время rtpoxoж,цeиия тактового сигнала Т1 осуществляется исполнение такукгих команд, загруженных в 93.

Разряды регистра. 93 распределены иа шесть полей.

Первое поле - адрес перехода передается в счетчик 94 для осуществления перехода по адресам программны. Второе поле - призн:ак записн-чтения .передается в блоки 8--11 и блок 1. При наличии этого признака блоки 8- 11 осуществляют запись информацииа передаваемой из блока 1 через шину 215 при отсутствии признака осуществляетсп чтение. Третье поле адресная часть команды .перед.ается в формирователь 5 адреса даспетчера на вычита- тели и с умматор 32 и служит для указания адреса в блоках Четвертое поле признак страничной модифицированной адресации: передается в формирователь 15 адреса диспетчера на стробирующне входы вычитателей 36- 38 и: слуясит для переключения телей 36-38 на режим страничной но- .дифицированной адресации. Пятое по.пе - признак страничной адресации передается в формирователь 5 адреса диспетчера на сум аторы 32-35 и спу: кит для переключения на режим страничной

914

адресадии,, Шестое поле - код ттман- ды передается на дешифратор Ч для дешифрирования девяти команд блока 2 программной диспетчеризации. Если

тактовый сигнал Т поступит на стро- бирующий вход дешифратора 95, с выходов последнего сигналы поступают в соответствующие узлы для исполнения. Элементы ИЛИ 101-104 служат для

формирования запросов для блоков 8- 1 I. Если присутствует хотя бы один запрос, элемент ИЛИ 105 формирует запрос для блока 1. Элемент Ц 98 служит для выполнения перехода по отсутствию признака окончания массива.

Элемент И 99 сл}/жит для осуществления перехода занятой страницы для обработки. Указанны признак поступает с выхода 67 блока 14. Этот переход ин-.

формирует блок програкгмной диспетчеризации о том, что закончена обработка в блоках 4-7 обработки данных.

Блок буферной памяти функционирует следующим образом.

Если необходимо записать операнд с шины 21 .по входу DB памяти 123, с выхода 49 формирователя 15 адреса диспетчера на вход АВ памяти 123 подается адрес с выхода 118 блока 2 программной диспетчеризации через элемент НЕ 126, признак записи поступает на вход WB памяти 123. С выхода 114 блока 2 программной диспетчеризации через элемент НЕ 127 запрос подается на вход ЕСВ памяти. Если необходимо чтениеf то на вход РВ памяти 123 подается признак чтения. Аналогично выполняется запись или чтение по входу-выкоду 133 памяти 123.

Блок 1 буферизации данных функционирует след:утош 1м образом.

Триггер 140 сбрасывается в состояние О, Если необходимо записать операнд с входа 22 в регистр 135 и

передать на щину 21, на вход DA регистра 135 поступает операнд, признак записи, запрос, с выхода элемента И 136 строб записи поступает в регистр 135,по которомуосуществляется запись операнда в последний.Одновременно запрос поступает на вход триггера 40 и устанавливает его в состояние 1. С выхода триггера 140 признак занятости поступает на выход 45, запрещая передачу следующего операнда. С инверсного выхода триггера 140 приз- , нак незанятого регистра поступает по связи 143 в блок программной дис

петчеризации, который начинает выгружать операнд на ганну 21, Для этого с выходов 118 и 112 блока 2 программной диспетчеризации поступает соответственно признак записи-чтения и запрос блока приема информации. С выхода элемента И 139 строб чтения поступает на вход РА регистра 135, считанный операнд передается на шину 21. Триггер 140 устанавливается в со стояние О, разрешая тем самым загрузку операнда с входа 22.

Для примера загрузки блоков 8-11 по процедуре Конволюционное умножение (фиг.4) требуется восемь стра- ниц 2 8, где п 3(11), по два слова Б каждой странице 2 2, где m l(01)j. Тогда п + m 3+ 1 4(100)j . На выходе дешифратора 158 формируется код (010000) Сигнал с соответствующего выхода дешифратора 158 запрещает прохождение старшего разряда адреса через элемен И 157, так как восемь страниц по два слова занимают 16 слов в блоке 8. Старший разряд адреса, который может возникнуть в результате переполнения в сумматоре 32, блокируется элементом И 157.

Перед выполнением процедуры Кон- волюционное умножение блок 2 про-, граммной диспетчеризации и блок 3 программного управления загружаются программами. Одновременно загружаются коды п и m в регистр 12 страниц.и регистр 13 слов. Код m в данном случае равен 3, что соответствует восьми страницам 5 а код п равен 1, что соответствует двум словам в каждой странице (фиг.4).

Блок 159 - команда Выгрузить Z.

С выхода 90 адресная часть й команды, равная нулю, и с выхода 87 признак страничной адресации передаются на сумматор 20, с выхода коч оро го адрес, равный нулю, передается в блоки 8-11, С выхода регистра 76 признак чтения и с выхода элемента И 82 запрос поступают в блоки 8-11 ОЗУ с выходов которых операнды Z пере- даются на входы арифметико-логичес- ких узлов 69 блоков 4-7 обработки данных. С выхода регистра 76 код вычислительной команды поступает на входы узла 69 и селектора 70 и пере- ключает их на пересылку операнда Z. С выхода элемента ИЛИ 83 сигнал Загрузить результат поступает на управляющий вход регистра 71 блоков

4-7 обработки данных, где операнды записываются. Блок 3 программного управления переходит к выполнению следующей команды.

Блок 60 - команда Умножить Z-X.

Выполняется аналогично блоку 159 за исключением того, что адресная часть а,, команды на выходе 90 равна единице для выбора операнда X, а умножители 68 выполняют операцию умножения операндов X, поступающих из блоков 8-11, на операнды Z, хра- няющиеся в регистрах 71. Результаты умножения Р помеш,аются в регистры 71

Блок 161 - команда Сложить P+Y.

Выполняется аналогично блоку 160 за исключением того, что адресная часть а, равна 16, признак странично адресации отсутствует, т.е. адресация прямая, арифметико-логические узлы 69 выполняют операции сложения.

Блок 162 - команда Загрузить Y.

По этой команде результаты обработки из регистров 71 поступают на хранение в блоки 8-11 по адресу, равном 16.

Блок 163 - команда Сменить страницу .

С выхода 89 дешифратора 78 сигнал Сменить страницу поступает в блок 14 на счетный вход счетчика 56, увеличивается содержимое счетчика 57 на единицу, т.е. переходит с нулевой страницы на первую. Если содержимое счетчиков 56 и 57 равно, триггер 60 устанавливается в состояние занятой страницы для обработки. С выхода 67 признак занятой .страницы поступает в блок 3 программного управления и блокирует его работу. Если на выходе триггера 60 отсутствует признак занятой страницы, блок 3 программного управления может продолжить свою работу по программе.

Блок 164 - команда Переход.

С выхода дешифратора 78 сигнал перехода поступает на вход установки адреса в счетчик 77 команд. Адрес перехода передается с выхода регистра 76 на вход счетчика 77.

Блок 165 - команда Загрузить X.

С выхода 121 блока 2 программной диспетчеризации адресная часть а, равная единице, поступает на вьгаита- тели 36-38, сумматор 32.

С выхода 120 признак страничной адресации передается на сумматоры 32-35, а с выхода 119 признак стра17 131

ничной модифицированной адресации поступает на вычитатели 36-38, С выходов коммутаторов 39-42 стра тичнь е модифицированные адреса АО-АЗ передаются в блоки 8-11. С выхода 118 признак записи передается в блоки 8- 11. Этот признак также поступает в блок 1, но в качестве признака чтения. С выходов элементов ИЛИ 101-104

запросы поступают в блоки , С выхода элемента ИЛИ 105 блока программной диспетчеризации запрос поступает в блок I, Этими действиями инициируется выгрузка операнда X-из блока J на шину 21 и загрузка операнда X в блок 8,

Блоки 166-168 - команда Загрузить X.

Выполняются аналогично блоку 165 за исключением того, что адресная часть в каждом блоке соответстве но равна 3,5,7. Открываются последовательно элементы И 11-19 s увеличивается количество блоков буферной

памяти, загружаемых операндами X (фиг,4).

Блок 169 - команда Загрузить Z.

Команда выполняется с адресной частью а, равной О, и признаком страничной адресации.

Блок 170 - команда Сменить страницу .

В результате вьшолнения команды счетчик 56 увеличивает свое содержимое на единицу, т.е. переходит с нулевой страницы на первую.

Блок 171 - команда Переход, если не окончен массив.

Если блок принял послед-, ние операнды X и Z, то на вход блока программной диспетчеризации Z поступает признак окончания массива данных, Блбк 2 программной диспетчери- зацрш выполняет соответствующий переход.

Блок 172 - команда Переход, если пё. окончена обработка.

Если 3 блок программного управления сменяет последнюю обработанную страницу, с выхода триггера 60 приз- нак занятой страницы поступает на вход элемента И 99 для выполнения соответствующего перехода в блоке 2

i. Параллельный процессор, содер- жащий блок буферизации данных, блок программной диспетчеризации, четыре блока обраб зтки данных, блок программно го управления,синхровход которого соединен с синхровькодом блока программной диспетчеризации, первый управляющий выход которого соединен с первым входом чтения блока буферизации данных, вьгход признака незанятости которого соединен с первьц входом признака режима блока программной диспетчеризации, первый информацион- вход - выход,, выход признака занятости, первый вход записи и второй вход чтения блока буферизации данных подключены к первой шине данных процессора, отличающийся тем, что, с целью упрощения, он содержит формирователь адреса диспетчера, блок управления страницами, регистр страниц, ре;гистр слов, сдвига- тель, сумматор, три элемента И и четыре блока буферной памяти, причем формирователь адреса диспетчера содержит шесть cyMivjaTopoB, три вычита- теля, четыре коммутатора, дешифратор и два сдвигателя, блок управления страницами содержит два счетчика, два .триггера и схему сравнения, причем второй вход признака режима блока программной диспетчеризации соединен и с выходом первого триггера блока управления страницами, вход установки в I которого соединен со счетным входом первого счетчика блока управления страницами и с вторым управляющим выходом блока программной диспетчеризации, с третьего по шестой управляющие выходы которого соединены соответственно с первым входом обращения первого блока буферной памяти, с пря- MijiM входом первого элемента И, с прямым входом второго элемента И и с

программной диспетчеризации. Признак

занятой страницы указывает на то, что 55прямым входом третьего элемента И,

обработка данных блоков 4-7 законч-няседьмой управляющий выход блока программной диспетчеризации соединен с

Блоки 173-176- команды Выгру-вторым входам записи блока буферизазить Y. ,ции данных и с входами записи-чтения

При выполнении этих команд поочередно выгру:жаются результаты обработки Y - Yp в блок 1 в соответствии с выражением

V. I

jr1

Z + i-1, для i 1 до P.

ормула изобретения

5

0

5

5

0

5

0

i. Параллельный процессор, содер- жащий блок буферизации данных, блок программной диспетчеризации, четыре блока обраб зтки данных, блок программного управления,синхровход которого соединен с синхровькодом блока программной диспетчеризации, первый управляющий выход которого соединен с первым входом чтения блока буферизации данных, вьгход признака незанятости которого соединен с первьц входом признака режима блока программной диспетчеризации, первый информацион- вход - выход,, выход признака занятости, первый вход записи и второй вход чтения блока буферизации данных подключены к первой шине данных процессора, отличающийся тем, что, с целью упрощения, он содержит формирователь адреса диспетчера, блок управления страницами, регистр страниц, ре;гистр слов, сдвига- тель, сумматор, три элемента И и четыре блока буферной памяти, причем формирователь адреса диспетчера содержит шесть cyMivjaTopoB, три вычита- теля, четыре коммутатора, дешифратор и два сдвигателя, блок управления страницами содержит два счетчика, два .триггера и схему сравнения, причем второй вход признака режима блока программной диспетчеризации соединен и с выходом первого триггера блока управления страницами, вход установки в I которого соединен со счетным входом первого счетчика блока управления страницами и с вторым управляющим выходом блока программной диспетчеризации, с третьего по шестой управляющие выходы которого соединены соответственно с первым входом обращения первого блока буферной памяти, с пря- MijiM входом первого элемента И, с прямым входом второго элемента И и с

с первого по четвертьш блоков буферной памяти, информационный выход блока программной диспетчеризации соединен с первыми информационными входами с первого по третий вычитателей и первого сумматора, восьмой управляющий выход блока программной диспетчеризации подключен к стробирующим входам с первого по третий вычитателей, девятый управляющий выход блока программной диспетчеризации соединен со стробирующими входами с первого по четвертый сумматоров, третий вход признака режима блока программной диспетчеризации подключен к выходу второго триггера блока управления страницами с входом блокировки блока программного управления, вход загруз- ки программы блока программной диспетчеризации подключен к входу загрузки программы диспетчеризации процессора, вход загрузки программы блока программного управления соединен с входом загрузки программы управления процессора, первый управляющий выход блока программного управления соединен со стробирующим входом сумматора, первьй информационный вход которого соединен с первым информационным выходом блока программного управления, второй управляющий выход которого соединен с вторым входом обращения первого блока буферной памяти и с первым входом обращения с

второго по четвертьй блоков буферной 35 ответственно с второго по четвертый памяти, второй информационный выход блоков буферной памяти, информационные входы регистра страниц и регистра слов соединены соответственно с первым и вторым настроечньми входа- 40 ми процессора, первые информационные входы-выходы с первого по четвертый блоков буферной памяти соединены с информационными входами-выходами соответственно с первого по четвер- 45 тьш блоков обработки данных, вторые информационные входы-выходы блока буферизации данных и с первого по четвертый блоков буферной памяти подключены к второй шине данных процес- 50 сора, выход дешифратора формирователя адреса диспетчера соединен с вторым информационным входом первого вычитателя, с информационным входом второго сдвигателя формирователя ад- динен с входом дешифратора формирова- 55 реса диспетчера и с первым информа- теля адреса диспетчера, с первым вхо- ционным входом шестого сумматора,

второй информационный вход которого соединен с вторым информационным входом второго вычитателя и с выходом

блока программного управления соединен с входами кода операции с первого по четвертый блоков обработки данных, третий управляющий выход блока программного управления соединен со счетным входом второго счетчика блока управления страницами и с входом установки в 1 второго триггера блока управления страницами, вход установки в О которого соединен с входом установки в О первого триггера блока управления страницами и выходом схемы сравнения,первый вход которой соединен с выходом первого счетчика блока управления страницами и информационным входом первого сдвигателя формирователя адреса диспетчера, вход кода сдвига которого соедом пятого сумматора, с выходом регистра слов и входом кода сдвига сдвигателя, информационный вход которого соединен с вторым входом схемы сравнения и с выходом второго счетчика блока управления страницами, вход установки которого соединен с

входом установки первого счетчика блока управления страницами, с выходом регистра страниц и с вторым входом пятого суьматора, выход которого соединен с управляющими входами с

первого по четвертый коммутаторов, информационные входы которых соединены соответственно с вь ходами с первого по четвертый сумматоров, второй информационный вход первого сумматора

и первые информационные входы с второго по четвертый . сумматоров соединены с выходом первого сдвигателя формирователя адреса диспетчера, вьг ходы с первого по четвертый коммута торов соединены с первыми адресными входами соответственно с первого по четвертьш блоков буферной памяти, вторые адресные входы которых соединены с выходом сумматора, второй

информационный вход которого соединен с выходом сдвигателя, вторые входы с второго по четвертый сум маторов соединены с информационными выходами соответственно с первого по третий вычитателей, выходы знака которых соединены соответственно с инверсными входами с первого по третий элементов И, выходы которых соединены с вторыми входами обращения со

второго сдвига-геля формирователя адреса диспетчера, вход кода сдвига которого подключен к входу логическо единицы процессора, выход шестого сумматора соединен с вторым информа ционным входом третьего вычитателя.

2, Процессор по п„1р отличающийся теМу что блок программной диспетчеризации содержит регистр, память, счетчик, дешифратор, генератор импульсов, триггер, три элемента И и семь элементов ИЛИ, причем выход генератора импульсов соединен с синхровходом триггера и подключен к синхровыходу блока, ин- .формационный вход триггера соединен с выходом первого элемента. И, первь й прямой вход которого соединен с пряным входом первого элемента ИЛИ, с синхровходом регистра и с инверсным выходом триггера, прямой выход которого соединен со стробирующим входом деЕ ифратора, информационньш вход которого соединен с первым вь ходом регистра, второй выход которого сое-- динен с информационным входом счетчика, счетный вход которого соединен с выходом первого элемента ИЛИ, инверсный вход которого, информационный вход и вход чтени:я записи памяти, второй прямой вход первого элемента И и инверсный ззход второго элемента ШШ объединены и подключены к входу загрузки программы блока, первый и второй инверснь- е входы первого элемента И подключены: соответственно к первому и второму входам признака режима блока, синхровход и выход счетчика соединены соответственно с выходом второго элемента Ш1И и адресным входом памяти, выход которой соединен с информационньВ 1 входом регистра, третий, четвертый, пятый и шестой выходы которого являются соответственно седьмым, восьмым и девятьи управляющими и информационньвми выходами блока, выход третьего элемента ИЛИ подключен к первому управляющему выходу блока, первый выход де- ,щифратора подключен к второму управляющему выходу блока, третий управ- ЛЯЮ1ЦИЙ выход которого подключен к выходу четвертого элемента ИЛИ и к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу пятого элемента ИЛИ и к четвертому управляющему выходу блока,, пятый управляющий выход которого подключен к выходу шестого элемента И1И

0

0

5

989

- 5

30

35

40

45

50

55

22

и к третьему входу второго элемента ИЛИ, четвертый вход которого подключен к выходу седьмого элемента ИЛИ и к шестому управляющему выходу блока, с второго по пятый выходы дешифратора подключены к первым входам соответственно с четвертого по седьмой элементов ИЛИ, вторые входы которых подключены к шестому выходу дешифратора, с седьмого по девятый выходы которого подклЮ Чены соответственно к первому входу третьего элемента ИЛИ, прямому входу второго элемента Ник прямому входу третьего элемента И, инверсный вход которого нодклю- :чен к третьему входу признака режима блока, выходы второго и третьего элементов И подключены соответственно к второму и третьему входам третьего элеьшнта ИЛИ. .

3. Процессор по п.i, отличающийся тем, что блок программного управления содержит счетчик, память, регистр, элемент И, триггер, дешифратор и три элемента ИЛИ, причем информационный вход памяти, инверсный вход первого элемента ИЛИ, первый прямой вход элемента И и вход записи-чтения памяти объединены и подключены к входу загрузки программы блока, второй прямой вход элемента И соединен с прямым входом первого блока элемента ИЛИ, с синхровходом регистра и с инверсным выходом триггера, прямой выход которого соединен со стробирующим входом дешифратора, информационный вход которого соединен с первым выходом регистра, второй выход которого соединен с информационным входом счетчика, выход которого соединен с адресньм входом памяти, выход которой соединен с информационным входом регистра, третий и четвертый выходы которого подключены соответственно к первому управляющему и первому информационному выходам блока, пятый выход регистра и выход второго элемента ИЛИ объединены и подключены к второму управляющему выходу блока., шестой выход регистра и выход третьего элемента ИЛИ объединены и подключены к второму информационному выходу блока, первьй, второй и третий выхода1 дешифратора подключены соответственно к синхро- входу счетчика, к первому входу второго элемента ИЛИ и к первому входу третьего элемента ШИ, вторые входы второго и третьего элементов ИЛИ подключену к четвертому выходу дешифратора, пятый выход которого подключен к третьему управляющему выходу блока, информационный вход и синхровход триггера подключены соответственно к

выходу элемента И и к синхровходу блока, вход блокировки которого подключен к инверсному входу элемента И, счетный вход счетчи1 а соединен с выходом первого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления углом опережения зажигания двигателя внутреннего сгорания | 1984 |

|

SU1226482A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Многопроцессорная вычислительная система | 1979 |

|

SU751238A1 |

Параллельный процессор относится к области вычислительной техники и может быть использован для обработки сигналов с высокой производительностью. Цель изобретения - упрощение параллельного процессора. Параллельный процессор содержит формирователь 15 адреса диспетчера, блок 14 управления страницами, регистр 12 страниц, регистр 13 слов, сдвигатель, элементы И 17 - 19, сумматор 20, блоки 8-П оо ел 00 со

Фиг. 2

Фив.З

Фиг. 5

ст

J

№S

3/

sc

3

32

93

W

1Z1

ns ш

т

,оап,Л

i6Sm-тS Г И™

Фив. в

Фиг. 9

it

iT

f57

SED

SC

| Ассоциативный параллельный процессор | 1973 |

|

SU479114A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Однородный параллельный процессор | 1978 |

|

SU736107A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1985-12-23—Подача