I

Изобретение огносигся к дискретной технике и может быть использовано в цифровых вычислительных машинах.

Известны запоминающие устройства (ЗУ) с произвольным доступом к хранящейся информации ij и 2 .

Недостатком известных устройств является большое время поиска места и причин возникающих в ЗУ неисправностей.

Наиболее близким техническимреше- нием к предлагаемому является устройство для управления стековой памятью содержащее блок памяти, блок регистров, адресные шины и шину управления 3.

Недостатком указанного устройства является большое .время поиска причин неустойчивых (редко повторяющихся) сбоев в работе ЗУ.

Цель изобретения - повышение надежности работы устройства.

Поставленная цель достигается тем, . что в запоминающее устройство, содержащее блок памяти, блок регистров и аД-

ресные шины, введены коммутатор и блок кштропя, одни КЗ входов коммутагоров соединены с адресными шинами, а выходы - - С а/фесными входами блока naMstти и информационными входами блока ре гистров, причем блок контроля подключен к блоку памяти.

Кроме того, выходы блока регистров соединены с другими входами коммутатора.

o

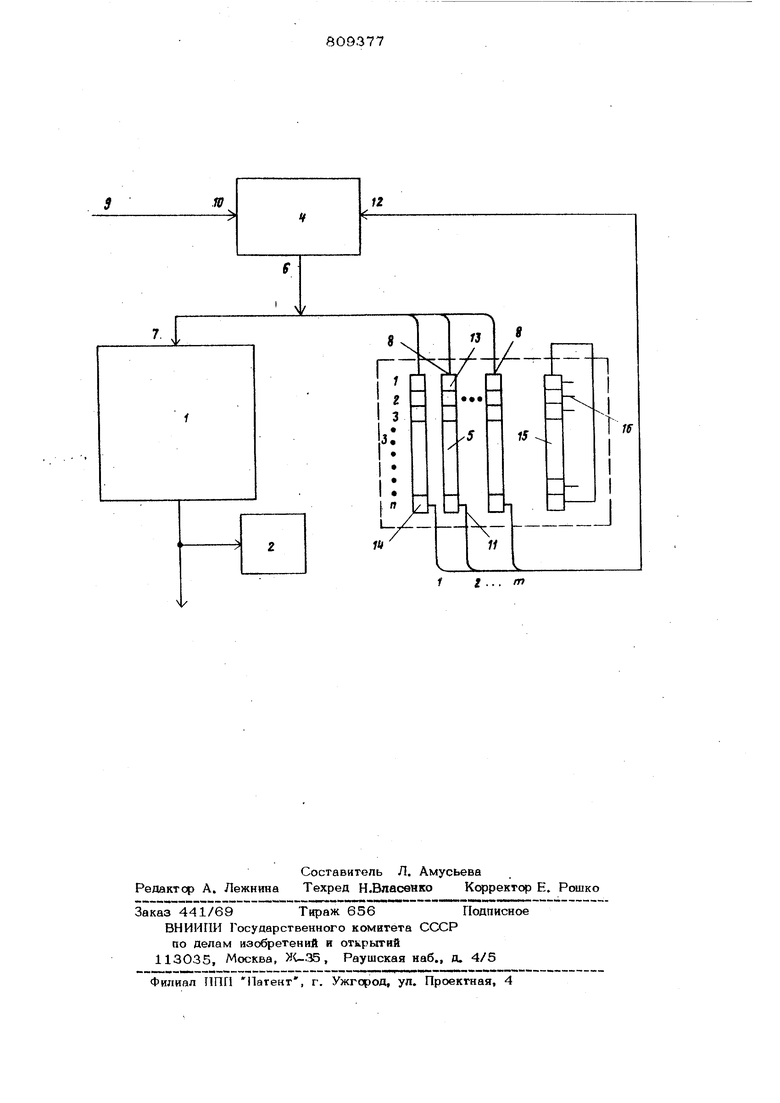

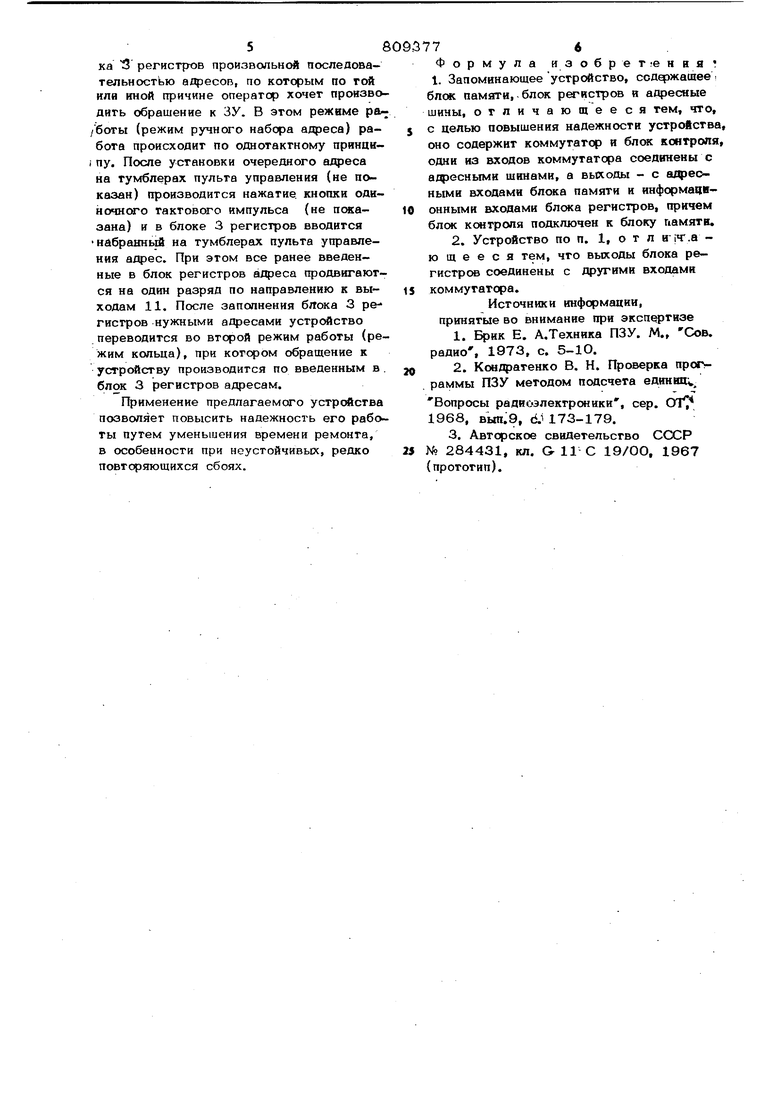

На чертеже представлена блок-схема запоминающего устройства..

Устройство содержит блок 1 памяти, блсж 2 контроля, блок 3 регистров и коммутатор 4.

S

Блок 3 регистров (блок стека) содержит п, п -разрядаых регистров 5 сдвига. Цепи, по которым на регистры 5 сдвига подаются тактовые (сдвигающие ;. импульсы,.вызывающие синхронные сдвиги находящейся в регистрах 5 информации, на чертеже не показаны (для упрощения чертежа). Выходы 6 коммутатора 4 соединены с адресными входами 7 блока 1 памяти и с информационными входами 8 блока 3 регистров. Адресные шины 9 уст ройства соединены с первой группой входов 10 коммутатора 4. Информационные выходы 11 блока 3 регистров соединены со второй группой входов 12 коммутатора 4. Устройство работает в трех режимах, которые условно называют нормальным режимом, режимом кольца и режимом ручного набора. Переход с одного режима работы на другой происходит, например при помощи внешних сигналов. При нормальном режиме работы коммутатор 4 осуществляет коммутацию (соединение) первой группы своих входов 10 с выходами 6, т.е. соединяет адресные шины 9 с .адресными входами 7 блока 1 памяти и с информационными входами 8 блсжа 3 регистров. Следовательно, в нчэмальном режиме работы при каждом обращении к ЗУ на входы 8 регистров 5 блока 3 регистров (т.е. в разряды 13 регистров 5) поступает и запоминается адрес, по которому происходит обращение к ЗУ. Одновременно все находящиеся в блоке 3 регистров (т.е. в регистрах 5) предыдущие адреса (по которым происходили предыдущие обращения к ЗУ) передвигаются в блоке 3 регистров на один разряд по направлению к выходам 11. Адрес, на- . ходившийся в последних разрядах 14 регистров 5 (т.е. по котфомупроисходило обращение к ЗУ и тактов тому назад) при очередаом обращении к ЗУ выбрасывается из блока 3 регистров. Таким образом, при работе в нормальном режиме в блоке 3 регистров находятся и послед них m -разрядных адресов, по которым происходило обращение к ЗУ. Следует отметить, что блек 3 регистров может стр иться не только на сдвигающих регистрах но и на параллельных регистрах (расположенных поперек направления передвиже ния информации). Если при работе ЗУ в нормальном ре ж,име произойдет сбой или отказ, то он обнаруживается блоком 2 контроля, который ироиаводит останов устройства ( .пре крашение дальнейших обращений). При эт в первых раундах 13 регистров 5 (если блок 2 контроля работает достаточно быстро) или в одном из последующих раз рядов окажется адрес, при обращении к , которому произощел сбой. Вся последовательност,ь адресов, находящихся после останова в блоке 3 регистров, представляе из собя аварийную ситуацию, привед1:;ую к сбою. После останова устройство из нормалього режима работы переводится (наприер вручную) во второй режим работырежим кольца. В этом режиме коммутатор 4 рсуществляет коммутацию второй группы своих входов 12 с выходами 6, т.е. соединяет информационные выходы 11 блсжа 3 регистров с информационными входами 8 блока 3 регистров (т.е. замыкает блок 3 регистров в кольцо) и с адресными входами 7 блока 1 памяти. Таким образом, при работе устройства в режиме кольца обращение к ЗУ происходит по хранящимся в блоке 3 регистров адресам, вращающимся по кольцу в той же последовательности, которая привела к сбою устройства, т.е. в этом режиме работы непрерывно и с высокой частотой воспроизводится аварийная ситуация. Именно в эгом режиме работы и производится обслуживающим персоналом поиск причин и места возникновения неисправностей, причем поиск существенно облегчен (в особенности при редко повторяющихся сбоях), т.к. аварийная ситуация воспроизводится многократно и с большой частотой. Для того, чтобы при работе устройства в режиме кольца облегчить и ускорить поиск места неисправности, желательно, чтобы осциллограф, при помощи которого обычно производится поиск неисправности, мог запускаться (так назьшаемая внешняя синхронизация осциллографа) в любом из г тактов, составляющих полный цикл блока 3 стека. С этой целью в устройство вводят дополнительный сдвигающий регистр 15, постоянно замкнутый в кольцо (вькод регистра 15 постоянно соединен с его входом). В этом кольце циркулирует одна единица (или один ноль), предварительно введенная тем или иным способом в регистр 15. Поэтому любой из п выходов 10 регистра 15 используется для запуска осциллографа в одном из h тактов. Тактовые (сдвигающие) входы регистра 15 (не показаны) также как тактовые входы блока 3 регистров сое динены с шиной управления. Поэтому в блоке 3 регистров и в дополнительном регистре 15 .все сдвиги происходят одновременно. Последний третий режим работы устройства (режим ручного набора адреса) предназначен для ручного заполнения блока 3 регистров произвольной последовательност ю адресов, ао которым по той или иной сфичине оператор хочет производить обращение к ЗУ. В этом режиме ра

боты (режим ручного набора адреса) работа происходит по одаотактному принцнпу. После установки очередного адреса на тумблерах пульта управления (не по казан) производится нажатие, кнопки одиночного тактового импульса (не показана) и в блоке 3 регистров вводится

нйбранньгй на тумблерах пульта управлеия адрес. При этом все ранее введенные в блок регистров адреса продвигаются на один разряд по направлению к выодам 11. После заполнения блока 3 регистров -нужными адресами устройство переводится во второй режим работы (режим кольца), при котором обращение к устройству производится по введенным в . блок 3 регистров адресам.

Применение предлагаемого устройства позволяет повысить надежность его работы путем уменьшения времени ремонта, в особенности при неустойчивых, редко повторяпощихся сбоях.

Формула изобрет енияг I. Запоминающее устройство, содержащее блсж памяти, блок ретистров и адресные шины, отличающееся тем, что, 5 с целью повышения надежности устройства, оно содержит коммутатор и блок контроля, одни из входов коммутатора соединены с адресными шинами, а выходы - с azipeoными входами блока памяти и информацв0 онными входами блока регистров, причем блок контроля подключен к блоку памяти. 2. Устройство по п. 1, о т л и |ч.а ю 1Д е е с я тем, что выходы блока регистров соединены с другими входами 5 коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Брик Е. А.Техника ПЗУ. М., Сов. радио , 1973, с. 5-10.

02. Кондратенко В. Н. Проверка nporv

. раммы ПЗУ методом подсчета единиц /

Вопросы радиоэлектроники , сер. ОТТ 1968, ВЫП.9, di 173-179.

3. Авторское свидетельство СССР № 284431, кл. G-11 С 19/00, 1967 (прототип).

3

п

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ контроля дискретных устройств при помощи счетчика | 1977 |

|

SU738180A1 |

| Устройство управления | 1983 |

|

SU1166108A1 |

| Постоянное запоминающее устройство | 1981 |

|

SU989586A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для исправления ошибок при итеративном кодировании | 1978 |

|

SU746528A1 |

| Вычислительная система | 1976 |

|

SU776320A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1104588A1 |

| Постоянное запоминающее устройство | 1983 |

|

SU1151573A1 |

| Ассоциативное запоминающее устройство | 1977 |

|

SU662972A1 |

. /

г.тИ/тг -,.

15

М

11

I ... т

Авторы

Даты

1981-02-28—Публикация

1978-01-17—Подача