I

Изобретение относится к дискретной Т1эхнике и может быть исяользовано в цифровых вычислительных машинах, устройствах передачи дискретной информации и т.п.

Известны устройства контроля правильности работы аппаратуры дискретного действия, проверяющие правильность хр нящейс:я, передаваемой или обрабатываемой инфс змации, содержащие свертки (схемы определения четности или нечетности информации l , 2 и з .

Недостатком извёбтных устройств является невозможность исправления много- кратных ошибок в контролируемом коде.

Наиболее близким техническим реше- ., нием к предлагаемому является устройство для исправления ощибок при итеративном кодировании, содержащее блок хранения информации с дешифратором адреса, сумматор по модулю два, регистры, эле- JQ менты И и блок сравнения .

Недостатком устройства является невозможность исправления любых четных много1фатных (т.е. двойных, четверных и

т.д.) ошибок в любом из контролируемых информационных регистров.

Целью изобретения является повышение надежности работы контролируемой аппаратуры дискретного действия.

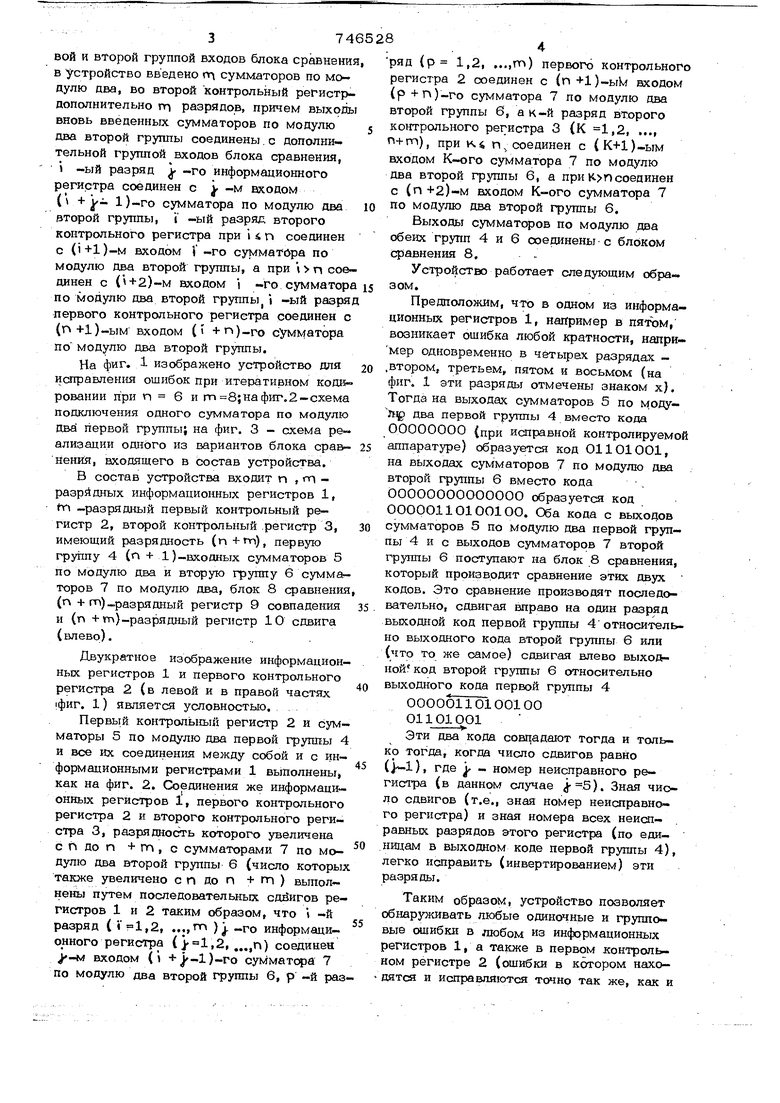

Поставленная цель достигается тем, что в устройство для исправления сшибок при итеративном кодировании, содержащее п ,т - разрядных информационных p9ГИстров, первый т- разрядный контрольный регистр и второй п - разрядный конти, рольный регистр, первую группу из гл..сумматоров по модулю два, вторую группу из г сумматоров по модулю два и блок сравнения, причем информационные выходы каждого t -го разряда всех информационнь1х регистров соединены с соответствующими входами -го сумматора по модулю два первой группы, выход i -го разряда первого контрольного регистра соединен с (п +1)-м входом -го сумматора по модулю два первой группы, выходы сумматоров по модулю два первой и вто- рой групп соединены соответственно с первой и второй группой входов блока сравнения в устройство введено гп сумматоров по мо дулю два, во второй контрольный регистрдополнительно m разрядов, причем выходы вновь введенных сумматоров по модулю два второй группы соединены. с дополнительной группой входов блока сравнения, -ый разряд -го информационного регистра соединен с . -м входом ( + 1)-го сумматора по модулю два второй группы, i -ый разряд второго контрольного регистра при i i n соединен с (i+l)-M входом } -го сумматора по модулю два второй группы, а при n соединен с ( + 2)-м входом | -го сумматора по модулю два второй группы, i -ый разряд первого контрольного регистра соединен с (п+1)-ым входом (i +п)го сумматора по модулю два второй группы. На фиг. 1 изображено устройство для исправления ошибок при итеративном коЩ5 ровании при n 6 и гп 8;на фиг,2-схема подключения одного сумматора по модулю два первой группы; на фиг. 3 - схема реализации одного из вариантов блока сравнений, входящего в состав устройства, В состав устройства входит n , разрйдньтх информационных регистров 1, Y -разрядный первый контрольный регистр 2, второй контрольный .регистр 3, имеющий разрядность (), первую группу 4 (п + 1)-входных сумматоров 5 по модулю два и вторую группу 6 сумматоров 7 по модулю два, блок 8 сравнения (п + т)-разрядный регистр 9 совпадения и (п + т)-разрядный регистр 10 сдвига (влево). Двукратное изображение информационных регистров 1 и первого контрольного регистра 2 (в левой и в правой частях 1ФИГ. 1) является условностью. Первый контрольньц регистр 2 и сумматоры 5 по модулю два первой группы 4 и все их соединения между собой и с информационными регистрами 1 выполнены как на фиг. 2. Соединения же информационных регистров 1, первого контрольного регистра 2 и второго контрольного регистра 3, разрядность которого увеличена с П до п + га , о сумматорами 7 по модулю два второй группы 6 (число которых также увеличено с п До п + m ) выполнень путем последовательных сдйигов регистров 1 и 2 таким образом, что -и разряд ( ,2, ...,гп ) J. -го информационного регистра (,2, ...,п) соединен -м входом ( +J-l)-ro сумматора 7 по модулю два второй группы 6, р -и раз яд (р 1,2, ,..,гп) первого контрольного егистра 2 соединен с (п+1)-ы входом (р +п)-го сумматора 7 по модулю два торой группы 6, а к-и разряд второго контрольного регистра 3 (К 1,2, ..., +т), при Кб п, соединен с (К+1)-ым входом К-ого сумматора 7 по модулю два второй группы 6, а при К.псоединен с (п+2)-м входом К-ого сумматора 7 по модулю два второй группы 6. Выходы сумматоров по модулю два обеих групп 4 и 6 соединены-с блоком сравнения 8.Устройство работает следующим образом. Предположим, что в одном из информационных регистров 1, например в пятом, возникает ошибка любой кратности, например одновременно в четырех разрядах втором, третьем, пятом и восьмом (на фиг. 1 эти разряды отмечены знаком х). Тогда на выходах сумматоров 5 по моду Л д два первой группы 4 вместо кода 00000000 (при исправной контролируемой аппаратуре) образуется код О11О10О1, на выходах сумматоров 7 по модулю два второй группы 6 вместо кода ОООООООООООООО образуется код ОО00011О10О1ОО. Оба кода с выходов сумматоров 5 по модулю два первой группы 4 и с выходов сумматоров 7 второй группы 6 поступают на блок 8 сравнения, который производит сравнение этих двух кодов. Это сравнение производят последовательно, сдвигая вправо на один разряд выходной код первой группы 4 относительно выходного кода второй группы 6 или (что то же самое) сдвигая влево выходной код второй группы 6 относительно выходного кода первой группы 4 00000110100100 01101001 Эти два кода совпадают тогда и только тогда, когда число сдвигов равно ()t где - номер неисятравного регисчра (в данном случае --5). Зная число сдвигов (т.е., зная номер неисправного регистра) и зная номера всех неисправных разрядов этого регистра (по единицам в выходном коде первой группы 4), легко исправить (инвертированием) эти разряды. Таким образом, устройство позволяет обнаруживать любые одиночные и групповые ошибки в любом из информационных регистров 1, а также в первом контрольном регистре 2 (ошибки в котором находятся и испртвляются точно так же, как и

ошибки в информационных регистрах 1) и во втором контрольном регистре 3 (при ошибках во втором контрольном регистре 3 выходной код первой группы 4 не содержит единиц, единицы в выходном коде j второй группы 6 указывают неисправные разряды второго контрольного регистра 3).

Само сравнение кодов в блоке 8 сравнения можно производить при помощи самых различных схем, например при помо- 10 щи (п + т)-разрядного сдвигающего (влево) регистра 1О и m -разрядной схемы совпадения 9 (фиг. 3). Более быстро (без сдвигающих регистров, требующих до h временных тактов )сравнениб производят 15 при помощи (п+1)т-разрядных схем сов падения (подобньгх схеме 9), соответст&ующим образом соединеннь х с выходами сверток 5 и 7.

Обнаружение и исправление ошибок, в 20 первом контрольном регистре 2 не является обязательным условием работы устройства (связанное с этим обнаружением и исправлением оборудование изображено пунктиром, фиг. 1).25

Следует отметить, что использование термина регистр (применительно к информационным и контрольным регистрам 1,2 и 3) является в известной степени условностью. В реальных объектах контролируем- 3Q мые (информационные) и контрольные коды вырабатываются не только регистрами, но и различными другими элементами и устройствами - микросхемами памяти, различными блоками цифровых вычислительныхз5 машин и других дискретных устройств (арифметическими и запоминающими устройствами, блоками ввода-вьшода, каналами связи и т.д.)

.Применение устройства для исправления ошибок при итеративном кодировании позволяет существенно повьюить надежность работы различных видов аппаратуры дискретного действия, а также позволяет строить такую аппаратуру из частично де-45 фектных комплектующих изделий, например позволяет применять микросхемы памяти,. в которых по отдельным адресам находятся неисправные запоминающие элементы, увеличивать периоды работы систем между 50 профилактическими ремонтами и т, д. Формула изобретения Устройство для исправления ошибок при итеративном кодировании, содержащее п , m-разрядных информационных регист - 55

ров, первый гг разрядный контрольный регистр и второй п -разрядный контрольный регистр, первую группу из m сумматоров по модулю два, вторую группу из г сумматоров по модулю два и блок сравнения, причем информационные выходы каждого I -го разряда всех информационных регистров соединены с соответствующими .входами -го сумматора по модулю два первой группы, выход 1 -го разряда первого контрольного регистра соединен с ()-M входом -го сумматора по модулю два первой группы, выходы суммато ров по модулю два первой и второй группы соединены соответственно с первой и второй группой входов блока сравнения,

0т л и ч а ю щ е е с я тем, что, с целью повышения надежности в устройство введено m сумматоров по модулю даа, а во второй контрольный регистр - дополнительно гп разрядов, причем выходы вновь введенных сумматоров по модулю два второй группы соединены с дополнительной группой входов блока сравнения, i -ый разряд I. -го информационного регистра соединен с v -м входом ( -1 )-го сумматора по модулю два второй группы,

1-ый разряд второго контрольного регистра при | г соединен с ( i +1)-м входом 1 -го сумматора по модулю два второй группы, а при i соединен с ( +2)-м входом i -го сумматора по модулю два второй группы, i -и разряд первого контрольного регистра соединен с (п+1)-ым входом (| +г)-.го сумматора по модулю два второй группы.

Источники информации, принятые во внимание при экспертизе

1.Сидоров А. М, Методы контроля электронных цифровых машин. М., Советское радио, 1966, с. 97-98,

2.Самофалов К. Г. и др. Структурно-логические методы повышения надежности запоминающих устройств. М-., Машиностроение, 1976, с. 4О-47.

3.Селлерс Ф. Методы обнаружения ошибок в работе ЭЦВМ. М., Мир, 1972, с. 269-270.

4.Авторское свидетельство СССР Ny 364О32, кл. G- 11 С 29/ОО, 25.О1.71 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции групповых ошибок @ источников информации | 1980 |

|

SU1290425A1 |

| Постоянное запоминающее устройство | 1983 |

|

SU1151573A1 |

| Запоминающее устройство | 1989 |

|

SU1716570A1 |

| Запоминающее устройство | 1990 |

|

SU1801227A3 |

| Запоминающее устройство | 1990 |

|

SU1794261A3 |

| Запоминающее устройство | 1990 |

|

SU1753491A1 |

| Запоминающее устройство | 1988 |

|

SU1635224A1 |

| Устройство для коррекции ошибок в дискретной информации,передаваемой кодом Хемминга | 1980 |

|

SU1040610A1 |

| Запоминающее устройство | 1978 |

|

SU809377A1 |

| Постоянное запоминающее устройство с самоконтролем | 1988 |

|

SU1532979A1 |

Авторы

Даты

1980-07-05—Публикация

1978-04-14—Подача