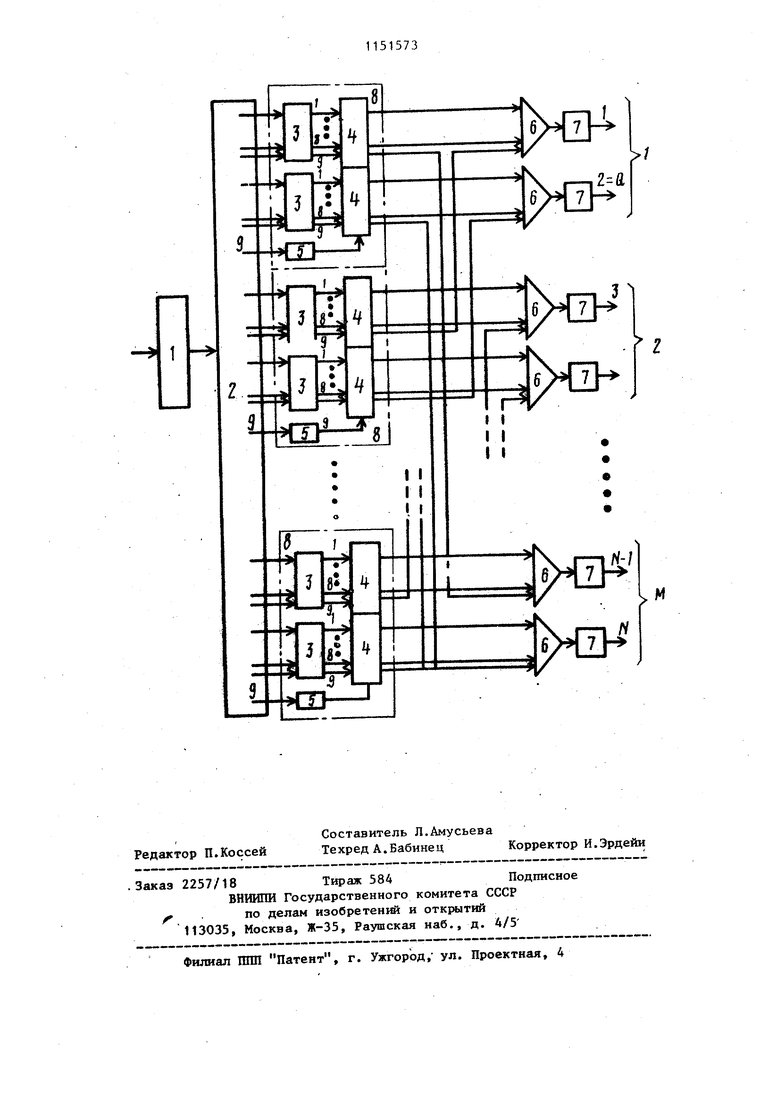

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля исправности работы различных дискретных устройств, в частности запоминающих. Известны запоминающие устройства с контролем информации по модулю дв (контроль по четности или нечетноети) 1. Недостатком подобных устройств является пропуск (необнаружение) от казов при некоторых видах неисправностей. Наиболее близким к изобретению п технической сущности является магни ное полупостоянное запоминающее устройство на микробиаксах, содержа щее накопитель, разрядные выходные ячейки, каждая из которых содержит 18 усилителей воспроизведения (2 ба та), 18 триггерав регистра числа и формирователь плавающего строба, управляющий приемом в регистр числа Контроль информации производится при помощи побайтовых сверток, уста новленных на выходах регистра числа 2 , Недостатком известного устройств является пропуск отказа при исчезно вении строба регистра числа, т.е. низкая надежность. При отказе формирователя плавающего строба в триггерах регистра числа сохраняется предыдущая исправная информация, и поэтому данная неисправность не будет обнаружена. Целью изобретения является повышение надежности работы запоминающе го устройства. Поставленная цель достигается тем, что в постоянном запоминающем устройстве, содержащем накопитель, N многовходовых сумматоров по модулю два (где N - количество байтов в считываемых числах), выходы которых соединены с входами триггеров ощибо М выходных разрядных ячеек (где Nг М 1), каждая из которых состоит и Q регистров числа (,N кратно Q и М Q групп усилителей воспроизведения и формирователя строба,вход формироват ля строба каждой выходной разрядной ячейки соединен с соответствующим выходом накопителя, а выход - с управляющими входами всех регистров числа данной ячейки, информационные выхода накопителя соединены с соот732ветствующими входами усилителей воспроизведения, выходы усилителей воспроизведения каждой группы - с информационными входами соответствующего регистра числа, все входы, кроме последнего, каждого сумматора по модулю два соединены с соответствующими выходами соответствующего регистра числа, последний выход i-ro регистра числа (i 1,2,...,Q) соединен с последним входом N-Q+i-ro сумматора по модулю два, последний выход j-ro регистра числа (j Q+1, ,. . . ,N) - с последним входом j-Q-ro сумматора по модулю два. На чертеже представлена функциональная схема предложенного постоянного запоминающего устройства. Устройство содержит адресные дещифраторы 1, накопитель 2, усилители 3 воспроизведения, регистр 4 числа, формирователи 5 стробов регистра числа, сумматоры 6 по модулю два (свертки) и триггеры 7 ошибок.Усилители 3 воспроизведения, регистр 4 числа и формирователи стробов 5 расположены в М разрядных ячейках 8, являющихся конструктивным элементом замены (при поломке ячейки). Входы формирователей 5 стробов соединены со стробовыми разрядньми шинами 9 накопителя 2 (во всех запоминающих элементах каждой из М стробовых шин 9 записаны единицы). В каждом из М ячеек 8 размещено оборудование Q байтов (на чертеже 1 ) по 9 разрядов каждый (8 информационных разрядов и один контрольньй). Каждый из байтов контролируется на четность (или нечетность) девятивходовым сумматором по модулю два (сверткой). Выходы триггеров регистра 4 числа, в которых хранятся контрольные разряды байтов, соединены не со свертками 6 байтов, находящихся в данной ячейке 8, ас входами сверток 6 байтов, находящихся в соседней ячейке 8. При этом в ячейку 8 из накопителя 2 поступают контрольные разряды не тех байтов, которые расположены в данной ячейке 8, а контрольные разряды байтов соседней ячейки. Предлагаемое устройство работает следукщим образом. Выходные сигналы накопителя 2 усиливаются усилителями 3 воспроизведения и подаются на информационные входы триггеров регистра 4 числа. Прием информации в триггеры регистра 4 числа происходит в мо- . мент подачи строба на триггеры, Стробы вырабатываются формирователями 5 (в каждой ячейке 8 находит.ся один формирователь 5 строба, управляющий приемом информации во все триггеры регистра числа 4 данной ячейки).

Выходные сигналы триггеров регистра 4 числа Лоступают на входы сумматоров 6 по модулю два. При несовпадении четности в каком-либо байте сигнал ошибки с выхода соотвествующей свертки 6 поступает в триггер 7 ошибки данного байта, где запоминается.

При отказе (или сбое) одного из формирователей 5 стробов такой отка будет обнаружен, причем одновременно четырьмя свертками: двумя свертками двух байтов поврежденной ячейки 8 и двумя свертками байтов, контрольные разряды которых находятся в поврежденной ячейке 8 (каждая из этих четырех сверток при каждом считывании обнаруживает отказ формирователя 5 строба с вероятностью О , 5).

Изобретение моткет быть применено для контроля исправности работы не только запоминающих, но и других дискретных устройств, в которых исчезновение строба, управляющего приемом информации в регистры, не обнаруживается другими схемами контроля. Контролируемая по модулю два группа может содержать не 9 разрядов, а иное количество разрядов.

Применение изобретения позволяет повысить надежность работы ЗУ и в сочетании с другими известными методами контроля полностью охватить контролем всю аппаратуру запоминающего устройства.

Базовым объектом для изобретения является магнитное полупостоянное запоминающее устройство на микробиаксах 2 , т.е. базовый объект является одновременно прототипом изобретения. Поэтому изложенные преимущества изобретения (повышение надежности работы устройства благодаря более полному контролю) является одновременно и техническим преимуществом предлагаемого запоминакндего устройства по сравнению с npoTOTimoM

w

2-fl

IF

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Запоминающее устройство | 1975 |

|

SU639016A1 |

| Устройство для исправления ошибок при итеративном кодировании | 1978 |

|

SU746528A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Устройство для задержки информации с контролем | 1990 |

|

SU1795442A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU879655A1 |

| Запоминающее устройство | 1990 |

|

SU1794261A3 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

ПОСТОЯННОЕ ЗАПОМИНАКЯЦЕЕ УСТРОЙСТВО, содержащее накопитель, N многовходовых сумматоров по модулю два (где N - количество байтов в считываемь1Х числах) , выхода которых соединены с входами триггеров ошибок, М выходных разрядных ячеек (где N г М 1), каждая из которых состоит из Q регистров числа (Q N/M, N кратно Q и М), Q, групп усилителей воспроизведения и формирователя строба, вход формирователя строба каждой выходной разрядной ячейки соединен с соответствукицим выходом накопителя, а выход - с управляющими входами всех регистров числа данной ячейки, информационные выходы накопителя соединены с соответствующими входами усилителей воспроизведения, выходы усилителей воспроизведения каждой группы с информационными входами соответствующего регистра числа, все входы, кроме последнего, каждого сумматора по модулю два соединены с соответствукщими выходами соответствующего регистра числа, отличающее(Л с я тем, что, с целью повышения надежности устройства, последний выход i-ro регистра числа (i 1,2,.. ..,Q) соединен с последним входом N - Q + i-rp сумматора по модулю два, последний выход j-ro регистра числа (J Q-H, Q+2,...,N) - с последним входом j-Q-ro сумматора по ел модулю два. сд со

i-.

y4ZK

bcih

LM

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Путинцев Н.Д | |||

| Аппаратный контроль управляющих цифровых вычислительных машин | |||

| Двухтактный двигатель внутреннего горения | 1924 |

|

SU1966A1 |

| СПОСОБ СОСТАВЛЕНИЯ ЗВУКОВОЙ ЗАПИСИ | 1921 |

|

SU276A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Коренев Н.И | |||

| ТКАЦКИЙ СТАНОК | 1920 |

|

SU300A1 |

| Всесоюзная научно-техническая конференция Развитие теории и техники хранения информации | |||

| Тезисы докладов, М., Радио и связь, 1983, с | |||

| Прибор, автоматически записывающий пройденный путь | 1920 |

|

SU110A1 |

Авторы

Даты

1985-04-23—Публикация

1983-12-08—Подача