Изобретение относится к вычислительной технике, в частности к полупроводниковым запоминающим устройствам (ЗУ).

Известно запоминающее устройство с самоконтролем, содержащее блоки памяти, формирователи контрольных разрядов кода Хэмминга, формирователи проверочного адова, дешифратор одноразрядных ошибок, схему обнаружения двухразрядных ошибок 1.

В данном устройстве не используется режим контрольного считывания с перезаписью скорректированной Информации в паузах обращения к ЗУ, что снижает достоверность хранимой информации.

Наиболее близким к предлагаемому является запоминающее устройство с самоконтролем, содержащее накопитель, соединенный с регистро.м записи, блоком воспроизведения и регистром числа, блок коррекции, блок контроля, подключенные к блоку управления, в котором осуществляется перезапись скорректированной информации в накопитель только по тому адресу, по которому информация считывалась потребителем 2.

В известном устройстве могут появиться «мягкие отказы, связанные с о(-частицами, излучаемыми корпусами микросхем, космическими лучами и электромагнитными импульсами. Если при этом не проводить контрольного считывания с перезаписью скорректированной информации, то сбой накапливаются и вероятность отказа ЗУ растет. Таким образом, недостатком устройства является отсутствие автоматического контрольного считывания и перезаписи скорректированной информации в паузах обращения потребителя к ЗУ, что существенно снижает надежность устройства.

Цель изобретения - повышение надежности устройства путем обеспечения возможности коррекции записанной информации в паузах обращения к устройству.

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее накопитель, входной регистр числа, коммутатор записи, формирователь контрольных разрядов, регистр адреса, блок управления, блок контроля, блок коррекции и выходной регистр числа, один выход которого подключен к первым входам блока коррекции и блока контроля, другой выход - к второму входу блока контроля, первый выход которого соединен с вторым входом блока коррекции, выход которого является информационны.м выходом устройства и подключен к первому входу коммутатора записи, второй вход которого является информационным входом устройства, а выход подключен к входу входного регистра числа, выход которого соединен с входом формирователя контрольных разрядов, входы накопителя соединены с выходами регистра адреса, входного регистра числа и формирователя контрольных разрядов, а выход накопителя подключен к входу выходного регистра числа, выходы с первого по пятый блока управления соединены соответствен5 но с управляющими входами регистра адреса, входного регистра числа, накопителя, выходного регистра числа и блока контроля, второй выход которого подключен к первому входу блока управления, входы которого с второго по четвертый являются соответственно входами чтения, записи и синхронизации устройства, введены коммутатор адреса, формирователь контрольного адреса, элемент И и формирователь сигнала паузы, входы которого подключены к входам чтения и за5 ниси устройства, а выход соединен с пятым входом блока управления, управляющими входами коммутатора записи, коммутатора адреса и первым входом элемента И, второй вход которого подключен к шестому выходу блока управления, третий вход - к

второму выходу блока контроля, а выход элемента И соединен с входом формирователя контрольного адреса, выход которого подключен к одному из входов коммутатора адреса, другой вход которого является адрес5 ным входом устройства, а вы.ход коммутатора адреса соединен с входом регистра адреса.

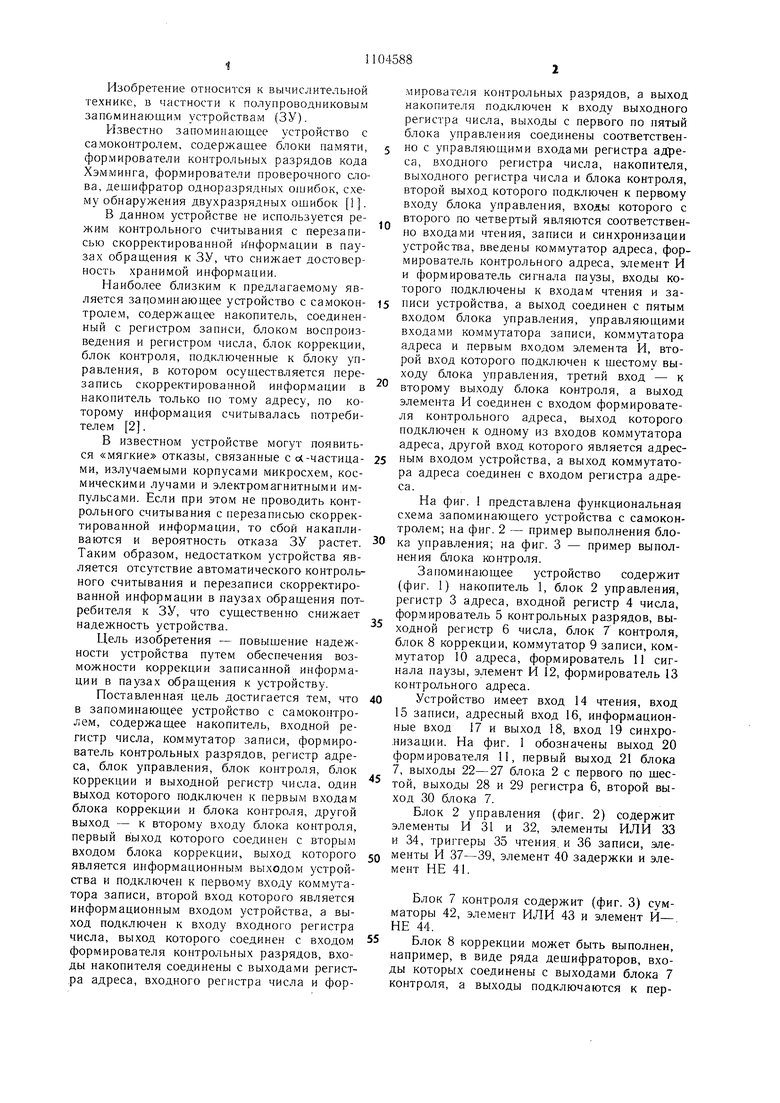

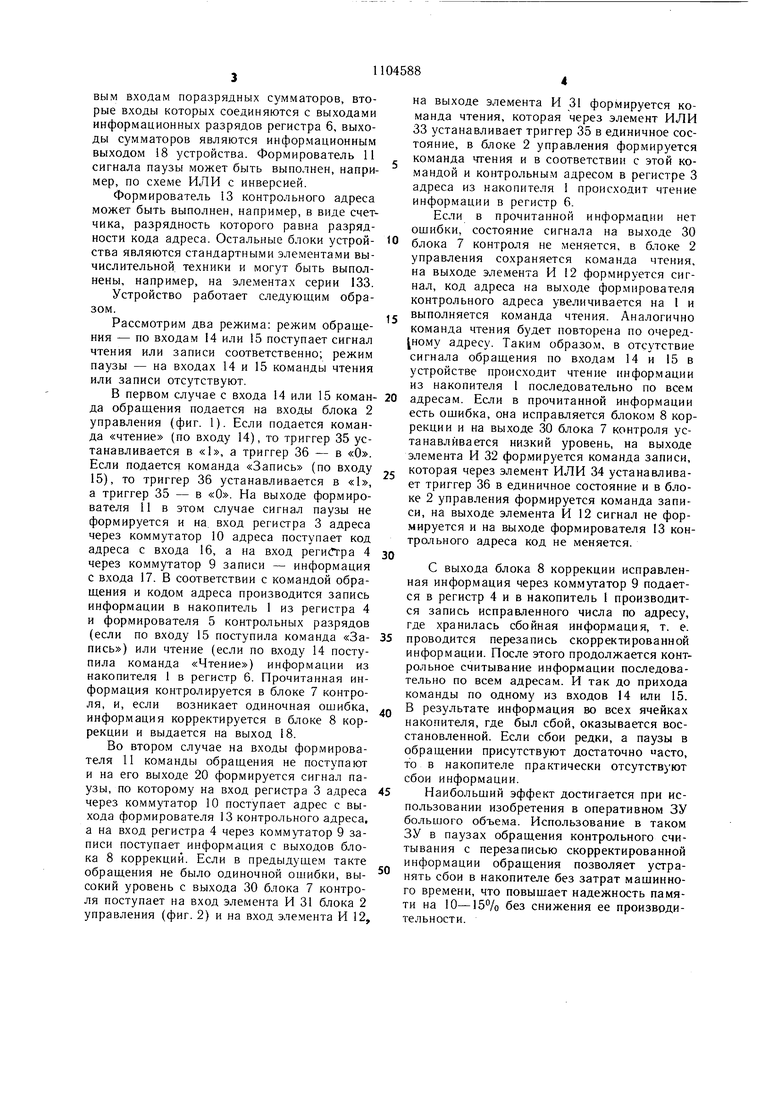

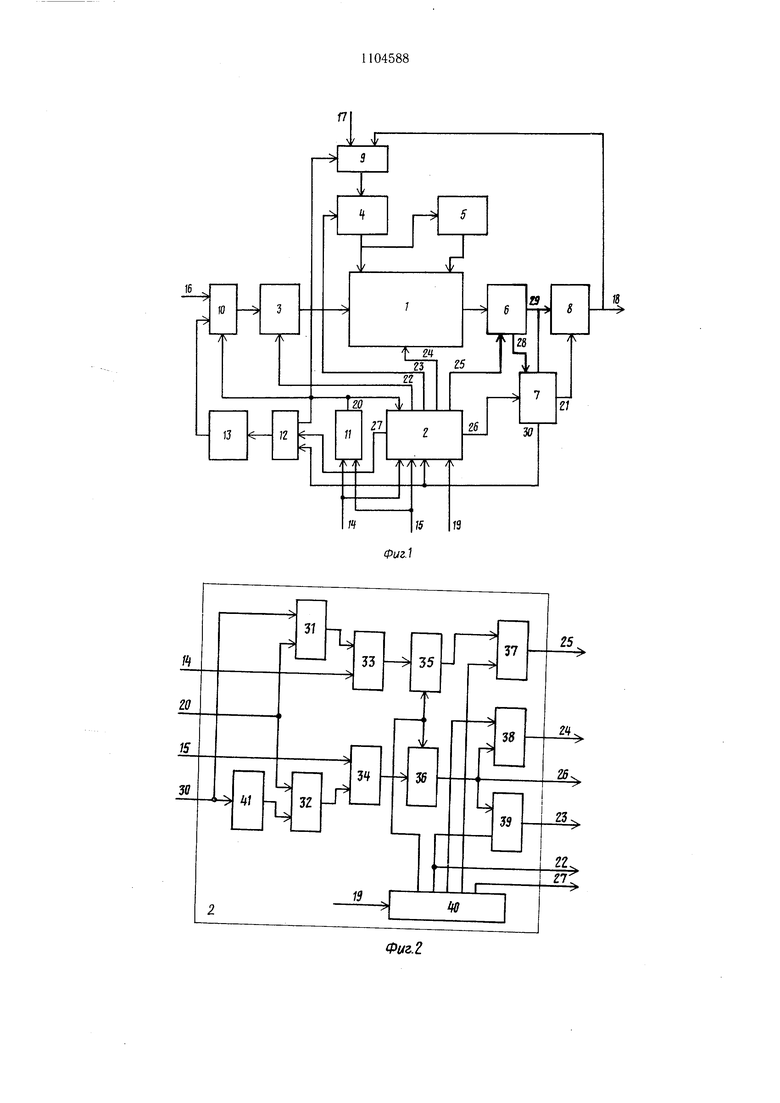

На фиг. 1 представлена функциональная схема запоминающего устройства с самоконтролем; на фиг. 2 - пример выполнения бло0 ка управления; на фиг. 3 - пример выполнения блока контроля.

Запоминающее устройство содержит (фиг. 1) накопитель 1, блок 2 управления, регистр 3 адреса, входной регистр 4 числа, формирователь 5 контрольных разрядов, выходной регистр 6 числа, блок 7 контроля, блок 8 коррекции, ком.мутатор 9 записи, коммутатор 10 адреса, формирователь 11 сигнала паузы, элемент И 12, формирователь 13 контрольного адреса.

Устройство имеет вход 14 чтения, вход 15 записи, адресный вход 16, информационные вход 17 и выход 18, вход 19 синхро.низации. На фиг. 1 обозначены выход 20 формирователя 11, первый выход 21 блока 7, выходы 22-27 блока 2 с первого по щес той, выходы 28 и 29 регистра 6, второй выход 30 блока 7.

Блок 2 управления (фиг. 2) содержит элементы И 31 и 32, элементы ИЛИ 33 и 34, триггеры 35 чтения, и 36 записи, элеQ менты И 37-39, элемент 40 задержки и элемент НЕ 41.

Блок 7 контроля содержит (фиг. 3) сумматоры 42, элемент ИЛИ 43 и элемент И- НЕ 44.

5 Блок 8 коррекции может быть выполнен, например, в виде ряда дешифраторов, входы которых соединены с выходами блока 7 контроля, а выходы подключаются к первым входам поразрядных сумматоров, вторые входы которых соединяются с выходами информационных разрядов регистра 6, выходы сумматоров являются информационным выходом 18 устройства. Формирователь 11 сигнала паузы может быть выполнен, например, по схеме ИЛИ с инверсией.

Формирователь 13 контрольного адреса может быть выполнен, например, в виде счетчика, разрядность которого равна разрядности кода адреса. Остальные блоки устройства являются стандартными элементами вычислительной техники и могут быть выполнены, например, на элементах серии 133.

Устройство работает следующим образом.

Рассмотрим два режима: режим обращения - по входам 14 или 15 поступает сигнал чтения или записи соответственно; режим паузы - на входах 14 и 15 команды чтения или записи отсутствуют.

В первом случае с входа 14 или 15 команда обращения подается на входы блока 2 управления (фиг. 1). Если подается команда «чтение (по входу 14), то триггер 35 устанавливается в «1, а триггер 36 - в «О. Если подается команда «Запись (по входу 15), то триггер 36 устанавливается в «1, а триггер 35 - в «О. На выходе формирователя 11 в этом с,пучае сигнал паузы не формируется и на вход регистра 3 адреса через коммутатор 10 адреса поступает код адреса с входа 16, а на вход региЛра 4 через коммутатор 9 записи - информация с входа 17. В соответствии с командой обращения и кодом адреса производится запись информации в накопитель 1 из регистра 4 и формирователя 5 контрольных разрядов (если по входу 15 поступила команда «Запись) или чтение (если по входу 14 поступила команда «Чтение) информации из накопителя 1 в регистр 6. Прочитанная информация контролируется в блоке 7 контроля, и, если возникает одиночная ошибка, информация корректируется в блоке 8 коррекции и выдается на выход 18.

Во втором случае на входы формирователя 11 команды обращения не поступают и на его выходе 20 формируется сигнал паузы, по которому на вход регистра 3 адреса через коммутатор 10 поступает адрес с выхода формирователя 13 контрольного адреса, а на вход регистра 4 через коммутатор 9 записи поступает информация с выходов блока 8 коррекций. Если в предыдущем такте обращения не было одиночной ошибки, высокий уровень с выхода 30 блока 7 контроля поступает на вход элемента И 31 блока 2 управления (фиг. 2) и на вход эле.мента И 12,

на выходе элемента И 31 формируется команда чтения, которая через элемент ИЛИ 33 устанавливает триггер 35 в единичное состояние, в блоке 2 управления формируется команда чтения и в соответствии с этой командой и контрольным адресом в регистре 3 адреса из накопителя 1 происходит чтение информации в регистр 6.

Если в прочитанной информации нет ощибки, состояние сигнала на выходе 30 блока 7 контроля не меняется, в блоке 2 управления сохраняется команда чтения, на выходе элемента И 12 формируется сигнал, код адреса на выходе фор.мирователя контрольного адреса увеличивается на 1 и выполняется команда чтения. Аналогично команда чтения будет повторена по очеред ному адресу. Таким образом, в отсутствие сигнала обращения по входам 14 и 15 в устройстве происходит чтение информации из накопителя 1 последовательно по всем адресам. Если в прочитанной информации есть ощибка, она исправляется блоком 8 коррекции и на выходе 30 блока 7 контроля устанавливается низкий уровень, на выходе элемента И 32 формируется команда записи, которая через элемент ИЛИ 34 устанавливает триггер 36 в единичное состояние и в блоке 2 управления формируется команда записи, на выходе элемента И 12 сигнал не формируется и на выходе формирователя 13 контрольного адреса код не меняется.

С выхода блока 8 коррекции исправленная информация через коммутатор 9 подается в регистр 4 и в накопите пь I производится запись исправленного числа по адресу, где хранилась сбойная информация, т. е. проводится перезапись скорректированной информации. После этого продолжается контрольное считывание информации последовательно по всем адресам. И так до прихода команды по одному из входов 14 или 15. В результате информация во всех ячейках накопителя, где был сбой, оказывается восстановленной. Если сбои редки, а паузы в обращении присутствуют достаточно «асто, то в накопителе практически отсутствуют сбои информации.

Наибольший эффект достигается при использовании изобретения в оперативном ЗУ большого объема. Использование в таком ЗУ в паузах обращения контрольного считывания с перезаписью скорректированной информации обращения позволяет устранять сбои в накопителе без затрат машинного времени, что повышает надежность памяти на 10-15% без снижения ее производительности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875474A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Запоминающее устройство | 1983 |

|

SU1246137A1 |

| Запоминающее устройство с автономным контролем | 1975 |

|

SU690567A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее накопитель, входной регистр числа, коммутатор записи, формирователь контрольных разрядов, регистр адреса, блок управления, блок контроля, блок коррекции и выходной регистр числа, один выход которого подключен к первым входам блока коррекции и блока контроля, другой выход - к второму входу блока контроля, первый выход которого соединен с вторым входом блока коррекции, выход которого является информационным выходом устройства и подключен к первому входу коммутатора записи, второй вход которого является информационным входом устройства, а выход подключен к входу входного регистра числа, выход которого соединен с входом формирователя контрольных разрядов, входы накопителя соединены с выходами регистра адреса, входного регистра числа и формирователя контрольных разрядов, а выход накопителя подключен к входу выходного регистра числа, выходы с первого по пятый блока управления соединены соответственно с управляющими входами регистра адреса, входного регистра числа, накопителя, выходного регистра числа и блока контроля, второй выход которого подключен к первому входу блока управления, входы которого со второго по четвертый являются соответственно входами чтения, записи и синхронизации устройства, отличающееся тем, что, с целью повыщения надежности устройства, в него введены коммутатор адреса, формирователь контрольного адреса, элемент И и формирователь сигнала паузы, входы которого подключены к входам чтения и записи устройства, а выход соединен с пятым входом бло(Л ка управления, управляющими входами коммутатора записи, коммутатора адреса и первым входом элемента И, второй вход которого подключен к щестому выходу блока управления, третий вход - к второму выходу блока контроля, а выход элемента И соединен с входом формирователя контрольного адреса, выход которого подключен к одному из входов коммутатора адреса, другой 4 СЛ вход которого является адресным входом устройства, а выход коммутатора адреса соеСХ) динен с входом регистра адреса. 00

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3573728, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875474A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-07-23—Публикация

1983-04-13—Подача