Изобретение относится к вычислительной технике и может быть использовано в системах управления, преимущественно в аналого-цифровых преобразователях, для преобразования непрерывно меняющегося во времени аналогового сигнала в цифровой код.

Цель изобретения - повышение стабильности и точности компаратора.

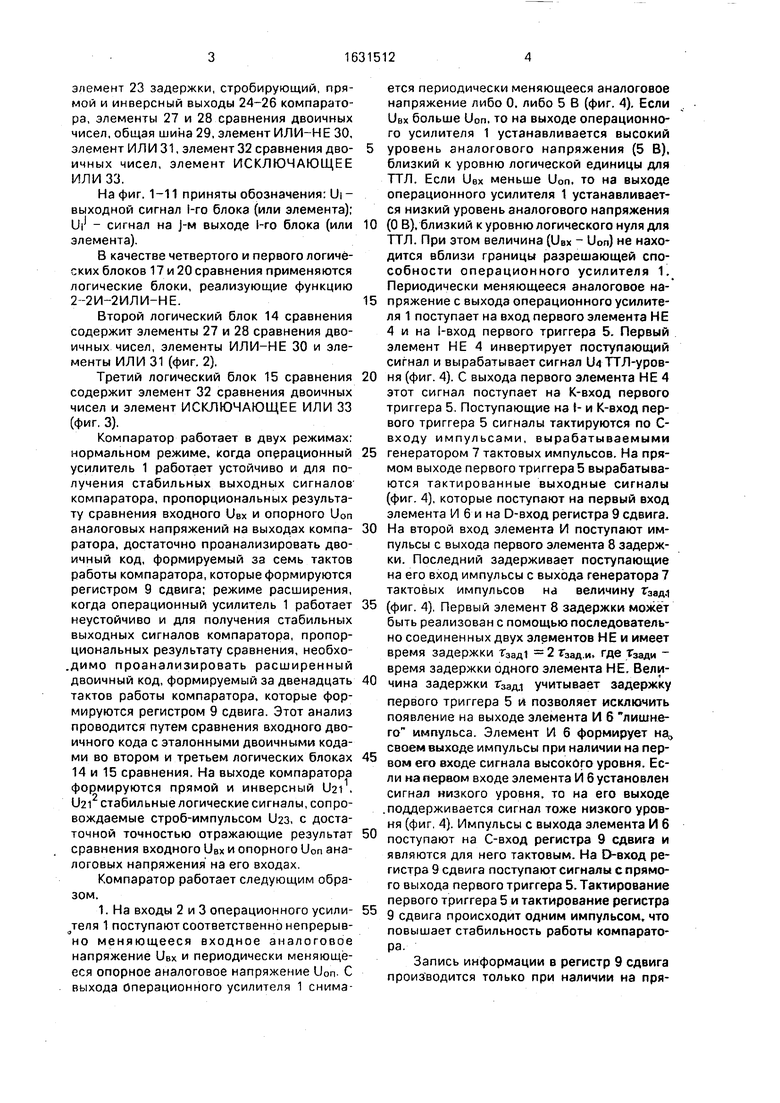

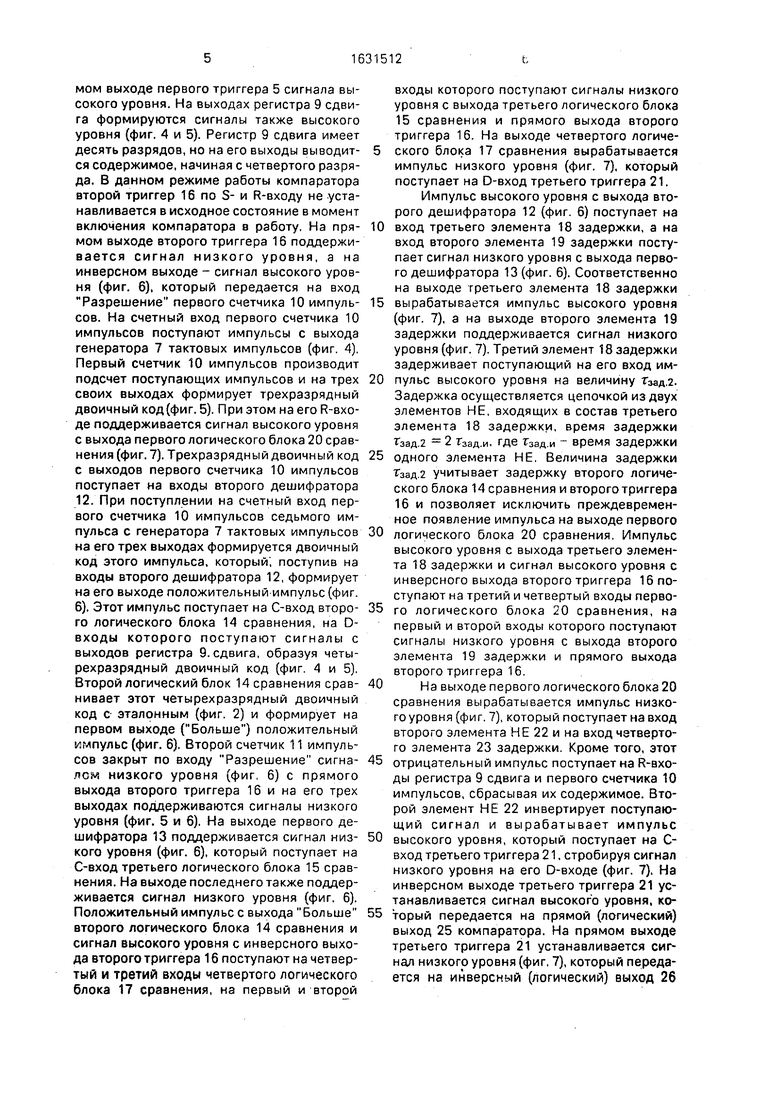

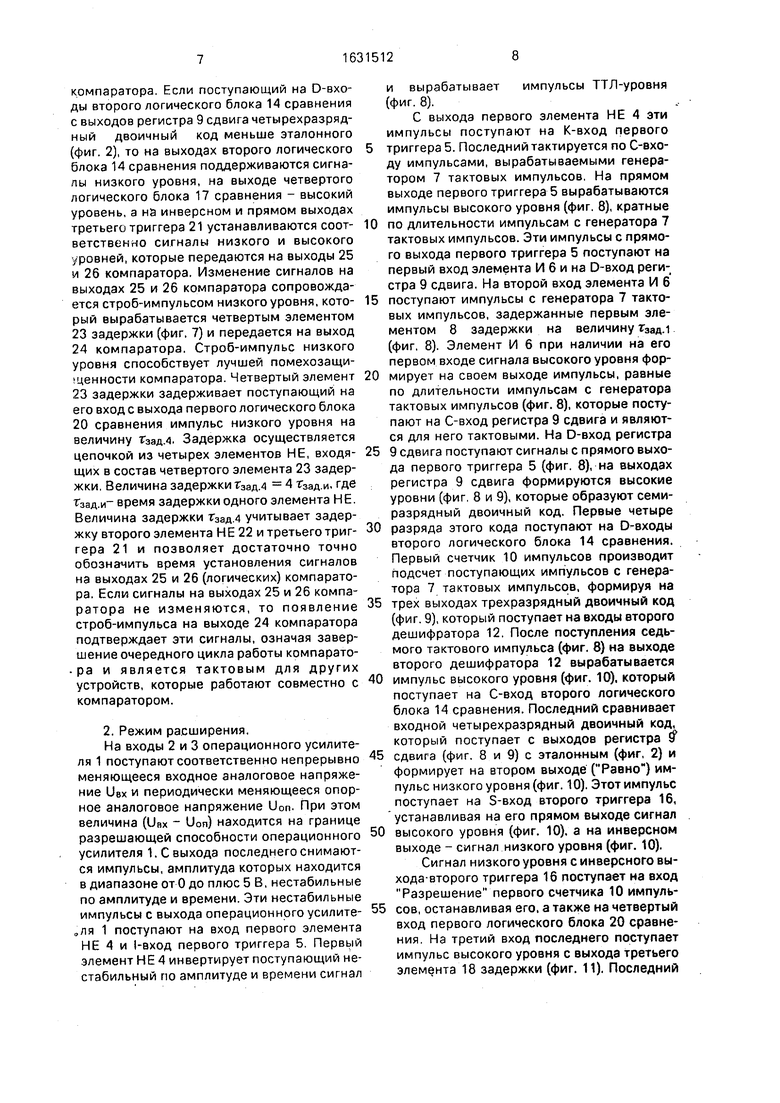

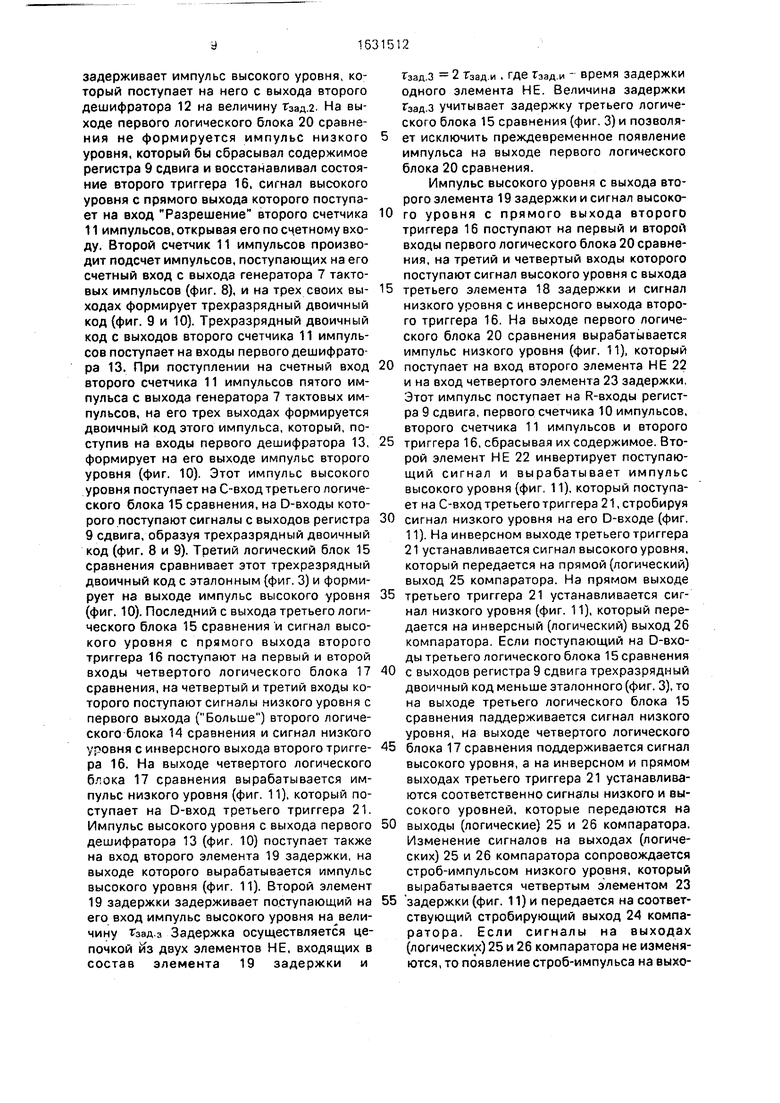

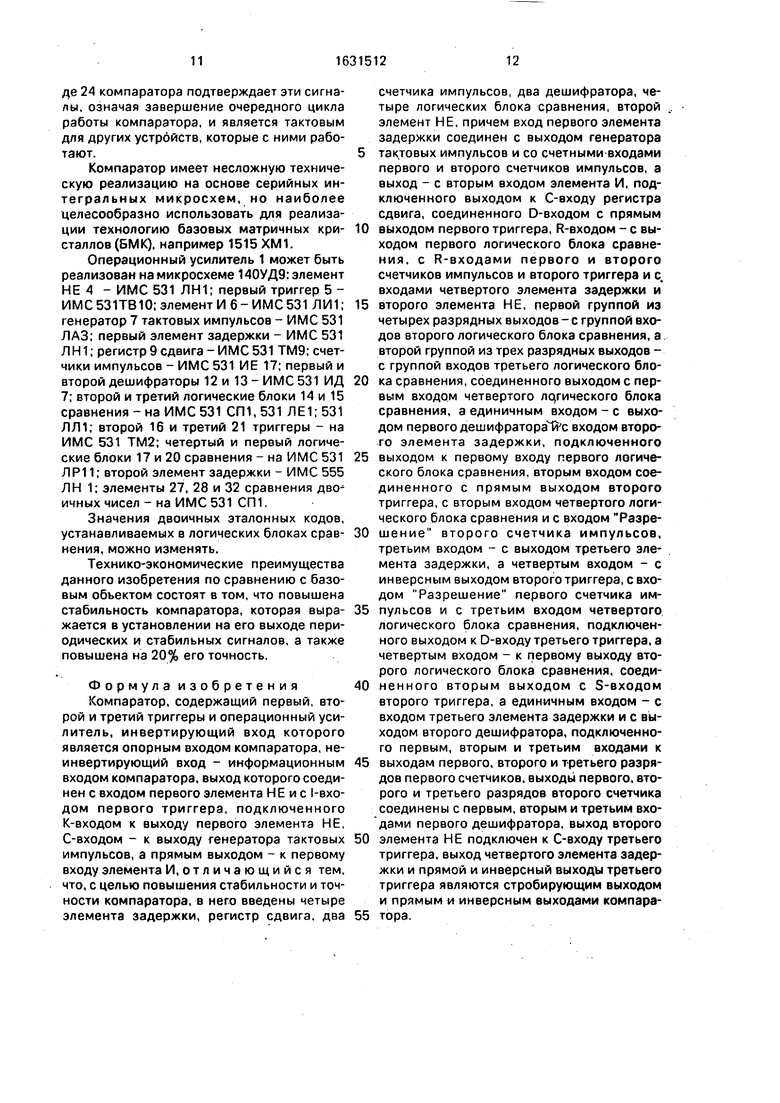

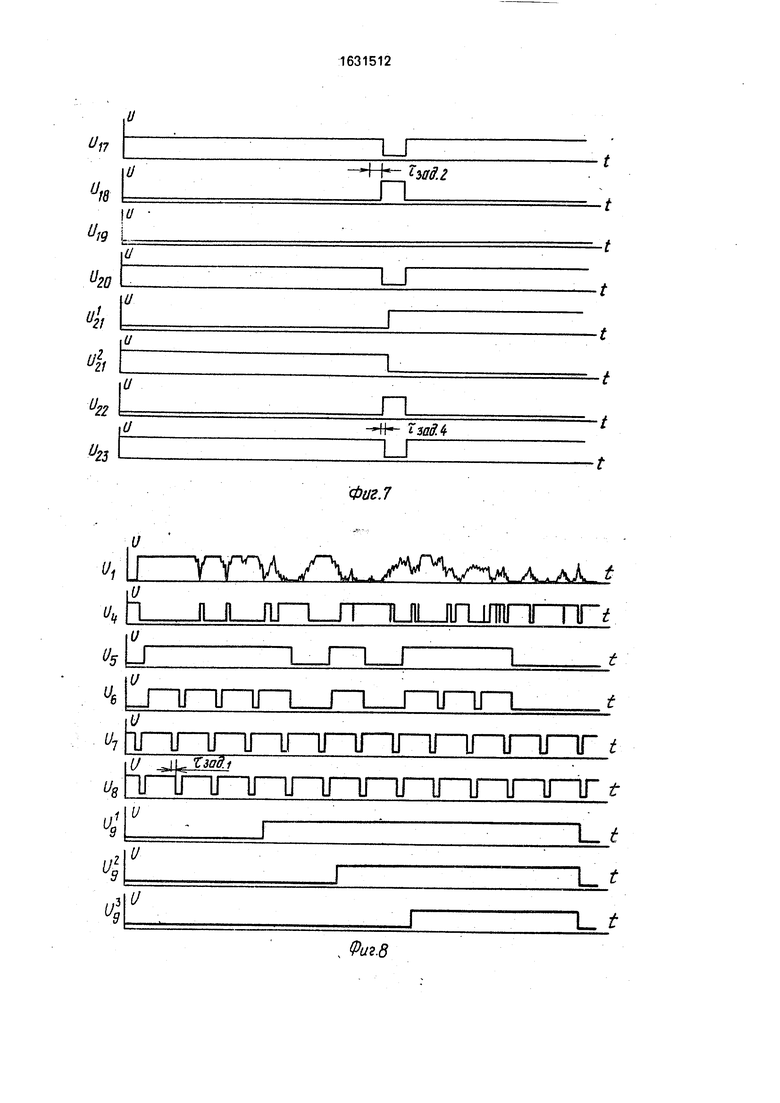

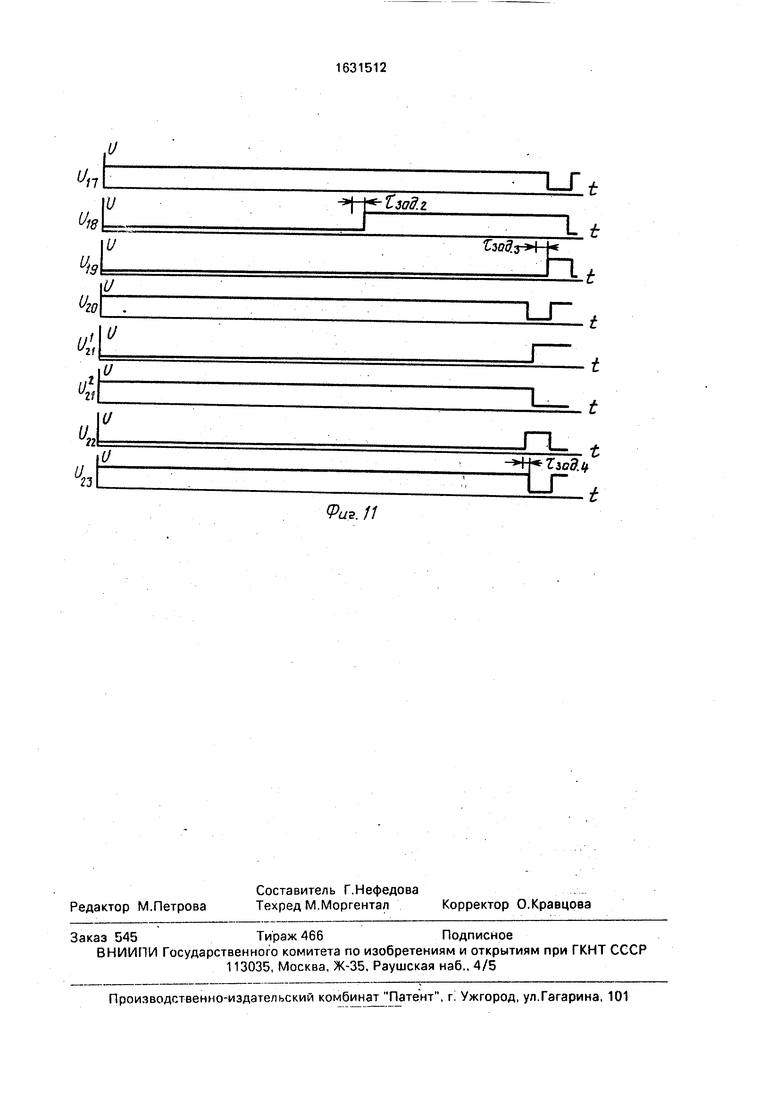

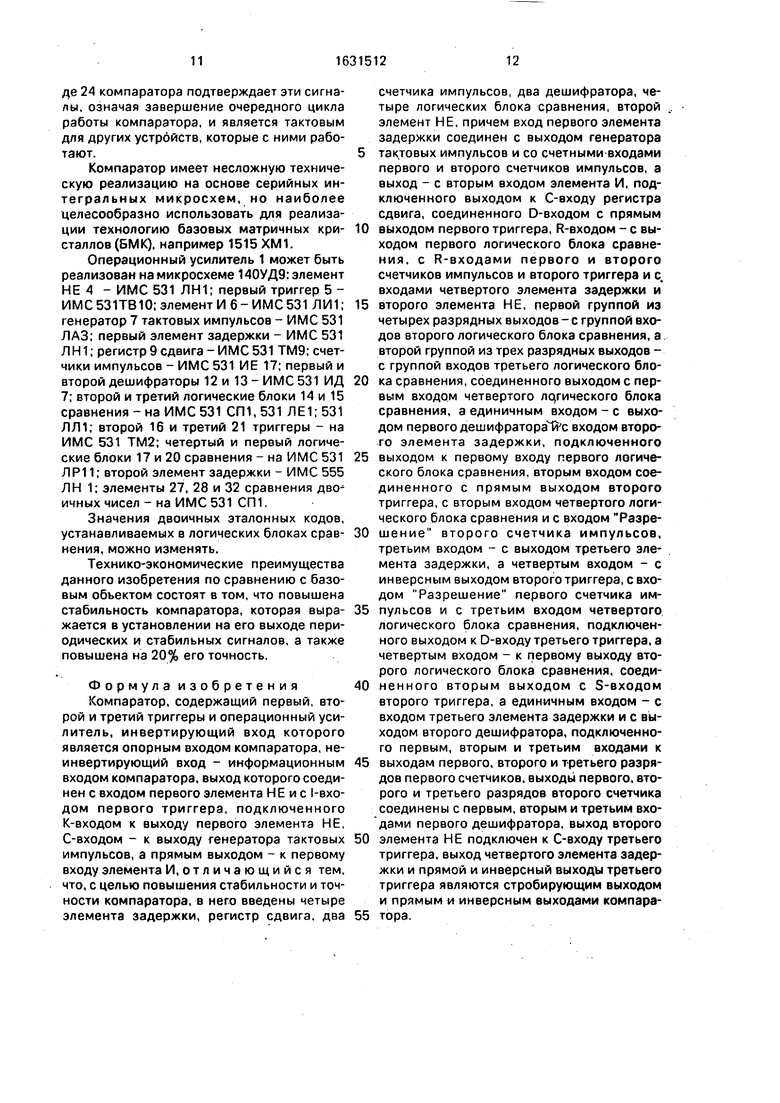

На фиг. 1 изображена блок-схема; на фиг. 2 - функциональная схема второго логического блока сравнения и его таблица истинности; на фиг. 3 - функциональная схема третьего логического блока сравнения и его таблица истинности; на фиг. 4-7 - временные диаграммы компаратора для нормального режима работы; на фиг. 8-11 - то же, для режима расширения.

Устройство содержит операционный усилитель 1, информационный вход 2 компаратора, опорный вход 3 компаратора, первый элемент НЕ 4, первый триггер 5, элемент И 6, генератор 7 тактовых импульсов, первый элемент 8 задержки, регистр 9 сдвига, первый и второй счетчики 10 и 11 импульсов, второй и первый дешифраторы .12 и 13, второй и третий логические блоки 14 и 15 сравнения, второй триггер 16, четвертый логический блок 17 сравнения, третий и второй элементы 18 и 19 задержки, первый логический блок 20 сравнения, третий триггер 21. второй элемент НЕ 22. четвертый

о

CJ

ел ю

элемент 23 задержки, стробирующий, прямой и инверсный выходы 24-26 компаратора, элементы 27 и 28 сравнения двоичных чисел, общая шина 29, элементИЛИ-НЕ 30, элемент ИЛИ 31, элемент 32 сравнения дво- ичных чисел, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 33.

На фиг. 1-11 приняты обозначения: Ui - выходной сигнал 1-го блока (или элемента); Ui - сигнал на j-м выходе 1-го блока (или элемента).

В качестве четвертого и первого логических блоков 17 и 20 сравнения применяются логические блоки, реализующие функцию 2-2И-2ИЛИ-НЕ.

Второй логический блок 14 сравнения содержит элементы 27 и 28 сравнения двоичных чисел, элементы ИЛИ-НЕ 30 и элементы ИЛИ 31 (фиг. 2).

Третий логический блок 15 сравнения содержит элемент 32 сравнения двоичных чисел и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 33 (фиг. 3).

Компаратор работает в двух режимах: нормальном режиме, когда операционный усилитель 1 работает устойчиво и для получения стабильных выходных сигналов компаратора, пропорциональных результату сравнения входного UBX и опорного Uon аналоговых напряжений на выходах компа- ратора, достаточно проанализировать двоичный код, формируемый за семь тактов работы компаратора, которые формируются регистром 9 сдвига; режиме расширения, когда операционный усилитель 1 работает неустойчиво и для получения стабильных выходных сигналов компаратора, пропорциональных результату сравнения, необхо- .димо проанализировать расширенный двоичный код, формируемый за двенадцать тактов работы компаратора, которые формируются регистром 9 сдвига. Этот анализ проводится путем сравнения входного двоичного кода с эталонными двоичными кодами во втором и третьем логических блоках 14 и 15 сравнения. На выходе компаратора формируются прямой и инверсный U21 , U21 стабильные логические сигналы, сопровождаемые строб-импульсом U23, с достаточной точностью отражающие результат сравнения входного UBx и опорного Uon аналоговых напряжения на его входах.

Компаратор работает следующим образом.

1. На входы 2 и 3 операционного усили- лтеля 1 поступают соответственно непрерывно меняющееся входное аналоговое напряжение UBx и периодически меняющееся опорное аналоговое напряжение U0n- С выхода Операционного усилителя 1 снимается периодически меняющееся аналоговое напряжение либо 0. либо 5 В (фиг. 4). Если UBX больше Uon. то на выходе операционного усилителя 1 устанавливается высокий уровень аналогового напряжения (5 В), близкий к уровню логической единицы для ТТЛ. Если Uex меньше Uon, то на выходе операционного усилителя 1 устанавливается низкий уровень аналогового напряжения (О В), близкий к уровню логического нуля для ТТЛ. При этом величина (UBx - Uon) не находится вблизи границы разрешающей способности операционного усилителя 1. Периодически меняющееся аналоговое напряжение с выхода операционного усилителя 1 поступает на вход первого элемента НЕ 4 и на 1-вход первого триггера 5. Первый элемент НЕ 4 инвертирует поступающий сигнал и вырабатывает сигнал U4 ТТЛ-уровня (фиг. 4). С выхода первого элемента НЕ 4 этот сигнал поступает на К-вход первого триггера 5. Поступающие на I- и К-вход первого триггера 5 сигналы тактируются по С- входу импульсами, вырабатываемыми генератором 7 тактовых импульсов. На прямом выходе первого триггера 5 вырабатываются тактированные выходные сигналы (фиг. 4), которые поступают на первый вход элемента И 6 и на D-вход регистра 9 сдвига. На второй вход элемента И поступают импульсы с выхода первого элемента 8 задержки. Последний задерживает поступающие на его вход импульсы с выхода генератора 7 тактовых импульсов на величину Тэад.1 (фиг. 4), Первый элемент 8 задержки может быть реализован с помощью последовательно соединенных двух элементов НЕ и имеет время задержки тзад1 2 гзад.и, где тзади - время задержки одного элемента НЕ, Величина задержки тзам учитывает задержку первого триггера 5 и позволяет исключить появление на выходе элемента И 6 лишнего импульса. Элемент И 6 формирует на„ своем выходе импульсы при наличии на первом его входе сигнала высокого уровня. Если на первом входе элемента И б установлен сигнал низкого уровня, то на его выходе .поддерживается сигнал тоже низкого уровня (фиг. 4). Импульсы с выхода элемента И 6 поступают на С-вход регистра 9 сдвига и являются для него тактовым. На D-вход регистра 9 сдвига поступают сигналы с прямого выхода первого триггера 5. Тактирование первого триггера 5 и тактирование регистра 9 сдвига происходит одним импульсом, что повышает стабильность работы компаратора.

Запись информации в регистр 9 сдвига производится только при наличии на прямом выходе первого триггера 5 сигнала высокого уровня. На выходах регистра 9 сдвига формируются сигналы также высокого уровня (фиг. 4 и 5). Регистр 9 сдвига имеет десять разрядов, но на его выходы выводит- ся содержимое, начиная с четвертого разряда. В данном режиме работы компаратора второй триггер 16 по S- и R-входу не устанавливается в исходное состояние в момент включения компаратора в работу. На пря- мом выходе второго триггера 16 поддерживается сигнал низкого уровня, а на инверсном выходе - сигнал высокого уровня (фиг. 6), который передается на вход Разрешение первого счетчика 10 импуль- сов. На счетный вход первого счетчика 10 импульсов поступают импульсы с выхода генератора 7 тактовых импульсов (фиг. 4), Первый счетчик 10 импульсов производит подсчет поступающих импульсов и на трех своих выходах формирует трехразрядный двоичный код(фиг. 5). При этом на его R-вхо- де поддерживается сигнал высокого уровня с выхода первого логического блока 20 сравнения (фиг. 7). Трехразрядный двоичный код с выходов первого счетчика 10 импульсов поступает на входы второго дешифратора 12. При поступлении на счетный вход первого счетчика 10 импульсов седьмого импульса с генератора 7 тактовых импульсов на его трех выходах формируется двоичный код этого импульса, который, поступив на входы второго дешифратора 12, формирует на его выходе положительный импульс (фиг. 6). Этот импульс поступает на С-вход второ- го логического блока 14 сравнения, на D- входы которого поступают сигналы с выходов регистра 9.сдвига, образуя четырехразрядный двоичный код (фиг. 4 и 5). Второй логический блок 14 сравнения срав- нивает этот четырехразрядный двоичный код с эталонным (фиг. 2) и формирует на первом выходе (Больше) положительный /мпульс (фиг. 6), Второй счетчик 11 импульсов закрыт по входу Разрешение сигна- лсм низкого уровня (фиг. 6) с прямого выхода второго триггера 16 и на его трех выходах поддерживаются сигналы низкого уровня (фиг. 5 и 6). На выходе первого дешифратора 13 поддерживается сигнал низ- кого уровня (фиг. 6), который поступает на С-вход третьего логического блока 15 сравнения. На выходе последнего также поддерживается сигнал низкого уровня (фиг. 6). Положительный импульс с выхода Больше второго логического блока 14 сравнения и сигнал высокого уровня с инверсного выхода второго триггера 16 поступают на четвертый и третий входы четвертого логического блока 17 сравнения, на первый и второй

входы которого поступают сигналы низкого уровня с выхода третьего логического блока

15сравнения и прямого выхода второго триггера 16. На выходе четвертого логического блока 17 сравнения вырабатывается импульс низкого уровня (фиг. 7), который поступает на D-вход третьего триггера 21.

Импульс высокого уровня с выхода второго дешифратора 12 (фиг. 6) поступает на вход третьего элемента 18 задержки, а на вход второго элемента 19 задержки поступает сигнал низкого уровня с выхода первого дешифратора 13 (фиг. 6). Соответственно на выходе третьего элемента 18 задержки вырабатывается импульс высокого уровня (фиг. 7), а на выходе второго элемента 19 задержки поддерживается сигнал низкого уровня (фиг. 7). Третий элемент 18 задержки задерживает поступающий на его вход импульс высокого уровня на величину Тзад.2. Задержка осуществляется цепочкой из двух элементов НЕ, входящих в состав третьего элемента 18 задержки, время задержки Тзад Тзад и, где г3ад и время задержки одного элемента НЕ. Величина задержки Тзад2 учитывает задержку второго логического блока 14 сравнения и второго триггера

16и позволяет исключить преждевременное появление импульса на выходе первого логического блока 20 сравнения. Импульс высокого уровня с выхода третьего элемента 18 задержки и сигнал высокого уровня с инверсного выхода второго триггера 16 поступают на третий и четвертый входы первого логического блока 20 сравнения, на первый и второй входы которого поступают сигналы низкого уровня с выхода второго элемента 19 задержки и прямого выхода второго триггера 16.

На выходе первого логического блока 20 сравнения вырабатывается импульс низкого уровня (фиг. 7), который поступает на вход второго элемента НЕ 22 и на вход четвертого элемента 23 задержки. Кроме того, этот отрицательный импульс поступает на R-вхо- ды регистра 9 сдвига и первого счетчика 10 импульсов, сбрасывая их содержимое. Второй элемент НЕ 22 инвертирует поступающий сигнал и вырабатывает импульс высокого уровня, который поступает на С- вход третьего триггера 21, стробируя сигнал низкого уровня на его D-входе (фиг. 7). На инверсном выходе третьего триггера 21 устанавливается сигнал высокого уровня, который передается на прямой (логический) выход 25 компаратора. На прямом выходе третьего триггера 21 устанавливается сигнал низкого уровня (фиг, 7), который передается на инверсный (логический) выход 26

компаратора. Если поступающий на D-вхо- ды второго логического блока 14 сравнения с выходов регистра 9 сдвига четырехразрядный двоичный код меньше эталонного (фиг. 2), то на выходах второго логического блока 14 сравнения поддерживаются сигналы низкого уровня, на выходе четвертого логического блока 17 сравнения - высокий уровень, а на инверсном и прямом выходах третьего триггера 21 устанавливаются соответственно сигналы низкого и высокого /ровней, которые передаются на выходы 25 и 26 компаратора. Изменение сигналов на выходах 25 и 26 компаратора сопровождается строб-импульсом низкого уровня, который вырабатывается четвертым элементом

23задержки (фиг. 7) и передается на выход

24компаратора. Строб-импульс низкого уровня способствует лучшей помехозащищенности компаратора. Четвертый элемент 23 задержки задерживает поступающий на его вход с выхода первого логического блока 20 сравнения импульс низкого уровня на величину Тзад.4. Задержка осуществляется цепочкой из четырех элементов НЕ, входящих в состав четвертого элемента 23 задержки. Величина задержки тзад.4 4 тзад и, где Тзад.и время задержки одного элемента НЕ. Величина задержки тзад4 учитывает задержку второго элемента НЕ 22 и третьего триггера 21 и позволяет достаточно точно обозначить время установления сигналов на выходах 25 и 26 (логических) компаратора. Если сигналы на выходах 25 и 26 компаратора не изменяются, то появление строб-импульса на выходе 24 компаратора подтверждает эти сигналы, означая завершение очередного цикла работы компаратора и является тактовым для других устройств, которые работают совместно с компаратором.

2. Режим расширения.

На входы 2 и 3 операционного усилителя 1 поступают соответственно непрерывно меняющееся входное аналоговое напряжение DBX и периодически меняющееся опорное аналоговое напряжение Don. При этом величина (UBx - Uon) находится на границе разрешающей способности операционного усилителя 1. С выхода последнего снимаются импульсы, амплитуда которых находится в диапазоне от 0 до плюс 5 В, нестабильные по амплитуде и времени. Эти нестабильные импульсы с выхода операционногоусилите- „ля 1 поступают на вход первого элемента НЕ 4 и 1-вход первого триггера 5. Первый элемент НЕ 4 инвертирует поступающий нестабильный по амплитуде и времени сигнал

и вырабатывает импульсы ТТЛ-уровня (фиг. 8).

С выхода первого элемента НЕ 4 эти импульсы поступают на К-вход первого

триггера 5. Последний тактируется по С-вхо- ду импульсами, вырабатываемыми генератором 7 тактовых импульсов, На прямом выходе первого триггера 5 вырабатываются импульсы высокого уровня (фиг. 8), кратные

по длительности импульсам с генератора 7 тактовых импульсов. Эти импульсы с прямого выхода первого триггера 5 поступают на первый вход элемента И 6 и на D-вход регистра 9 сдвига. На второй вход элемента И 6

поступают импульсы с генератора 7 тактовых импульсов, задержанные первым элементом 8 задержки на величину тзад.1 (фиг, 8). Элемент И 6 при наличии на его первом входе сигнала высокого уровня формирует на своем выходе импульсы, равные по длительности импульсам с генератора тактовых импульсов (фиг. 8), которые поступают на С-вход регистра 9 сдвига и являются для него тактовыми. На D-вход регистра

9 сдвига поступают сигналы с прямого выхода первого триггера 5 (фиг. 8), на выходах регистра 9 сдвига формируются высокие уровни (фиг. 8 и 9), которые образуют семиразрядный двоичный код. Первые четыре

разряда этого кода поступают на D-входы второго логического блока 14 сравнения. Первый счетчик 10 импульсов производит подсчет поступающих импульсов с генератора 7 тактовых импульсов, формируя на

трех выходах трехразрядный двоичный код (фиг. 9), который поступает на входы второго дешифратора 12. После поступления седьмого тактового импульса (фиг. 8) на выходе второго дешифратора 12 вырабатывается

импульс высокого уровня (фиг. 10), который поступает на С-вход второго логического блока 14 сравнения. Последний сравнивает входной четырехразрядный двоичный код, который поступает с выходов регистра S

сдвига (фиг. 8 и 9) с эталонным (фиг, 2) и формирует на втором выходе (Равно) импульс низкого уровня (фиг. 10), Этот импульс поступает на S-вход второго триггера 16, устанавливая на его прямом выходе сигнал

высокого уровня (фиг. 10). а на инверсном выходе - сигнал низкого уровня (фиг. 10).

Сигнал низкого уровня с инверсного выхода-второго триггера 16 поступает на вход Разрешение первого счетчика 10 импульсов, останавливая его. а также на четвертый вход первого логического блока 20 сравнения. На третий вход последнего поступает импульс высокого уровня с выхода третьего элемента 18 задержки (фиг. 11). Последний

задерживает импульс высокого уровня, который поступает на него с выхода второго дешифратора 12 на величину Т3ад.2. На выходе первого логического блока 20 сравнения не формируется импульс низкого уровня, который бы сбрасывал содержимое регистра 9 сдвига и восстанавливал состояние второго триггера 16, сигнал высокого уровня с прямого выхода которого поступает на вход Разрешение второго счетчика 11 импульсов, открывая его по счетному входу. Второй счетчик 11 импульсов производит подсчет импульсов, поступающих на его счетный вход с выхода генератора 7 тактовых импульсов (фиг. 8), и на трех своих выходах формирует трехразрядный двоичный код (фиг. 9 и 10). Трехразрядный двоичный код с выходов второго счетчика 11 импульсов поступает на входы первого дешифратора 13. При поступлении на счетный вход второго счетчика 11 импульсов пятого импульса с выхода генератора 7 тактовых импульсов, на его трех выходах формируется двоичный код этого импульса, который, поступив на входы первого дешифратора 13, формирует на его выходе импульс второго уровня (фиг. 10). Этот импульс высокого уровня поступает на С-вход третьего логического блока 15 сравнения, на D-входы которого поступают сигналы с выходов регистра 9 сдвига, образуя трехразрядный двоичный код (фиг. 8 и 9). Третий логический блок 15 сравнения сравнивает этот трехразрядный двоичный код с эталонным (фиг, 3) и формирует на выходе импульс высокого уровня (фиг. 10). Последний с выхода третьего логического блока 15 сравнения и сигнал высокого уровня с прямого выхода второго триггера 16 поступают на первый и второй входы четвертого логического блока 17 сравнения, на четвертый и третий входы которого поступают сигналы низкого уровня с первого выхода (Больше) второго логического блока 14 сравнения и сигнал низкгого уровня с инверсного выхода второго триггера 16. На выходе четвертого логического блока 17 сравнения вырабатывается импульс низкого уровня (фиг. 11), который поступает на D-вход третьего триггера 21. Импульс высокого уровня с выхода первого дешифратора 13 (фиг 10) поступает также на вход второго элемента 19 задержки, на выходе которого вырабатывается импульс высокого уровня (фиг. 11). Второй элемент 19 задержки задерживает поступающий на его вход импульс высокого уровня на вели- чину Тзад з Задержка осуществляется цепочкой из двух элементов НЕ, входящих в состав элемента 19 задержки и

Гзад Тзад и . где тэад и - время задержки одного элемента НЕ. Величина задержки ГзадЗ учитывает задержку третьего логического блока 15 сравнения (фиг. 3) и позволяет исключить преждевременное появление импульса на выходе первого логического блока 20 сравнения.

Импульс высокого уровня с выхода второго элемента 19 задержки и сигнал высокого уровня с прямого выхода второго триггера 16 поступают на первый и второй входы первого логического блока 20 сравнения, на третий и четвертый входы которого поступают сигнал высокого уровня с выхода

третьего элемента 18 задержки и сигнал низкого уровня с инверсного выхода второго триггера 16. На выходе первого логического блока 20 сравнения вырабатывается импульс низкого уровня (фиг, 11), который

поступает на вход второго элемента НЕ 22 и на вход четвертого элемента 23 задержки. Этот импульс поступает на R-входы регистра 9 сдвига, первого счетчика 10 импульсов, второго счетчика 11 импульсов и второго

триггера 16, сбрасывая их содержимое. Второй элемент НЕ 22 инвертирует поступающий сигнал и вырабатывает импульс высокого уровня (фиг, 11), который поступает на С-вход третьего триггера 21, стробируя

сигнал низкого уровня на его D-входе (фиг. 11). На инверсном выходе третьего триггера 21 устанавливается сигнал высокого уровня, который передается на прямой (логический) выход 25 компаратора. На прямом выходе

третьего триггера 21 устанавливается сигнал низкого уровня (фиг. 11), который передается на инверсный (логический) выход 26 компаратора. Если поступающий на D-входы третьего логического блока 15 сравнения

с выходов регистра 9 сдвига трехразрядный двоичный код меньше эталонного (фиг. 3), то на выходе третьего логического блока 15 сравнения паддерживается сигнал низкого уровня, на выходе четвертого логического

блока 17 сравнения поддерживается сигнал высокого уровня, а на инверсном и прямом выходах третьего триггера 21 устанавливаются соответственно сигналы низкого и высокого уровней, которые передаются на

выходы (логические) 25 и 26 компаратора. Изменение сигналов на выходах (логических) 25 и 26 компаратора сопровождается строб-импульсом низкого уровня, который вырабатывается четвертым элементом 23

задержки (фиг. 11) и передается на соответствующий стробирующий выход 24 компаратора. Если сигналы на выходах (логических) 25 и 26 компаратора не изменяются, то появление строб-импульса на выходе 24 компаратора подтверждает эти сигналы, означая завершение очередного цикла работы компаратора, и является тактовым для других устройств, которые с ними работают.

Компаратор имеет несложную техническую реализацию на основе серийных интегральных микросхем, но наиболее целесообразно использовать для реализации технологию базовых матричных кристаллов (БМК). например 1515 ХМ1.

Операционный усилитель 1 может быть реализован на микросхеме 140УД9: элемент НЕ 4 - ИМС 531 ЛН1; первый триггер 5 - ИМС 531ТВ10; элемент И б - ИМС 531 ЛИ1 ; генератор 7 тактовых импульсов - ИМС 531 ЛАЗ; первый элемент задержки - ИМС 531 ЛН1; регистр 9 сдвига-ИМС 531 ТМ9; счетчики импульсов - ИМС 531 ИЕ 17; первый и второй дешифраторы 12 и 13 - ИМС 531 ИД 7; второй и третий логические блоки 14 и 15 сравнения - на ИМС 531 СП1, 531 ЛЕ1; 531 ЛЛ1; второй 16 и третий 21 триггеры - на ИМС 531 ТМ2; четертый и первый логические блоки 17 и 20 сравнения - на ИМС 531 ЛР11; второй элемент задержки - ИМС 555 ЛН 1; элементы 27, 28 и 32 сравнения дво ичных чисел - на ИМС 531 СП1.

Значения двоичных эталонных кодов, устанавливаемых в логических блоках сравнения, можно изменять.

Технико-экономические преимущества данного изобретения по сравнению с базовым объектом состоят в том, что повышена стабильность компаратора, которая выражается в установлении на его выходе периодических и стабильных сигналов, а также повышена на 20% его точность.

Формула изобретения Компаратор, содержащий первый, второй и третий триггеры и операционный усилитель, инвертирующий вход которого является опорным входом компаратора, не- инвертирующйй вход - информационным входом компаратора, выход которого соединен с входом первого элемента НЕ и с 1-вхо- дом первого триггера, подключенного К-входом к выходу первого элемента НЕ, С-входом - к выходу генератора тактовых импульсов, а прямым выходом - к первому входу элемента И, отличающийся тем. что, с целью повышения стабильности и точности компаратора, в него введены четыре элемента задержки, регистр сдвига, два

счетчика импульсов, два дешифратора, четыре логических блока сравнения, второй элемент НЕ, причем вход первого элемента задержки соединен с выходом генератора

тактовых импульсов и со счетными входами первого и второго счетчиков импульсов, а выход - с вторым входом элемента И, подключенного выходом к С-входу регистра сдвига, соединенного D-входом с прямым

выходом первого триггера, R-входом - с выходом первого логического блока сравнения, с R-входами первого и второго счетчиков импульсов и второго триггера и с. входами четвертого элемента задержки и

второго элемента НЕ, первой группой из четырех разрядных выходов-с группой входов второго логического блока сравнения, а второй группой из трех разрядных выходов - с группой входов третьего логического блока сравнения, соединенного выходом с первым входом четвертого лцгического блока сравнения, а единичным входом - с выходом первого дешифратораТл с входом второго элемента задержки, подключенного

выходом к первому входу первого логического блока сравнения, вторым входом соединенного с прямым выходом второго триггера, с вторым входом четвертого логического блока сравнения и с входом Разрешение второго счетчика импульсов, третьим входом - с выходом третьего элемента задержки, а четвертым входом - с инверсным выходом второго триггера, с входом Разрешение первого счетчика импульсов и с третьим входом четвертого логического блока сравнения, подключенного выходом к D-входу третьего триггера, а четвертым входом - к первому выходу второго логического блока сравнения, соединенного вторым выходом с S-входом второго триггера, а единичным входом - с входом третьего элемента задержки и с выходом второго дешифратора, подключенного первым, вторым и третьим входами к

выходам первого, второго и третьего разрядов первого счетчиков, выходы первого, второго и третьего разрядов второго счетчика соединены с первым, вторым и третьим вхо- дами первого дешифратора, выход второго

элемента НЕ подключен к С-входу третьего триггера, выход четвертого элемента задержки и прямой и инверсный выходы третьего триггера являются стробирующим выходом и прямым и инверсным выходами компаратора.

0

Ii4j5

AJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Компаратор | 1990 |

|

SU1755253A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАНАЛОВ СВЯЗИ | 1991 |

|

RU2019038C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| Устройство для моделирования дискретного радиоканала | 1980 |

|

SU962999A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1997 |

|

RU2116004C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168282C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2002 |

|

RU2233038C1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Устройство для измерения искажения длительности импульсов | 1988 |

|

SU1559327A1 |

| УСТРОЙСТВО АДАПТИВНОГО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2001 |

|

RU2194366C2 |

Изобретение используется в системах управления, преимущественно в аналого- цифровых преобразователях. Цель изобретения - повышение стабильности и точности компаратора. Устройство содержит операционный усилитель, подключенный к элементам цифровой обработки получаемого в результате сравнения сигнала. Устройство работает в двух режимах: нормальном режиме, когда для получения сигнала на выходе устройства достаточно проанализировать двоичный код, формируемый за семь тактов работы из сигнала, снимаемого с выхода элемента сравнения аналоговых напряжений; режиме расширения, когда для получения сигнала на выходе устройства необходимо проанализировать расширенный двоичный код, формируемый за двенадцать тактов работы из сигнала, снимаемого с выхода элемента сравнения аналоговых напряжений. Анализ проводится путем сравнения с эталонными двоичными кодами в логических блоках сравнения. Компаратор формирует выходной строб-импульс сопровождения, тактирующий прямой и инверсный выходные логические сигналы ТТЛ-уровня. Управление работой компаратора осуществляется с помощью генератора тактовых импульсов, счетчиков импульсов, дешифраторов, элементов задержки. 11 ил. V Ё

%2 Uon3

i:

.больше

wo

Фиг. 2

Фаг Л

Фиг. 6

V

YYirW ./УЛугчл л,.л t

Ub

fl

JULJirn THL

, Фиг.8

Фиг.7

4

и

о

0

II3 ию

Фиг. 9

Фиг. 10

Риг. //

| Устройство для сравнения напряжений | 1974 |

|

SU541140A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Патент США № 3593162, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

Авторы

Даты

1991-02-28—Публикация

1988-08-29—Подача