(54) УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1981 |

|

SU993451A1 |

| Умножитель частоты | 1975 |

|

SU627572A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU898600A1 |

| Цифровой умножитель частоты | 1978 |

|

SU790181A1 |

| Умножитель частоты следования импульсов (его варианты) | 1983 |

|

SU1120483A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU961150A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU894847A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU884102A1 |

Изобретение относится к автоматике, измерительной и вычислительной технике и может найти применение в устройствах частотно-импульсной и цифровой обработки информации. Известно устройство цля умножения частоты слеаования импульсов, содержащее источник калиброванной частоты, источник входной частоты, два управляемых целителя частоты, измеритель периода, четыре блока сдвига. Управляемые делители частоты содержат по два вычитающих счетчика, два регистра памяти два вентиля переноса, четыре элемента задер жки и по два вентиля. Измеритель периода содержит суммирующий счетчик, вентиль переноса кода, два элемента задержки. В блоки сдвига входят по четыре элемента И, два элемента запрета, два элемента . Недостатками этого устройства являю ся значительные аппаратурные затраты и сложность алгоритма работы, что ограничивает область ого применения. Известен также укшожитель частоты следования импульсов, содержащий дели тель опорной частоты с коэффициентом деления, равным коэффициенту умножения, счетчик импульсов опорной частоты,входной и выходной формирователи, запоминающий регистр и блок управления 2. Недостатком этого умножителя является динамическая погрешность ограничивающая область его применения. Наиболее близким по технической сущности к предлагаемому является умножитель частоты, содержащий делитель опорной частоты, входной формирователь, регистры сдвига, блоки переноса кода, запоминающий регистр, блок управления и выходной формирователь з. Недостатком этого устройства является низкая надежность работы. Так, появление ложной единицы в одном из разрядов регистра сдвига полностью наруигост его работу. Циркуляция ложной единииьт может продолжаться неограни 4einio цолго, вызывая пульсацию частоты нп гчлхоце

умножителя. Причем начальный сброс регистра сдвига не восстанавливает работоспособность устройства.

Цель изобретения - повышение надежности работы умножителя.

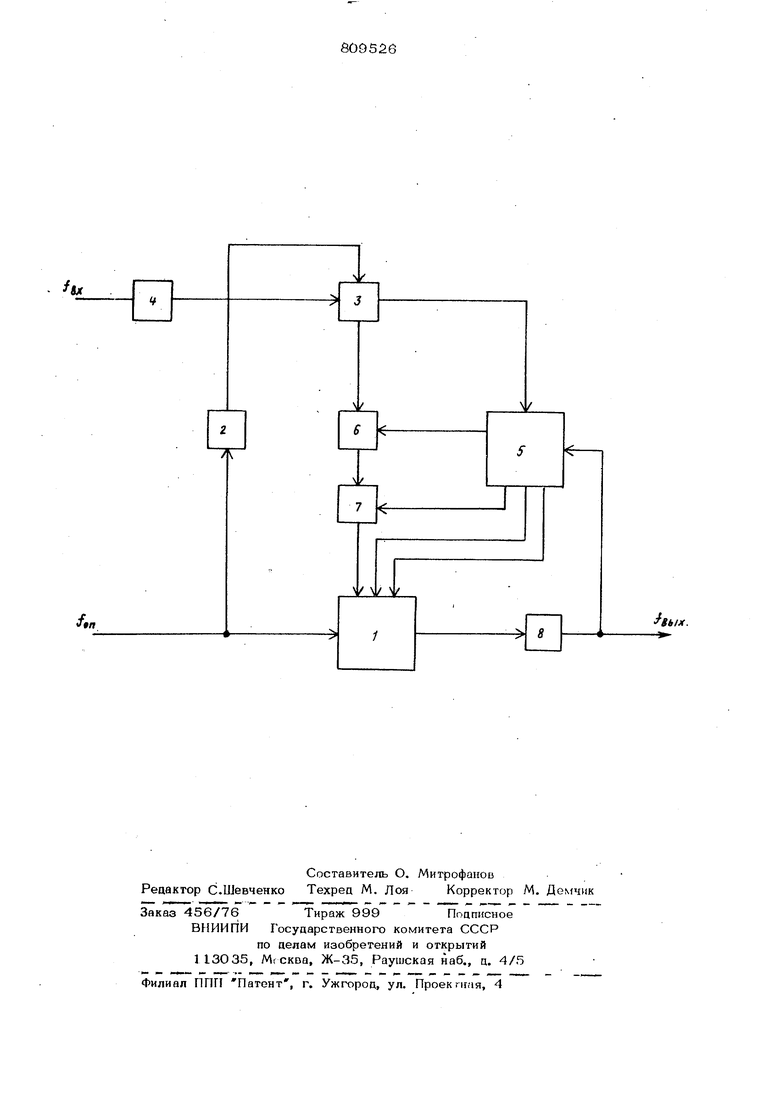

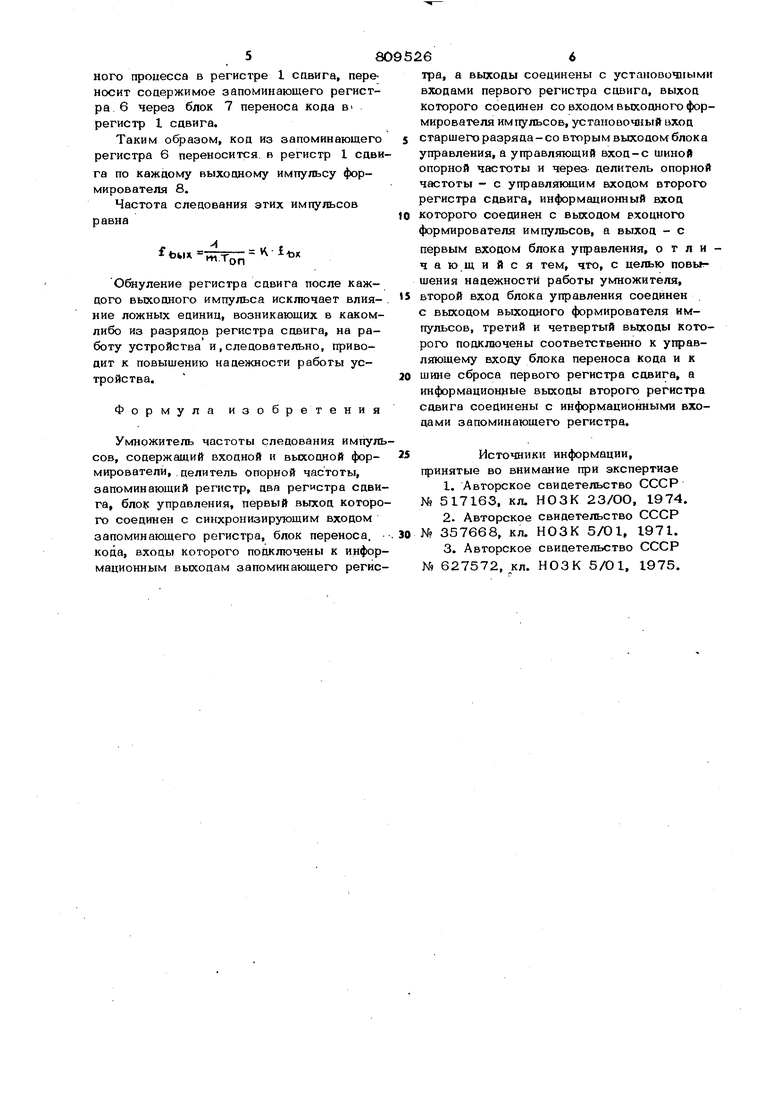

Поставленная цель достигается тем, что в умножителе частоты следования импульсов, содержащем входной и выходной формирователи, делитель опорной частоты, запоминающий регистр, два регистра ю го сдвига, блок управления, первый выход которого соединен с синхронизирующим входом запоминающего регистра, блок переноса кода, входы которого подключены к информационным выходам запоминающего регистра, а выходы соединены с установочными входами первого регистра сдви га, выход которого соединен со входом выхош ого формирователя импульсов, установочный вход старшего разряда - со вторым выходом блока управления, а управляющий вход - с шиной опорной частоты и через делитель опорной частоты - с управляющим входом второго регистра . сдвига, информационный вход которого сое динен с выходом входного формирователя импульсов, а выход-с первым входом блока управления, второй вход блока управления соединен с выходом выходного формирователя импу/шсов, третий и четвертый выходы которого подключены соответственно к управляющему входу блока переноса кода и к шине сброса первого регистра сдви га, а информацио1шые выходы второго .регистра сдвига соединены с информационными входами запоминающего регистра. На чертеже изображена структурная электрическая схема умножителя частоты следования импульсов. Умножитель содержит первый регистр 1 сдвига , делитель 2 опорной частоты, второй регистр 3 сдвига, входной формиро ватель 4 импульсов, блок 5 управления, запоминающий регистр 6, блок 7 перенос кода, выходной формирователь 8 импульсов. К шш1е опорной частоты подключены управляющий вход первого регистра 1 сдвига и через делитель 2 опорной часfofbi - управляющий вход второго регистра 3 сдвига, информационный вход которо го соединен с выходом входного формирователя 4, а выход старшего разряда ре гистра 3 сдвига подключен к первому входу блока 5 управления, информационны выходы регистра 3 сдвига соединены с информационными входами запоминающего регистра б, информационные выходы кото рого подключены к блоку 7 переноса кода. Выходы блока 7 соединены с установочными входами первого регистра 1 сдвига, выход старшего разряда которого соединен с входом выходного формирователя 8, выход которого подключен к второму входу блока 5 управления, четыре выхода которого подключены соответственно к синхронизирующему входу запоминающего регистра 6, к установочному входу старшеразряда первого регистра 1 сдвига, к управляющему входу блока 7 переноса и к шине сброса регистра 1 сдвига. Устройство работает следующим образом. Импульсы опорной частоты поступают на вход делителя 2, коэффициент целения которого равен заданному коэффициенту умножения, и на управляющий вход регистра 1 сдвига. Импульсы с выхода делителя 2, частота следования которых равна подаются на управляющий вход регистра 3 сдвига. Каждый импульс умножаемой частоты поступает через входной формирователь 4 на рабочий вход регистра 3 сдвига, записывается в первом разряде этого регистра (разряд из состояния О переводится в состояние l) и последовательно переносится в последующие со скоростью, соответствующей частоте следования тактирующих импуль- ; сов. Число разрядов tn регистра 3 сдвига, находящееся между двумя возбужденными разрядами, пропорционально периоду входного сигнала Tg и равно 1/к-Т у/Тр,. Таким образом, в регистре 3 сдвига фиксируется каждый период Tg,y входного сигнала. Импульсы с последнего разряда регистра 3 сдвига поступают на вход блока 5 управления. Блок 5 управления формирует сигналы, поступающие на синхронизирующие входы запоминающего регистра и на установочный вход последнего разряда регистра 1 сдвига, при этом содержимое регистра 3 сдвига переносится в запоминающий регистр, а последний разряд регистра 1 сдвига переводится в .единичное состояние. Сигнал, снимаемый с последнего разряда регистра I сдвига, поступает на формирователь 8. , Импульс с выхода формирователя 8 поступает в блок 5 управления. При этом блок 5 управления каждый раз формирует два следующих друг за другом импульса, первый из которых поступает на шину сброса регистра I сдвига, а второй, сдвинутый относитель)ю первого на время, равное максимальному времени переход58ного ароцесса в регистре 1 савига, пере носит соцержимое запоминающего регистра. 6 через блок 7 переноса кода В регистр I савига. Таким образом, код из запоминающего регистра 6 переносится, в регистр 1 сдви га по каждому выходному импульсу формирователя 8. Частота следования этих импульсов равна Обнуление регистра сдвига после каждого выходного импульса исключает влияние ложных единиц, возникающих в какомлибо Из разрядов регистра сдвига, на работу устройства и,следовательно, приводит к повышению надежности работы устройства. рмула изобретения Умножитель частоты следования импуль сов, содержащий входной и вьсходной формирователи, .делитель опорной частоты, запоминающий регистр, двп регистра сдви га, бло(с управления, первый выход которо го соединен с синхронизирующим входом запоминающего регистра, блок переноса. кода, входы которого подключены к инфор мационным выходам запоминающего регис 6 тра, а выходы соединены с установочными входами первого регистра сдвига, выход которого соединен со входом выходного формирователя импульсов, установочный вход старшего разряда - со вторым выходом блока управления, а управляющий вход-с шиной опорной частоты и через делитель опорной частоты - с управляющим входом второго регистра сдвига, информационный вход которого соединен с выходом входного формирователя импульсов, а выход - с первым входом блока управления, отличающийся тем, что, с целью повытшения надежности работы умножителя, второй вход блока управления соединен с выходом выходного формирователя импульсов, третий и четвертый выходы которого подключены соответственно к угфавляющему вх.оау блока переноса кода и к шине сброса первого регистра сдвига, а информационные выходы второго регистра сдвига соединены с информационными входами запоминающего регистра. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N9 517163, кл. НОЗК 23/ОО, 1974. 2.Авторское свидетельство СССР № 357668, кл. НОЗК 5/01, 1971. 3.Авторское свидетельство СССР N9 627572, кл. НОЗК 5/01, 1975.

/ir

9П

Авторы

Даты

1981-02-28—Публикация

1979-04-17—Подача