Изобретение относится к автома,тике, измерительной и вычислительной технике и может найти применение в устройствах частотно-импульсной и цифровой обработки информации.

Известен умножитель частоты, содержа1ций делитель опорной частоты, входной формирователь импульсов, два регистра сдвига,два блока переноса код а, запоминающий регистр,блок управ-„ ления и выходной формирователь ClJ.

Недостаток данного умножителя частоты -невысокая точность умножения, что ограничивает его применение..

Наиболее близким к предлагаемому по технической сущности является умножитель частоты следования импульсов, содержащий последовательно соединенные входной формирователь импульсов, первый регистр сдвига, запоминающий регистр, блок переноса кода, второй регистр сдвига, выходной формирователь импульсов и блок управления, второй вход которого со-, единен с вторым выходом регистра сдвига, а первый выход - с вторым входом 8апо1 шнающего регистра, выход - с вторым входом блока переноса кода, третий и четвертый выхода - с вторым и третьим входами второго регистра сдвига, четвертый вход которого соединен с входом . делителя опорной частоты и шиной опорной частоты, а выход делителя опорной частоты соединен с вторьм входом первого регистра сдвига С2 .

Однако устройство характеризуется недостаточно высокой точностью умножения.

10

Цель изобретения - повышение точности умножения.

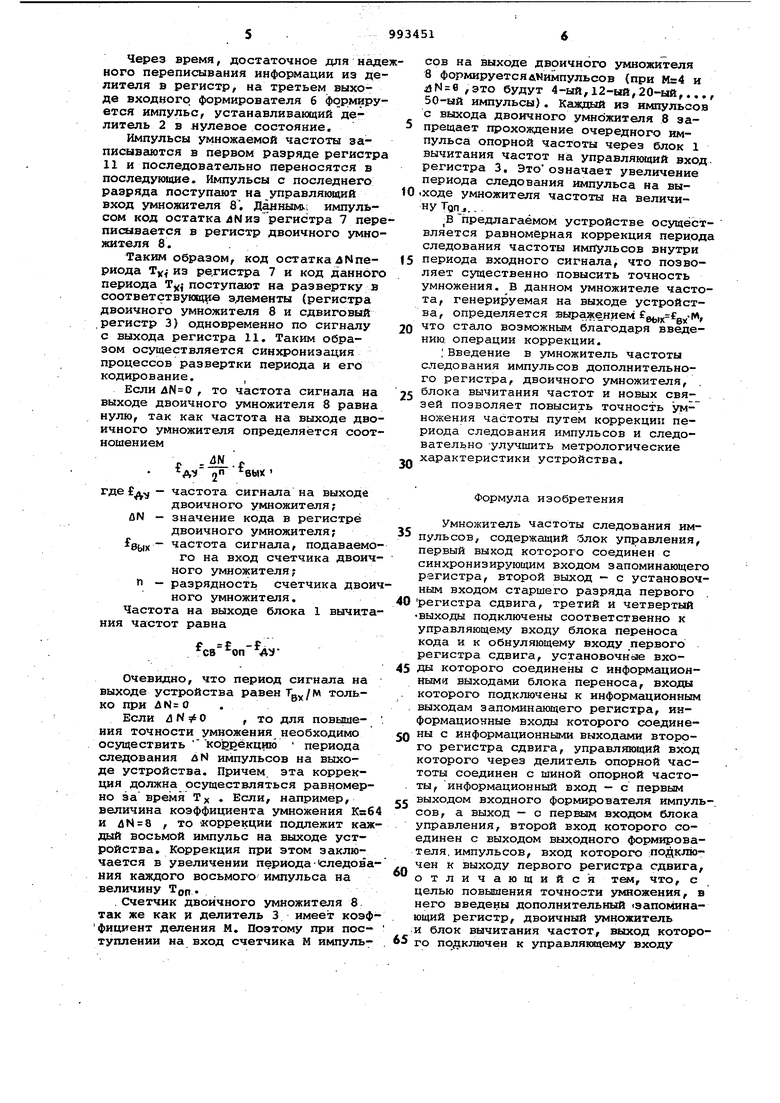

Поставленная цель достигается тем, что в умножитель частоты следования импульсов, содержащий блок управления,

15 первый выход.которого соединен с синхронизирующим входом-запоминающего регистра, второй ВЕ2ХОД - с установочным входом старшего разряда первого регистра сдвига, третей и чет20вертый выходы подключены соответственно к управлянлцему входу блока не.- . реноса 2кодс; к обнуляющему входу первого регистра сдвига, установочные входы которого соединены с информаци25 онными выходами блока переноса, входы которого подключены к информационным выходам запоминающего регистра, информационные входы которого соеди. нены с информационными выходами вто30,рого регистра сдвига, управляющий вход которого через делитель опорной частоты соединен с шиной опорной частоты, информационный вход - с первым выходом входного формирователя импуль сов, а выход - с первым входом блока управления, второй вход которого соединен с выходом выходного формирователя импульсов, вход которого подключен к выходу первого регистра сдвига, введены дополнительн.ый. запоминающий регистр, двоичный умножитель и блок вычитания частот, выход которого подключен к управляющему входу первого регистра сдвига, первый вход - к шине опорной частоты, второй - к выходу двоичного умножителя, счетный вход которого соединен с выходом выходного формирователя импульсов, управляющий вход - с выходом второго регистра сдвига, информационные входы - с информационными выходами дополнительного запоминающего регистра, информационные входы которого подключены к информационным выходам делителя опорной час „ /ГхГо сТрмирователя импульсов, а синхронизирующий вход дополнительного запоминающе го регистра соединенс третьим выходом входного формирователя импульсов На чертеже представлена структурная схема устройства. Умножитель содержит блок 1 вычитания частот, делитель 2 опорной частот первый регистр 3 сдвига, блок 4 управ ления, запоминающий регистр 5, входной формирователь б импульсов, допол нительный регистр 7 сдвига, двоичный умножитель 8, выходной формирователь 9 импульсов, блок 10 переноса кода, второй регистр 11 сдвига, шину входных импульсов, шину опорной /частоты. Дво.ичный умножитель 8 состоит из счетчика импульсов, регистра, группы элементов И и суммирующего элемента. Устройство работает следующим образ ом. Импульсы опорной частоты поступают на вход делителя 2 и на первый вход блока 1. Коэффициент деления делителя 2 равен заданному коэффициенггу умножения М. Импульсы с выхода делителя 2, частота следования которых равна уоп/М , подаются на управляющий вход регистра 11. Каждый импульс умножаемой частоты поступает через входной формирователь б на информационный вход регистра 11,записывается в первом разряде этого ре гистра (разряд из состояния О пе реводится в состояние 1) и после довательно переносится в последующие Число разрядов К регистра 11, находя щееся между двумя разрядами, в единичном состоянии пропорционально целой части отношения периода Tj, входного сигнала, и периода импульсов, с выхода делителя 2Т т.е.Е, Таким образом, в регистре 11 фиксируется каждый период Тех входного сигнала. Импульсы с последнего разряда регистра 11 сдвига поступают на вход блока 4 и вход синхронизации умножителя 8. Блок 4 управления формирует сигналы, поступающие на синхронизирующие входы регистра 5 и на установочный вход последнего разряда регистра 3, при этом содержимое регистра 11 сдвига переносится в регистр 5, а последний разряд регистра 3 переводится в единичное состояние. Сигнал, снимаемый с последнего разряда регистра 3, поступает на формирователь 9. Импульс с выхода формирователя 9 поступает в блок.4 и на счетный вход умножителя 8. При этом блок 4 каждый раз формирует два следующих друг за другом импульса, первый из которых ---:,-.:™-.--. ра 3, а второй, сдвинутый относительно первого на время, равное максимальному времени, переходного процесса в -регистре 3 сдвига, переносит содержимое регистра 5 через блок 10 в регистр 3. Таким образом, код из ре гистра 5 переносится в регистр 3 сдвига по каждому импульсу с выхода формнp gj 9 . ; л,,,„„, с „„„,„„, деляемый формирователем 6,делитель 2 успевает сформировать определенное количество импульсов, поступающих на управляющий вход регистра 11, а так как перед каж,цым очередным тактом работы делитель устанавливается сигналом с формирователя 6 в нулевое состояние, то к концу периода Т,при ().. ТхТ„„ условии, что будет сформ.ирован некоторый код д N , определяемый разностью .N .T,-M-E,i(). Значение.данного остатка можно также выразить в виде лМ м-чак 14 / г «.т где чак - дробная часть числа - , С учетом этого истинное значение периода Тунаходится в виде К4Ч) По окончании периода Т входного сигнала импульсом с второго выхода входного формирователя 6 кодйЫиз делителя 2 переносится в регистр 7.

Через время, достаточное для наденого переписывания информации из делителя в регистр, на третьем выходе входного формирователя 6 формируется импульс, устанавливающий делитель 2 в нулевое состояние.

Импульсы умножаемой частоты записываются в первом разряде регистра 11 и последовательно переносятся в последующие. Импульсы с последнего разряда поступают на управлякяций вход умножителя 8. Дадным ; илшульсом код остатка ЛМ из регистра 7 переписывается в регистр двоичного умножителя 8. .

Таким образом, код остатка 4Nneриода Tyj из регистра 7 и код данного периода Ту,- поступают на развертку в соответствующие элементы (регистра двоичного умножителя 8 и сдвиговый регистр 3) одновременно по сигналу с выхода регистра 11. Таким образом осуществляется синхронизация процессов развертки периода и его кодирование. ,

Если , то частота сигнала на выходе двоичного умножителя 8 равна нулю, так как частота на выходе двоичного умножителя определяется соотношением

. UN if

Г - -С

А-; 2 вы«

где ,j - частота сигнала на выходе

двоичного умножителя; uN - значение кода в регистре

двоичного умножителя; вых частота сигнала, подаваемого на вход счетчика двоичного умножителя;

п - разрядность счетчика двоичного умножителя.

Частота на выходе блока 1 вычитания частот равна

Очевидно, что период сигнала на выходе устройства равен только при ДМ О .

Если Л N ь О , то для повышеНИН точности умножения необходимо осуществить коррекцию периода следования aN импульсов на выходе устройства. Причем, эта коррекция должна осуществляться равномерно за время ТX . Если, например, величина коэффициента умножения и , то коррекции подлежит каждый восьмой импульс на выходе устройства. Коррекция при этом заключается в увеличении периода -следования каждого восьмого импульса на величину ТОР.

. Счетчик двоичного умножителя 8 так же как и делитель 3 имеет коэффициент деления М. Поэтому при поступлении на вход счетчика М импульсов на выходе двоичного умножителя 8 формируетсядмимпульсов (при и ,это будут 4-ый,12-ый,20-ый,..,, 50-ый импульсы). Каждый из импульсов с выхода двоичного умножителя 8 запрещает прохождение очередного импульса опорной частоты через блок 1 вычитания частот на управляющий вход. регистра 3. Это означает увеличение периода следования импульса на вы.ходе умножителя частоты на величину ТапJ...

В предлагаемом устройстве осуществляется равномерная коррекция периода следования частоты импульсов внутри

периода входного сигнала, что позволяет существенно повысить точность умножения. В данном умножителе частота, генерируемая на выходе устройства, определяется выражением g(,,,

что стало возможным благодаря введению операции коррекции.

;Введение в умножитель частоты следования импульсов дополнительного регистра, двоичного умножителя, .

блока вычитания частот и новых свя- эей позволяет повысить точность умножения частоты путем коррекции периода следования импульсов и следовательно -улучшить метрологические

характеристики устройства.

Формула изобретения

Умножитель частоты следования импульсов, содержащий блок управления, первый выход которого соединен с синхронизирующим входом запоминающего регистра, второй выход - с установочным входом старшего разряда первого

регистра сдвига, третий и четвертый выходы подключены соответственно к управляющему входу блока переноса кода и к обнуляющему входу первого . регистра сдвига, установочнае входы которого соединены с информационными выходами блока переноса, входы которого подключены к информёщионным выходам запоминающего регистра, информационные входы которого соединены с информационными выходами второго регистра сдвига, управляющий вход которого через делитель опорной частоты соединен с шиной опорной частоты, информационный вход - с первым

выходом входного формирователя импуль55

сов, а выход - с первым входом блока управления, второй вход которого соединен с выходом выходного формирователя, импульсов, вход которого лодключен к выходу первого регистра сдвига,

60 отличающийся т&л, что, с целью повышения точности умножения, в него введены дополнительный 1эапоминающий регистр, двоичный умножитель и блок вычитания частот, выход которо65 го подключен к управляющему входу

первого регистра сдвига, первый вход к шине опорной частоты, второй - к выходу двоичного умножителя, счетный вход которого соединен с выходом выходного формирователя импульсов, управляющий вход - с выходом второго регистра сдвига, информационные, входы - с информационными выходами дополнительного Запоминающего регистра, информационные входы которого подключены к информационным выходам делителя опорной частоты, управляющий вход

которого подключен к второму выходу входного формирователя импульсов, а синхронизирующий вход дополнительного запоминающего регистра соединен с третьим выходом входного формирователя импульсов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР . 627572, кл, Н 03 К 5/01, 1977.

2.Авторское свидетельство СССР 809526, кл. Н 03 К 5/01, 1979.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1979 |

|

SU809526A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Цифровой умножитель частоты | 1978 |

|

SU790181A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU898600A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU884102A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU894847A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Устройство для умножения частоты следования импульсов | 1982 |

|

SU1040598A1 |

| Умножитель частоты | 1975 |

|

SU627572A1 |

Авторы

Даты

1983-01-30—Публикация

1981-08-05—Подача