2. Умножитель поп, 1, отличающийся тем, что блок памяти .содержит элемент ИЛИ, триггер и элемент И, причем счетный вход триггера явпяется первым входом блока памяти, первый и второй входы элемента ИЛИ - соответственно его вторым

и третьим входами, установочный вход триггера соединен с выходом элемента ИЛИ, первый вход элемента И соединен с выходом триггера, второй вход является четвертым входом, а выход - входом блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1987 |

|

SU1448394A2 |

| Умножитель частоты следования импульсов | 1981 |

|

SU976482A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Умножитель частоты | 1987 |

|

SU1499341A1 |

| Число-импульсное линеаризующее устройство с масштабированием | 1983 |

|

SU1109759A1 |

| Дискретный умножитель частоты | 1977 |

|

SU736099A1 |

| Умножитель частоты | 1979 |

|

SU813728A1 |

| Устройство для измерения частоты | 1983 |

|

SU1170373A1 |

| Умножитель частоты | 1988 |

|

SU1562908A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

1. УМНОЖИТЕЛЬ ЧАСТОТЫ содержащий блок управления, вход которого соединен с входом устройства, генератор опорной частоты, выход которого подключен к счетному входу первого счетчика импульсов и первому входу делителя частоты, второй вход которого соединен с первым выходом блока управления, а Ш1псод - со счетным входом второго счетчика импульсов, установочный вход которого подключен к выходу Сброс блока управления, регистр, информационные входы которого соединены с соответствующими информационными выходами второго счетчика импульсов, блок элементов И, группа первых входов которого подключена к информационным выходам регистра, а выходы - к информационн1Ф1 входам первого счетчика импульсов, выход которого подключен к выходу умножителя частоты и к управляющему входу блока элементов И, представляющему собой объединенные вторые входы элементов И, отличающийся тем, что, с целью повышения точности умножения путем исключения пульсахщй выходного сигнала, в него введены первый и второй дешифраторы, входы которых соединены с соответствующими информационными выходами второго (Л счетчика импульсов, первого дешифратора подключен к первому входу блока памяти, выход второго дешифратора подключен к второму входу блока памяти, третий вход которого соединен с выходом Сброс блока управления, четвертый вход блежа памяти соединен с выходом Перепись блока уп:о сд равления, причем выход блоке памяти подключен к управляющему входу регистра..

Изобретение относится к измерительной технике и автоматике и может быть использовано для повышения быстродействия процесса преобразования частоты при работе с низкочастотными датчиками.

Известен умножитель частоты, содержащий делитель опорной частоты с коэффициентом деления, равным коэффициенту умножения, счетчик импульсов опорной частоты, входной и выходной формирователи, запоминающий регистр и блок управления, один из выходов которого подключен к нулевым входам всех, разрядов делителя опорной частоты и запоминающего регистра нулевой выход каждого разрЗДа счетчика импульсов соединен с первым входом первого блока элементов И, второй вход которого подключен к второму выходу блока управления, а выход к единичному входу того же разряда запоминающего регистра, причем третий выход блока управления подключен к единичным входам всех разрядов счетчика импульсов, единичный выход каждого разряда запоминакицего регистра соединен с входом второго блока элементов И, выход которого соединен с единичным входом того же разряда счетчика импульсов опорной частоты, а второй выход - с выходной шиной выходного формирователя, вход которого подключен к выходу счетчика импульсов опорной частоты tOНедостатком устройства является низкая помехоустойчивость.

1 аиболее близким к предлагаемому является умножитель частоты, содержащий генератор опорной частоты, делитель опорной частоты, счетчик ямпульсов, запоминающий §ргистр, блок управления, счетчик импульсов опорной частоты, блок памяти с не менее чем тремя состояниями, блок элементов И и формирователь импульсов, причем генератор опорной частоты соединен с входами делителя частотьг и счетчика импульсов опорной частоты, входы разрядов запоминающего регистра подключены к счетчику, счетный вход которого соединен с выходом делителя частоты, входы разрядов счетчика импульсов опорной частоты под.ключены через формирователь импульcd к выходам запоминающего регистра а вход управления записью счетчика импульсов опорной час1оты соединен с его выходом, вход управления записью запоминающего регистра и входы установки в исходное состояние счетчика и делителя частоты подключены к выходам блока управления, вход которого соединен с входом умножителя частоты, к которому подключен вход блока памяти, другой вход которого соединен с выходом счетчика, выход умножителя частоты, к которому подключен вход блока памяти, другой вход которого соединен с выходом блока элементов И, первая группа входов которого подключена к выходу счетчика импульсов опорной частоты, а вторая - к выходу устройства памяти с тремя состояниями, счетный вход триггера через блок элементов И соединен с входом блока памяти и с одним из выходов триггера, второй выход которого является выходом блока памяти, счетный вход триггера блока памяти подключен к выходу другого триггера блока памяти, а выходы установки в нулевое состояние триггеров блока памяти соединены с входом блока памяти .2.

Данный умножитель частоты невозожно использовать при построении нформационно-измерительных систем случаях действия помех на входе ибо в случаях, когда исследуемые s роцессы характеризуются высокой диамичностью. При этих условиях налюдается пульсирующий выходной сигнал, т.е. паузы (которые могут быть остаточно большими) чередуются с 10 ачками импульсов, генерируемых умножителем, что значительно затрудняет реализацию операции кодирования и, следовательно, получения инормации о ходе процесса. Таким обра-15 зом, недостатком данного умножителя является низкая точность умножения, обусловленная пульсирующим характером выходного сигнала как в случае наложения на контролируемую последо- 20 вательность шумового сигнала, так и в случае контроля быстро протекающих процессов.

Цель изобретения - повышение точности умножения путем исключения 25 пульсаций выходного сигнала. .

Поставленная цель достигается тем, что в умножитель частоты, содержащий блок управления, вход которого соединен с входом устройства, генератор зо опорной частоты, выход которого подключен к счетному входу первого счетчика импульсов и первому входу делителя частоты, второй вход которого соединен с первым выходом блока уп- , равления, а выход - со счетным входом второго счетчика импульсов, установочный вход которого подключен к выходу Сброс блока управления, регистр, информационные входы которого соединены с соответствующими информационными выходами второго счетчика импульсов, блок элементов И, группа первых входов которого подключена к информационным выходам регистра,j а выходы - к информационным входам первого счетчика импульсов, выход которого подключен к выходу умножителя частоты и к управляющему входу блока элементов И, представляющему JQ собой объединенные вторые входы элементов И, введены первый и второй дешифраторы, входы которых соединены с соответствуюш;ими информационными выходами второго счетчика импульсов, jj выход первого дешифратора подключен к первому входу блока памяти, выход второго дешифратора подключен к второму входу блока памяти, третий вход которого соединен с выходом Сброс блока управления, четвертый вход блока памяти соединен с выходом Перезапись блока управления, причем выход блока памяти подключен к управляющему входу регистра.

При этом блок памяти содержит элемент ИЛИ, триггер и элемент И, причем счетный вход триггера является первым входом блока памяти, первый. и второй входы элемента ИЛИ - соответственно его вторым и третьим входами, установочный вход триггера соединен с выходом элемента ИЛИ, первый вход элемента И соединен с выходом триггера, второй вход является четвертым входом, а выход - выходом блока памяти.

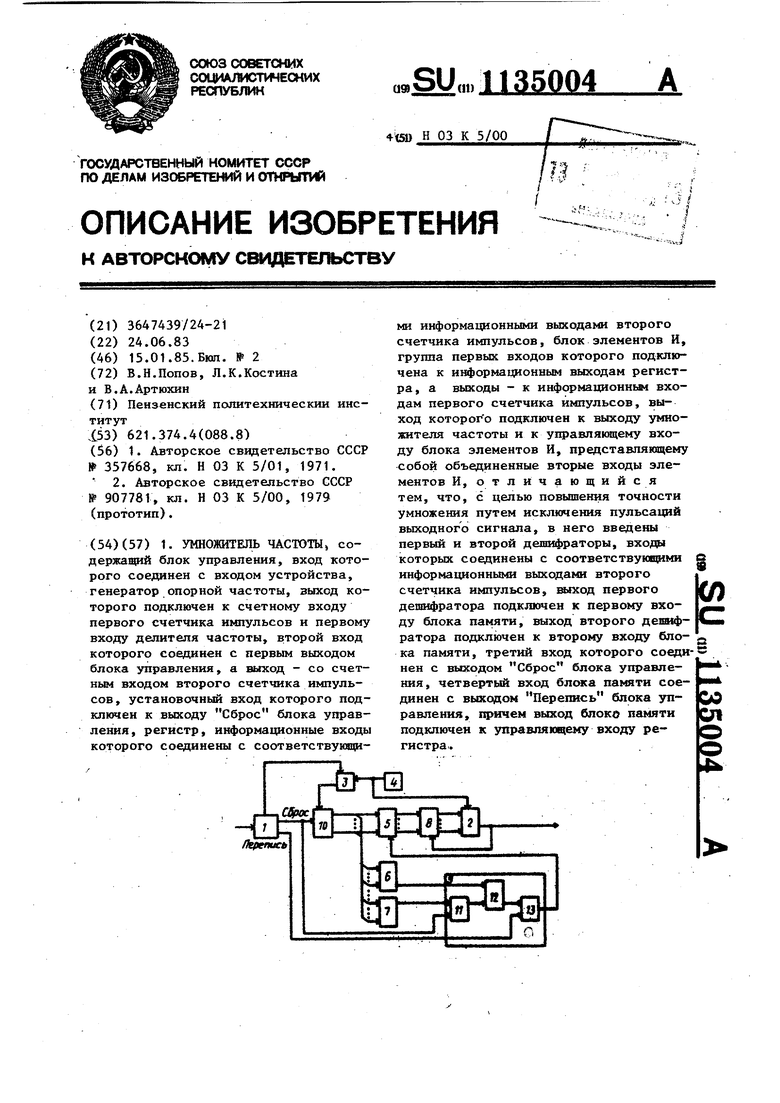

На чертеже представлена структурная схема предлагаемого умножителя частоты.

Умножитель частоты содержит блок 1 управления, первый счетчик 2 импульсов, делитель 3 частоты, генератор, 4 опорной частоты, регистр 5, первый дешифратор 6, второй дешифратор 7, блок 8 элементов И, блок 9 памяти, второй счетчик 10 импульсов. Вход блока 1 управления соединен с входом умножителя частоты, генератор 4 соединен с первым входом делителя 3 и счетным входом счетчика 2, второй вход делителя 3 соединен с блоком 1 управления, счетный вход второго счетчика 10 соединен с выходом делителя 3, установочный вход которого подключен одновременно к выходу Сброс блока 1 управления. Информационные входы регистра 5 соединены с информационными входами второго счетчика 10, входы блока 8 элементов И подключены к информационным выходам регистра 5, а выходы - к информационным входам первого счетчика

J2, выход которого подключен к выходу устройства и к управляницему входу блока 8 элементов И. Входы первого и второго дешифраторов 6 и 7 соединены с соответствующими информационными вькодами второго счетчика 10, выход первого дешифратора подключен к первому входу блока 9 памяти,

;второго - к второму его входу, третий вход блока 9 соединен с выходом Сброс, четвертый вход - с выходом Перезапись блока 1, выход блока 9 подключен к управлякщеь у входу регистра 5. Блок 9 памяти содержит элемент ИЛИ 11, триггер 12, элемент И 13, причем первый вход элемента ИЛИ 11 подключен к второму входу блока 9 памят% второй вход элемента ИЛИ 11 соединен с третьим входом блока 9 памяти, счетный вход триггера 12 подключен к первому входу блока 9 па мяти, установочный вход триггера 12 соединен с выходом элемента ИЛИ 11, первый вход элемента И 13 соединен с выходом триггера 12, второй вход элемента И 13 подключен к четвертому входу блока 9 памяти, выход элемента И 13 соединен с выходом блока 9 памяти. Умножитель Частоты работает еледующим образом. На вход блока 1 управления поступают импульсы умножаемой частоты, при этом на шлходах блока управления формируются управляющие импульсы обеспечиваюоцие синхронизацию работы устройства. Первым импульсом обеспечивается перепись содержимого счетчи ка 10 в регистр 5. Данный импульс, формируемый на выходе Перепись бло ка 1 управления, поступает на блок 9 памяти, где проходит через открытый элемент И 13 и поступает на управляю щий вход регистра 5. Содержимое счет чика, определяемое выражением . где fд - частота следования импульсов опорного генератора; М - коэффициент деления делителя 3 частоты, переписывается в регистр 5. На счетный вход счетчика 2 поступают импуль сы опорной частоты f с генератора опорной частоты. Счетчик 2 суммирует поступающие импульсы. В момент переполнения на его выходе формируется импульс, который поступает на выход умножителя частоты, а также обеспечи вает перепись содержимого регистра 5 через блок 8 элементов И в счетчик в дополнительном коде. Счетчик 2 вновь начинает сумьофовать импульсы с выхода генератора опорной частоты и в момент переполнения счетчика вновь на его выходе формируется импульс. С учетом того, что где индекс вверху соответствует + суммирующему счетчику и - вычитающему;NX -дополнительный код N, частота выходного сигнала записывается в . После формирования сигнала Перепись блок 1 управления с задержкой на период формирует сигналы Сброс, обеспечивающий установку в нулевое состояние счетчика 10 и делителя 3. Кроме того, импульс сброса с выхода блока 1 управления поступает в блок 9 памяти, где проходит через элемент ИЛИ 11 и устанавливает в нулевое состояние триггер 12. Затем импульсы опорной частоты с выхода делителя 3 частоты начинают поступать на вход счетчика 10, т.е. производится кодирование очередного периода Т входного сигнала. Формируемый в счетчике 10 код контролируется дешифраторами 6 и 7, причем дешифратор 6 настроен и выделяет код, соответствующий минимальному периоду Т. входного сигнала, а дешифратор 7 - код, соответствую1ций максимальному периоду Т входного сигнала. Значения периодов и Т определяют границь рабочего диапазона В .,,(/Т.) для данного умножителя . При работе умножителя частоты с реальными входными сигналами возможны случаи, когда Т.Т. и Т,.Т. В первом случае устройство работает следующим образом. Код, формируемьй в счетчике 10, не достигает к моменту окончания Ki ( значения, контролируемого дешифратором 6, и на выходе дешифратора И1в1ульс не формируется. Импульс же переписи, поступающий в блок 9 памяти, на выход элемента И 13 не проходит, так как элемент И 13 закрыт сигналом нулевого уровня с выхода триггера 12. Таким образом, содержимое счетчика 10 в регистр не переписывается, и умножитель продолжает отрабатывать код предыдущего периода, т.е. пульсации не возникает. В случае, ,,,, дешифратор 6 срабатывает и формирует импульс, который устанавливает триггер 12 блока управления в единич ное состояние. Триггер открывает эле мент И 13. Импульс Перепись проходит в этом случае через открытый элемент И 13 и поступает на управляю щий вход регистра 5, обеспечивая перепись содержимого счетчика в регистр. Если T,i Т„«, , то последовательJHo срабатывают оба дешифратора 6 и 7, причем сигнал с первого устанавливает триггер 12 в единичное со стояние, со второго - в нулевое. Элемент И 13 закрыт. Теперь импульс Перепись также не проходит через элемент И 13, и содержимое регистра не изменяется. Умножитель продолжает генерирование импульсов с частотой, соответствующей коду предьщущего периода. Таким образом, предлагаемый умножитель частоты, в. отличие от прототипа, генерирует выходную последовательность импульсов постоянно без пауз, что повышает его помехоустойчивость, так как кратковременные импульсные помехи не нарушают работу , умножителя.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 0 |

|

SU357668A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-01-15—Публикация

1983-06-24—Подача