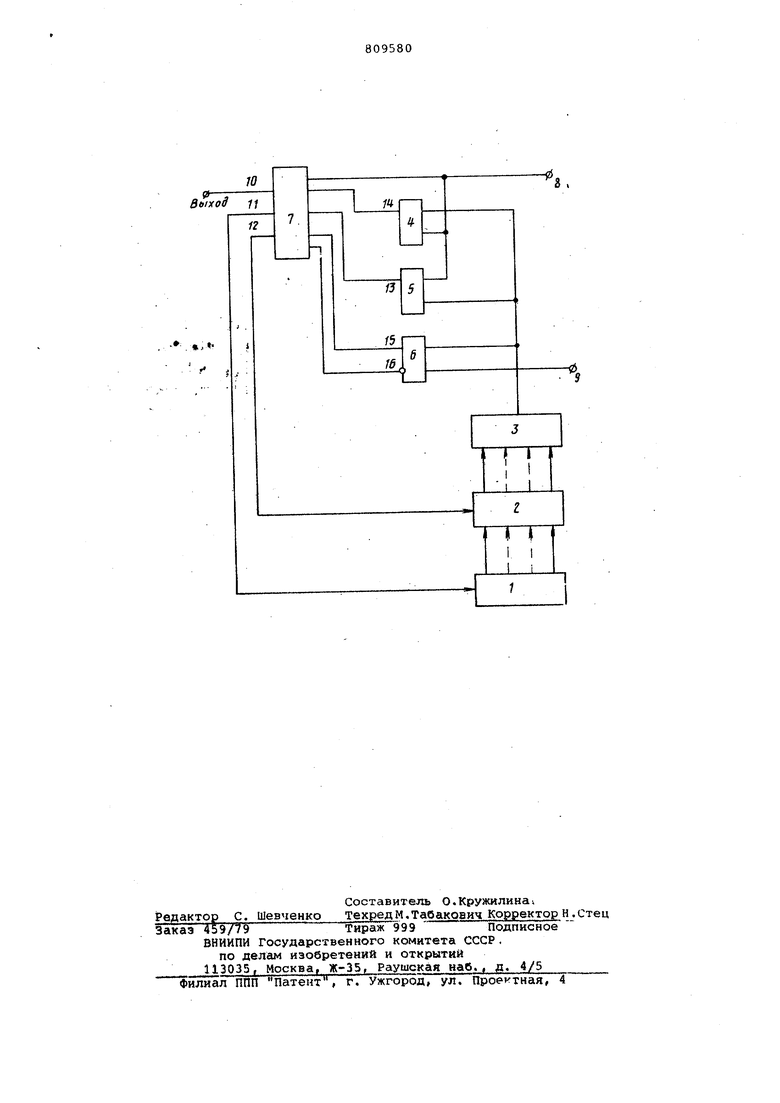

(54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ Цифрами 8 и 9 обозначены входная шина и дополнительная входная шина, цифрами 10-12 - выходы элемента 7, а цифрами 13-16 - выходы триггеров 4-6. Устройство работает следующим об разом. На шину 8 подается импульсная последовательность с частотой FO и скважностью, равной двум. На шину 9 поступает потенциальный сигнал (О и 1), определяющий один из двух режимов работы делителя: период выходного сигнала кр тен полупериоду входных импульсов, период выходного сигнала кратен периоду входных импульсов.. Элемент 7 вырабатывает на своихвыходах 10-12 сигналы, соответствую щие логическим формулг1М и«- «« FflV и„- Uo- FO (О UM- FO(2) Utt- U,- FO(3) fQ - соответственно частоты прямой и проинвертированной входной последо вательности импульсов; напряжение на прямом выходе триггера 4; UD - напряжение на прямом в ходе триггера 5 Цц - соответственно напряже ния на прямом и инверс ном выходах триггера 6 Рассмотрим подробнее работу делител для случая«когда период выходного сигнала кратен полупериоду входной частоты, т.е. Т Р-- (4) где f - период выходного сигнаяа| TO период входного сигнЁша} Р - нечетное число. Для конкретности примем Р 9. . 7огда в течение работы делителя в блоке 1 хранится число М равиов целой части - (в данном случав ««). На ищие 0 устанавливается уровень« например 1, который поступая на управл вов(ия BkoA триггера б, его функционирование как сч«тмдго триггера. В начальньй мсмент времени в бло ке 1 и счетчике 2 находится число ММ, на выходе блока 3 сигнал отсут вует, триггеры 4-6 находятся в сброшенном состоянии (U|4 -О ttiji Ujj «о) элемент 7 - в закрытом состоянии по выходам 10 и 11, а по выходу 12 - в подготовленном состоянии. С поступлением на ишну 8 делителя импульсной последовательности РО она проходит через элемент 7 на вход счетчика 2. С приходом четвертого импульса, который в нашем случае Является последним в перзом, цик |ле счета, блок 3 определяет конечно состояние счетчика 2 и вырабатывает сигнал, поступающий на установочные входы триггеров 4 и 5 и на счетный вход триггера 6. Состояние триггеров изменяется, причем триггеры 4 и 6 перебрасываются непосредственно по сигналу с блока 3, а триггер 5 переключается по заднему фронту последнего импульса цикла счета, так как ему на вход синхронизации подается входная последовательность импульсов с шины 8 делителя . В соответствии с логическими вйражениями (1) и (2) на выходах 10 и 11 элемента 7 формируются им-: пульсы, совпадающие с паузой, последнего в перв цикле счета периода входной последовательности. С выхода 10 сигнал поступает на выход делителя, а с выхода 11 на вход блока 1 и тем самым счетчик 2 переводится в начальное состояние. Сигнал на выходе блока 3 отсутствует. Следующий, в нашем случае пятый, импульс 9ХОДНОЙ последовательности является первьв4 во втором цикле счета. Кроме того по переднему фронту этого импульса возвращается в исходное состояние триггер 4, а по заднему фронту - триггер 5. Триггер 6 сохраняет свое состояние. Второй цикл счета протекает аналогично первому в части работы блока 3 и триггеров 4 и 5. Но если в первом цикле счета триггер 6 по сигналу с блока 3 переключался из О в 1, то во втором цикле он по сигналу с блока 3 переходит из сосВ связи и состояние тояния с этим на входах элемента 7 присутствует комбинация сигналов отличная от комбинации в первом цикле. В соответствии С логическими формуЛсши Х), (2) и (3) на выходе 10 элемента 7 вырабатывается сигнал, оовпгшающий с импульсом вводной последс(овательности FQ следующим за последним во втором цикле счета, т.е. с пятым импульсом входной частоты Ft«а выход 12 блокируется на вреся этого Импульса, тем самым в последовательности импульсов, поступающих с выхода 12 элемента 7 на вход счетчика 2, пропускается один импульС| на выходе 11 элемента 7 сигнал установки счетчика 2 в начальное состояние образуется так же, как и в первом цикле счета. Таким образом использование сигнала с триггер 6, меняющего свое состояние через каящый хшкл счета по передиему фронту импульса с блока 3, позволяет получать на выходе делителя выходной сигнгш, совпадающий попеременно то с паузой, то с импульсом входной последовательности F, ,

и, следовательно, период выходного сигнала задается кратным полупериоду входной частоты. При получаем Т 9г-Кроме того, использование для получения, выходной последовательности импульсов сигналов с триггеров 4 и 5, сдвинутых друг относительно друга на половину периода входной частоты,, обеспечивает малые и равные задержки выходных импульсов, которые определяются задержкой в элементе 7 и не зависят от задержки в блоке 3, а также от задержки переключения триггеров 4 и 5. Если применяемая для построения делителя элементная база позволяет осуществлять логическую функцию И (ИЛИ) путем монтажа,то задержка выходного сигнала относительно входного определяется задержкой одного вентиля выбранной элементной базы.

В случае необходимости задания периода выходных импульсов равным целому числу периодов входной частоты FO, в блок 1 записывается число N - - 1 (в этом случае число Р четное). Например, если Р 10, то в блок 1 записьшается число 4, но в отличие от предыдущего случая на шину 9 делителя подается уровень О, который удерживает триггер 6 все время в сбрсяиенном состоянии. В связи с этим каждый цикл счета делителя протекает аналогично второму циклу счета предыдущего случая, т.е. постоянно выходной сигнал совпсщает с импульсом входной частоты F0, и постоянно пропускается соответствующий импульс в последовательности, поступсцощей на счетный вход счетчика 2. При Р 10 на выход делителя будет проходить каждый пятый импульси, следовательно, Т Ю-,Таким образом, применение в известном делителе частоты следования импульсов с переменным коэффициентом деления новых элементов - трех триггеров и логического элемента - позволяет вырабатывать частоту выходного сигнала с повышенной точностью, не увеличивая частоту входных импульсов, причем оыходная последовательность импульсов строго равномерна и имеет задержку отно0сительно входного сигнё1ла, определяемую задержкой одного вентиля выбранной элементной базы.

Формула изобретения

Делитель частоты следования им5пульсов с переменным коэффициентом деления, содержащий счетчик импульсов, информационные входы которого соединены с выходами блока установки, а выходы - со входами блока

0 опознавания, отличающийс я тем, что, с целью повышения стабильности частоты выходного сигнала, в него введены триггеры и логический элемент, первый вход которого соединен с входной шиной, оста5льные входы - с выходами триггеров, первые входы которых подключены к выходу блока опознавания, вторые входы первого и второго триггеров к входной аш«е, второй вход третье0го триггера - к дополнительной входной шине, а первый и второй выходы логического элемента соединены соответственно со счетным входом счетчика импульсов и входом блока установки.

5

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

624371, кл. Н 03 К 23/00,06.12.76.

2.Лейнов М.Л. и др. Цифровые де0лители частоты на логических элементах.М., Энергия, 1975, с. 103

JO

Btiixod /f

г,

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1980 |

|

SU894877A2 |

| Широкодиапазонный генератор импульсов с кратно дробной автоподстройкой частоты | 2019 |

|

RU2716222C1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

| Устройство для измерения механических величин | 1989 |

|

SU1737287A1 |

| Расширитель импульсов | 1980 |

|

SU902233A1 |

| Цифровой демодулятор частотно-манипулированных сигналов | 1982 |

|

SU1058083A1 |

| Устройство для стабилизации вакуума | 1983 |

|

SU1149060A1 |

| Устройство для управленияТиРиСТОРНыМ АВТОНОМНыМ иНВЕРТОРОМ | 1977 |

|

SU794704A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1267601A1 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2105410C1 |

-«

Авторы

Даты

1981-02-28—Публикация

1979-04-09—Подача