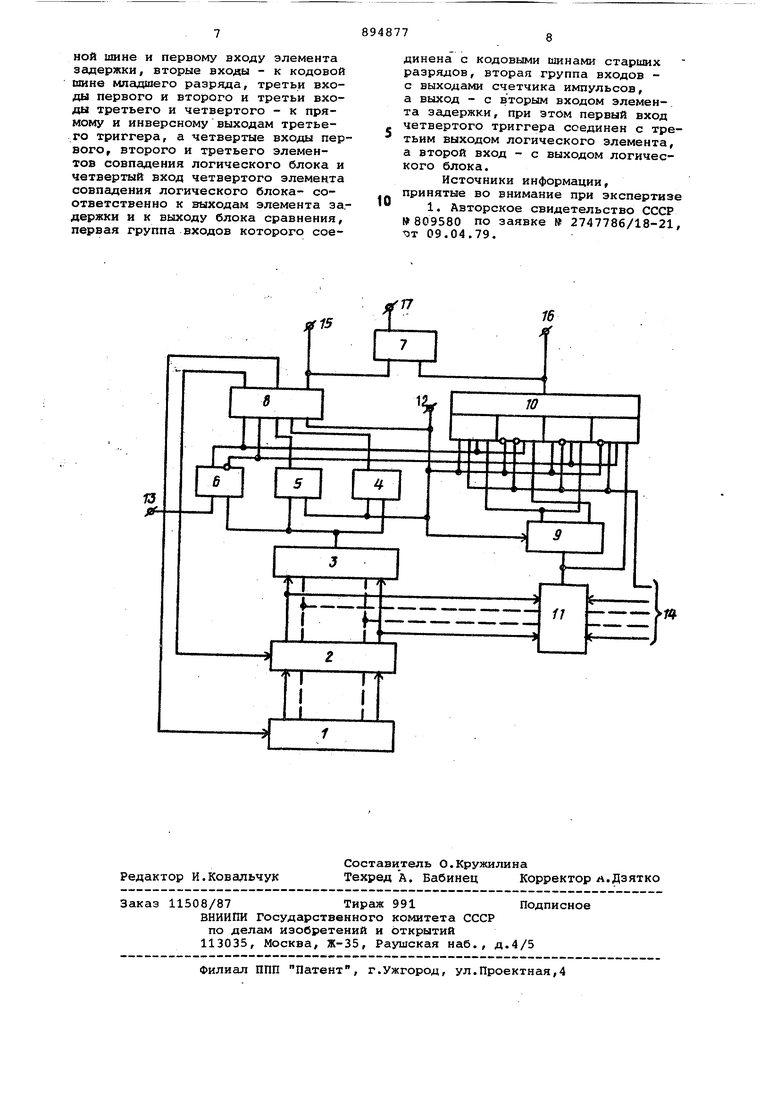

но к прямому и инверсному выходам третьего триггера, а четвертые входы первого, второго, .третьего элементов совпадения логического блока и четвертый вход четвертого элемента совпадения логического бло ка - соответственно к выходам элемента задержки и выходу блока сравнения кодов, первая группа входов -которого соединена с кодовыми ши- нами старишх разрядов, вторая группа входов - с выходами счетчика импульсов , а выход - с вторым входом элемента задержки, при этом первый вход четвертого триггера соединен с третьим выходом логического элемента, а второй вход - с выходом логического блока. На чертеже представлена структурная схема устройства. Устройство содержит блок 1 установки начального состояния счетчика импульсов, счетчик 2 импульсов, блок 3 опознавания конечного состояния счетчика импульсов, триггеры 4-7, ло гический элемент 8, элемент 9 задерж ки, логический блок 10, включающий в себя четыре элемента, совпадения и элемент сборки, блок 11 сравнения ко дов, входную 12 и дополнительную вхо ную 13 шины, кодовые шины 14, и выходные шины 15-17. . Устройство работает следующим образом. На входную шину 12 поступает импульсная последовательность с частотой fb (период TO ) и скважность, рав ной двум. На шину 13 подается потенциальный сигнал О или 1, определяющий режим работы делителя: вырабо ка выходного сигнала с периодом крат ным TO или кратным То/2. В блоке 1 содержится число N, определяющее пе риод Т (частоту F) выходных импульсо Разрядность числа - К. На шинах 14 поддерживаются уровни напряжения (О или 1), соответствующие коду числа My, определяющему величину сдвига по фазе импульсов, вырабатываемых на выходе 16 относительно импульсов на выходе 15, Разрядность числа N(f равна К+1. При задании периода Т выходных импульсов равным Р, То/2, а сдвига равным (здесь Р , Pj - целы числа), числа Н и NO определяются следующим образом: ff- / если Р - нечетное NfH р тU I ,если Р - четное, 2 (2 Логический элемент 8 вырабатывае на своих выходах сигналы, соответст вующие логическим формулам -Uas -FO Uft Uafi FO U,7 Uat -FoVUat Ugs FO , где FO , FO - соответственно частоты прямой и проинвертированной входной последовательности импульсов# ei соответственно напряжения на прямом и инверсном выгходах триггера б; Uj2 - напряжение на прямом выходе триггера 4 ; Ugj - напряжение на прямом выходе триггера 5. Сигнал на выходе 16 логического блока 10 соответствует логической формуле:U U и,о USB Foi;-U. Uto -U c-FoVUX--, Usi Uj -feV/Ui, . Uj, . Uj. FO U,«, - напряжение на входной кодовой шине 14 младшего разряда;Uji, - напряжение на выходе блока 11 сравнения кодов; I Цге. г4 напряжения на выходах блока 9 задержки. Рассмотрим конкретный пример работы делителя частоты. Пусть необходимо получить период Т выходных импульсов делителя равным 17.TO/2, а сдвиг по фазе между выходными, последовательностями равным 9 Ц,/2. При этом счетчик 2 импульсов работает на вычитание. В начальный момент времени при заданных условиях в блоке 1 хранится число (1000), на дополнительной входной шине 13 присутствует уровень 1, так как период выходных импульсов кратен , На входных кодовых шинах 14 присутствует код числа N.()P, -Pg +1 17-9+1 9(01001); Старшие разряды числа Ny.T.e. код (0100), присутствуют на вторых входах блока 11 сравнения, а состояние 1, соответствующее коду младшего разряда, на входах всех схем совпадения логического блока 10. При этом два элемента совпадения оказываются заблокированными, и их функционирование в данном примере анализироваться на будет. Для двух других элементов совпадения логического блока 10 уровень 1 является разрешающим, таким образом, формула (6) может быть записана в виде и« и; Uao F, VU; Uj-, UM FO. (7) Кроме того, в начальный момент триггеры 4 и б находятся в состоянии . О, триггер 5 в состоянии 1. Счетчик 2 импульсов находится в исходном состоянии. Первый импульс входной частоты F , поступающий на входную шину 12, в соответствии с формулой (5) проходит на выход 15 логического элемента 8. По заднему- фронту этого импульса устанавливается в состояние О триггер 5. Тем самым второй импульс частоты FB и следующие за ним проходят через логический элемент 8 и поступают на счетный вход счетчика 2. Содержимое счетчика 2.импульсо уменьшается. С приходом пятого импульса в счетчике 2 устанавливается крд (0100), совпадающий с кодом, при сутствующим на вторых входах блока 11. Имея на первых и вторых входах одинаковый код, блок 11 вырабатывает сигнал, который дважды сдвигается в блоке 9 на величину То/2. Так как в первом такте счета три гер 6 имеет состояние О, то к моменту сравнения кодов в подготовлен ном состоянии оказывается лишь один элемент совпадения логического блока 10, который и формирует сигнал в соответствии с формулой(7) по . совпадению импульса с выхода блока 11 и паузы входной последовательнос ти FO . Этот сигнал проходит через элемент сборки элемента 10 на выход 16. Одновременно счетчик 2 продолжает считать..С приходом девятого импульса входной частоты FO ,.который является последним в первом цикле счета, блок 3 определяет конечное состояние счетчика 2 и на его выхотце появляется сигнал, поступающийна входы триггеров 4 и 5 и на счетный вход триггера б. Состояния триг геров 4 и 6 изменяются по переднему фронту импульса с блока 3, а три гер 5 переключается по заднему фрон ту импульсов вхрдной частоты FO , ко торые поступаиот на его вход синхронизации. В соответствии с логически ми выражениями (4) и (5) на выходах логического элемента 8 формируются ; сигналы, совпадающие с паузой пйс- леднего в первом цикле счета периода частоты FO. Сигнал с выхода логического элемента 8 поступает на вход блока 1 установки и тем самым счетчик 2 возвращается в исходное состояние. Сигнал на выходе блока 3 пропадает. Поэтому по переднему фрон ту десятого импульса частоты возвращается в состояние О триггер 4, а по Зсщнему фронту - триггер 5. Триггер б сохраняет состояние 1. Десятый импульс частоты FQ является пер вым во втором цикле счета, который протекает аналогично первому.в части работы блоков 11 и 9. Но в свя зи с тем, что в данном цикле в момент сравнения кода счетчика 2 с кодом на шинах 14 триггер б находится в состоянии 1, сигнал на выходе 16 логического блока 10 формируется элементом совпгщения логического бло ка 10 по совпадению сигналов с прямого выхода триггера б, с выхода бло ка 9 и импульса входной частоты 1 (см.формулу 7). Если необходимо получить период выходных импульсов кратным периоду То входной частоты, то на дополнительную входную шину 13 подаете О. При этом триггер б блокируется по счетному входу и все время находится в состоянии О. В этом случае логическая формула 5 может быть записана в виде Uo UM-Uea-Fe(9) Блок 1, счетчик 2, блок 3, триггеры 4 - 6 и триггер 7 функционируют в калугом цикле так же, как в четных циклах рассмотренных выше примеров, т.е. импульс частоты следующий за последним в цикле счета, проходит на выход 17 триггера, но не проходит на выход 15 и не поступает на счетный вход счетчика 2 импульсов. 9 Исходя из вьооеприведенного анализа вариантов работы делителя частоты можно саелать вывод: на выходе 17 триггера 7 формируется выходная последовательность импульсов с периодом Т, определенным числом N{, дискретность иэАюнения периода Т-Т, /2; на выходе 18 логического блока 10 формируется вторая выходная последовательность импульсов с тем же периодом Т, задержанная относительно первой на величину €, задаваемую числом N), величина 1; изменяется с дискретностью То /2, в пределгис на выходе 19 триггера 11 вырабатывается третья выходная последовательность импульсов с периодом Т и длительностью импульса 1г . Таким образом, в предлагаемом делителе частоты следования импульсов введение несжольких дополнительных элементов обеспечивает формирование двух выходных последовательностей импульсов с pfeгyлиpye(Юй частотой и регулируемым в пределах О-ЗбО сдвигом по фаее между ними и (или) формирование выходной последовательности импульсов с регулируемой частотой и скважностью, причем все выходные последовательности строго равномерны, а дискретность иэменения регулируенфос параметров равна полупериоду входной частоты, что расширяет функциональные возможности устройства. Фсфмула изобретения Делитель частоты следования импульсов с переменным коэффициентом деления по авт.св. NI 809580,о тличающийся тем, что, с целью расширения функциональных возможностей, в него введены блок сравнения, элемент задержки, четвертый триггер и логический блок, включакяций в себя элемент сборки и четыре элемента совпадения,первые входы которых подключены к входной шине и первому входу элемента задержки, вторые входы - к кодовой шине младшего разряда, третьи входы первого и второго и третьи входы третьего и четвертого - к прямому и инверсному выходам третьего триггера, а четвертые входы первого, второго и третьего элементов совпадения логического блока и четвертый вход четвертого элемента совпадения логического блока- соответственно к выходам элемента эа,держки и к выходу блока сравнения, первая группа входов которого соединена с кодовыми шинами старших разрядов, вторая группа входов с выходами счетчика импульсов, а выход - с вторьлм входом элемента задержки, при этом первый вход четвертого триггера соединен с третьим выходом логического элемента, а второй вход - с выходом логического блока.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР №809580 по заявке 2747786/18-21, хзт 09.04.79.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следованияиМпульСОВ C пЕРЕМЕННыМ КОэффициЕН-TOM дЕлЕНия | 1979 |

|

SU809580A1 |

| Устройство для управления многофазным инвертором | 1978 |

|

SU955837A1 |

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1994 |

|

RU2084958C1 |

| Устройство для измерения параметров радиоимпульсов | 1980 |

|

SU938206A1 |

| Цифровой измеритель скважности прямоугольных импульсов | 1990 |

|

SU1725152A1 |

| Способ измерения фазового сдвига между двумя гармоническими сигналами и устройство для его осуществления | 1988 |

|

SU1596272A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1267601A1 |

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1990 |

|

SU1834548A1 |

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Фазоимпульсный преобразователь | 1983 |

|

SU1161977A1 |

Авторы

Даты

1981-12-30—Публикация

1980-05-07—Подача