ЬЭ

О)

а

Изобретение относится к импульс- ной технике и быть использовано в измерительной технике и в устройствах автоматики.

Цель изобретения - повьпиенивг точности.

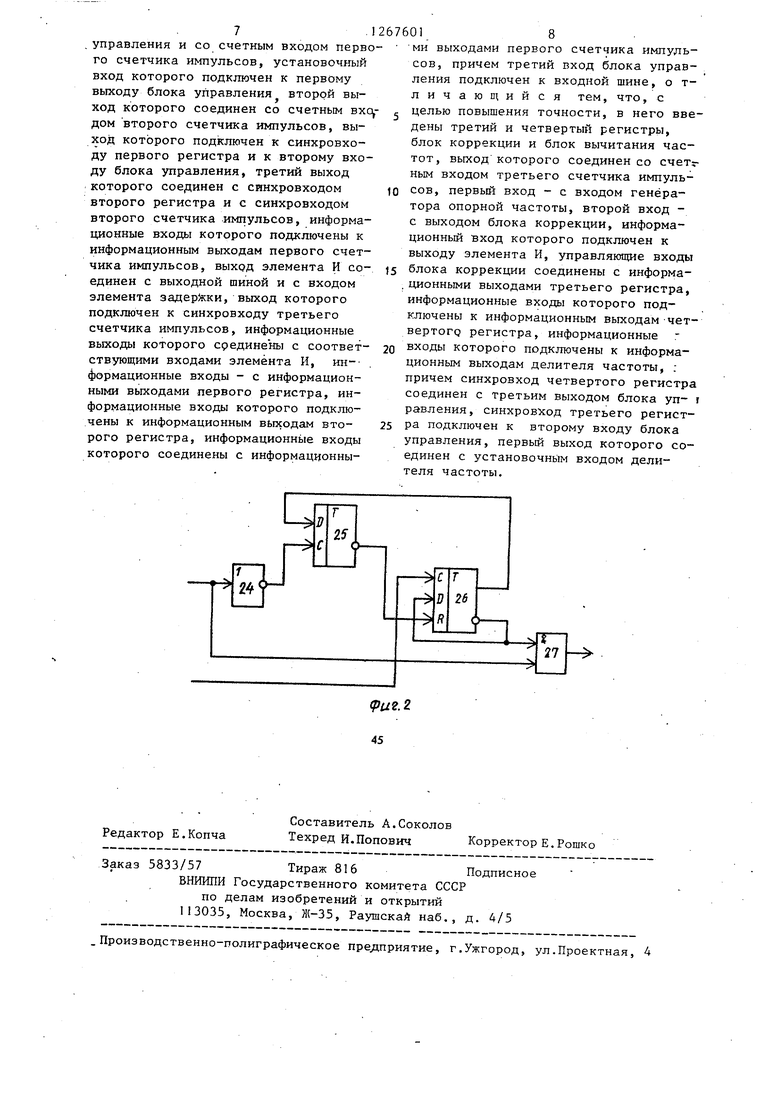

На фиг.1 изображена электрическая структурная схема умножителя частоты следования импульсов; на фиг.2 - , электрическая функциональная схема блока вычитания частот.

Устройство содержит генератор 1 опорной частоты, первый 2, второй 3, третий 4 счетчики импульсов, деотител 5 частоты, первый 6 и второй 7 регистры, элемент И 8, элемент 9 задержки, блок 10 управления, блок 11 коррекции, третий 12 и четвертьй 13 регистры, блок 14 вычитания частот, входную 15 и выходную 16 шины.

Выход генератора 1 опорной частоты соединен с первьм входом блока 14 вычитания частот и с входом делителя 5 частоты, выход которого подключен к счетному входу первого счетчика 2 импульсов и к первому входу блока 10 управления, первый выход ; которого соединен с установочным входом делителя 5 частоты и с установочным входом первого счетчика 2 импульсов, второй выход - со счетным входом второго счетчика 3 икпульсов, третий выход - с синхровходамй второго 7, четвертого 13 регистров и второго счетчика 3 импульсов, вы - .ход которого подключен к второму г входу блока 10 управления и синхровходу первого регистра 6, информационные входы которого соединены с информационными выходами второго регистра 7, информационные входы которого соединены с информационными входами второго счетчика 3 импульсов и с информационными выходами первого счетчика 2 импульсов,, Информационные выходы первого регистра 6 соединены с информационными входами третьего счетчика 4 импульсов, счетньй вход которого подключен к выходу блока 4 вычитания частот , а синхровход - к выходу элемента. 9 задержки, вход которого соединен с выходной 16 устройства, выходом элемента И 8 и с входом блока 11 коррекции, выход которого подключен к второму входу блока 14 вычитания частот, управляющие входы блока 11 коррекции соединены с информационными выходами третьего регистра 12, информационные входы которого подключены к информационным выходам четвертого регистра 13, информационные входы которого соединены

с информационными выходами делителя 5 частоты, причем третий вход блока 10 управления подключен к входной шине 15 устройства.

Блок IО управления содержит первый 17 и второй18 формирователи, триггер 19, элемент И 20. Первый вход блока IО управления соединен с первым входом элемента И 20, выход которого подключенг к второму выходу блока 10 управления, третий выход которого соединен с выходом пер« вого формирователя 17 и подключен к входу второго формирователя 18, выход которого соединен с первым

установочньм входом триггера 19 и с первым выходом блока 10 управления, второй вход КОТОРОГОподключен к второму установочному входу триггера 19, выход которого соединен с вторым

входом элемента И 20, причем третий вход блока 10 управления подключен к входу первого формирователя 17,

Блок 11 коррекции содержит счетчик 21 импульсов, элементы И 22-1,

,..,22-п, элемент И11И 23. Управляющие входы блока 1I коррекции соединены с первыми входами элементов 22-1,...,22-п выходы которых пЗДключены к соответствующим входам элемента 23 ИЛИ, выход которого соединен с выходом блока i коррекции, вход которого подключен к вторым входам элементов 22-1,...,22-п и к счетному входу счетчика 21 импульсов, информационные выходы которого соединены с третьими входами соответствующих элементов 22-,,.., 22-п.

Блок 14 вычитания частот содержит инвертор 24, два D-триггера 25 и 26, элемент И 27. Первьш вход блока 14 вычитания частот подключен к первому входу элемента И 27 и входу инвертора 24, выход KOTopoio соединен с синхровходом первого D-триггера 25, информационный вход которого подключен к прямому выходу второго D-триггера 26, синхровход которого подключен к второму входу блока 14 вычитания частот, выход которого соединен с выходом элемента И 27, второй вход кото рого соединен с информационным входом второго D-триггера 26 и с инверсным выходом последнего, установо ный вход которого соединен с инверсным выходом первого D-триггера 25. Блок 14 вычитания частот работает следующим образом. На первый вход блока 14 вычитания частот поступает опорная частота f , от генератора 1 , которая проходит через открытый элемент 27 на выход блока 14 вычитания частот. При переходе импульса на второй вход бло ка 14 вычитания частот D-триггер 26 взводится и элемент И 27 закрывается, уровень логической единицы поступает на информационный вход Dтриггера 25, который взводится инвер тированным импульсом f опорной частоты, а нуль с выхода D-триггера 25 сбрасывает D-триггер 26 в нулевое состояние, тем самым вновь открывает ся элемент И 27, следующим импульсом Го D-триггера 25 переводится в нулевое состояние, так как на его вход поступает уровень логического нуля с прямого выхода D-триггера 26. Следовательно, блок 14 выделения частот вырезает один импульс из последовательности fo , а затем возвращается в исходное состояние. Умножитель частоты следования им.пульсов работает следующим образом. Импульсная последовательность с частотой fx, (t) ff -X MClKt 2f. -XMMH соответствует динамическому диапазону, рекомендованному для первичных преобразователей) поступает на третий вход блока 10, а подается на вход формирователя 17 и через него на вход формирователя 18 Формирователь 17 формирует короткие прямоугольные импульсы по переднему фронту входных колебаний с частотой следования , равной частоте по ледних. -Формирователь 18 формирует короткие прямоугольные импульсы по заднему фронту импульсной последова тельности, поступающей с формирователя 17. Таким образом, на выходах формирователей 17 и 18 формируются импульсные последовательности с час тотой, соответствующей частоте вход ного сигнала, но сдвинутые друг относительно друга на время tn (t длительность импульса на выходе фор мирователя 17), причем-ТГц выбирается из условия , где to - период импульсов .опорной частоты с . выхода генератора 1 . Импульсы с выхода формирователя 17 поступают на синхровходы счетчика 3, регистров 7 и 13. Содержимое счетчика 2 переписывается в прямом коде в регистр 7 и в счетчик 3, а содержимое делителя 5 переписывается в регистр 13. Импульсы «с выхода формирователя 1В поступают на установочные входы счетчика 2, делителя 5 , устанавливая их в нулевое состояние, и на первый установочный вход триггера 19 блока 10 и тем самым взводят последний в единичное toстояние, что, в свою очередь, открывает элемент 20 блока 10. Таким образом, импульсы с генератора 1 поступают на вход делителя 5, коэффициент деления которого равен коэффициенту умножения устройства, и одновременно на первый вход блока 14, импульсы с выхода делителя 5 с частотой fo/M, где М - коэффициент умножения .устройства, поступают на счетный вход счетчика 2 и через элемент 20 блока 10 на счетный вход счетчика 3, работающего в режиме вьгчитания. Причем емкость счетчика 3 выбрана в два раза меньше, чем емкость счетчика 2 а разрядность и f - частота опорных импульсов - выбираются таким образом, чтобы периоду минимальной частоты Т „„ц соответствовал код 1000... О, т.е. единица в старшем разряде. Соответственно код периода максимальной частоты 0100 .. .0. Данное усло1иё позволяет синхронизировать два одновременно протекающих процесса в устройстве: кодирования и развертки кода. За период Т входного сигнала fJ (t) в счетчике 2 образуется код N периода входного сигнала. Значение N кода периода входного сигнала равно--.Ч-ъН где - целая часть числа -Чт. , Так как делитель 5, как и счетчик 2, перед каждым тактом кодирования сбрасывается в нулевое состояние, то к концу периода Тк в делителе 5 образуется некоторое значение кода N, равное ,- ()J М, По окончании периода TXL сигнало с третьего выхода блока 10 код N; переписывается в. регистр 7 и счетчик 3, а код 4N; - в регистр 13.. -В момент кодирования Ту (при условии Tyj; Ty;+j ) на выходе счетчик 3 формируется импульс, которыр1 пере писывает содержимое (N| ) регистра 7 в регистр 6, содержимое (iN;) регис ра 13 - в регистр 12 и сбрасывает в нуль триггер 19 блока 10. Счетчик 4 элемент 8 и элемент 9 задержки объе динены функционально в узел разверт ки кода, т.е. осуществляют генерацию импульсной последовательности с час тотой в М раз больше исходной. К мо менту появления импульса на выходе элемента 9 задержки (время задержки выбирается равным времени достаточно го для формирования полноценного импульса выходной послёдовательности) в регистре 6 уже находится кодовый эквивалент текущего периода. Сиг нал с выхода элемента 9 задержки обеспечивает перезапись содержимого регистра 6, т.е. значения N , в счет чик 4, после чего начинается процесс развертки кода. Если лК О, то элементы 22-i, ,..,22-п блока II закрыты и частота на вкгходе блока 1 1 равна нулю, так как частота на выходе данного блока определяется соотношением частота на выходе блока I значение кода в регистре 12; частота, подаваемая на вход счетчика 21 блока 1 разрядность счетчика 21, Частота на выходе блока 14 равна (fg-fg ), поэтому при дЫ 0 импульсы с генератора 1 поступают на вход счетчика 21, на развертку кода N;. В результате частота сигнала на шине 16 равна f f /м f . м бык -1-0/1 1 f,t - . Очевидно, что период сигнала на выходе устройства равен Т, /М только при . Если , то для повышения точности умножения необходимо осуществлять коррекцию периода следования AN импульсов на выходе устройства, причем эта коррекция должна осуществляться равномерно за время Ту . Еели, например, величина коэффициента . умножения М 64 и AN 8, то коррекций подлежит каждьй восьмой им- пульс на выходе устройства. Коррекция при этом заключается в увеличении периода следйвания каждого восьмого импульса на величину t, . Счетчик 21 блока II имеет, как и делитель 5, коэффициент деления М. Поэтому при поступлении на вход счетчика 21 М импульсом на вькоде блока I1 формируется лЫ импульсов, каждый из которых запрещает прохождение очередного импульса с генератора 1 через блок 14 на вход счетчика 4. Это означает увеличение периода спедования импульсов на выходе устройства на величину tp При .скачке входного сигнала от Т макс Тмин в момент окончания периода Т„„„ импульсом с блока 10 кодовый эквивалент переписывается в счетчик 3 и регистр 7, а код лЫ|-|,„в регистр 13. Затем начинается процесс кодирования следующего периода. Импульсная последовательность fe/M поступает на входы счетчиков 2 и 3, а импульсная последовательность f. с генератора I через блок 14 - на вход счетчика 3, где происходит развертка и корекция периода Т.. . Содержимое счетчика 4 уменьшается до нуля, а затем первый же импульс обеспечивает формирование на выходе счетчика 3 импульса, который записьшаетодержимое регистра 7 в регистр 6, а содержимое регистра 13 - в регистр 12. К этому времени заканчивается процесс развертки и коррекции кода максимального периода Т„д . Импульсы с выхода элемента 9 обеспечивают перезапись содержимого регистра 6 в счетчик 4, т.е. устройство осуществляет полную развертку кода и подготавливает к началу очередного процесса развертки и коррекции новое значение кода периода. В случае скачка входного сигнала от Т„,„ к работа устройства происходит аналогично. Формула изобретения Умножитель частоты следования импульсов, содержащий генератор опорной частоты, выход которого подключен к входу делителя частоты, выход которого соединен с первым входом блока

7

управления и со счетным входом первого счетчика импульсов, установочный вход которого подключен к первому выходу блока управления второй выход которого соединен со счетным вхс дом второго счетчика импульсов, выход которого подключен к синхровходу первого регистра и к второму входу блока управления, третий выход которого соединен с сйнхровходом второго регистра и с сйнхровходом второго счетчика импульсов, информационные входы которого подключены к информационным выходам первого счетчика импульсов, выход элемента И соединен с выходной шиной и с входом элемента задерйски, выход которого подключен к синхровходу третьего счетчика импульсов, информационные выходы которого срединены с соответствующими входами элемента И, информационные входы - с информационными выходами первого регистра, информационные входы которого подключены к информационным выходам второго регистра, информационные входы которого соединены с информационны676018

ми выходами первого счетчика импульсов, причем третий вход блока управления подключен к входной шине, о тличающийся тем, что, с целью повышения точности, в него введены третий и четвертый регистры, блок коррекции и блок вычитания частот, выход которого соединен со счетг ным входом третьего счетчика импуль 0 сов, первый вход - с входом генератора опорной частоты, второй вход с выходом блока коррекции, информационный вход которого подключен к выходу элемента И, управляющие входы {5 блока коррекции соединены с информа. ционными выходами третьего регистра, информационные входы которого подключены к информационным выходам-четвертогр регистра, информационные 20 входы которого подключены к информационным выходам делителя частоты, : причем синхровход четвертого регистра соединен с третьим выходом блока уп- f равления, синхровход третьего регист25 ра подключен к второму входу блока управления, первый выход которого соединен с установочным входом делителя частоты.

(pU2.2 45

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1981 |

|

SU976482A1 |

| Устройство для измерения частоты | 1988 |

|

SU1550434A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU993451A1 |

| Умножитель частоты | 1983 |

|

SU1176439A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1081783A1 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Устройство для измерения частоты | 1983 |

|

SU1170373A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Умножитель частоты | 1987 |

|

SU1499341A1 |

Изобретение может быть использовано в измерительной технике. Цель изобретения - повьшение точности. Умножитель содержит генератор 1 опорной частоты, счетчики 2, 3 и 4 импульсов, делитель 5 частоты, регистры 6 и 7 , элемент И 8, элемент 9 задержки и блок IО управления. Введение блока I1 коррекции, регистров 12 и 13, блока 14 вычитания частот и образование новых связей между элементами устройства способствует достижению поставленной цели. 2 ил. If (Л С

| Умножитель частоты следования импульсов | 1982 |

|

SU1027830A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU898600A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU976482A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-10-30—Публикация

1985-04-09—Подача