1

Изобретение относится к вычислительной технике, в частности к устройствам для обслуживания запросов, и может быть использовано для управления очередностью обращения нескольких потребителей к нескольким коллективно используемым ресурсам.

Известно устройство для обслуживания запросов, содержащее счетчики записи и считывания и в каждом канале - регистр, схему сравнения, элементы И и триггер 1. Устройство характеризуется ограниченными функциональными возможностями, поскольку способно обслуживать системы только с одним исходящим каналом и, кроме того, требует для своей работы источник синхроимпульсов.

Известно устройство для обслуживания запросов, которое выполнено в виде матрицы из однотипных ячеек и схемы управления 2. Входы и выходы устройства соединены с входами и выходами ячеек первой строки. Выходы ячеек последних И строк последнего столбца соединены со своими входами этих ячеек. Кроме того, выходы всех ячеек последнего столбца соединены через элементы схемы управления со своими входами этих ячеек. Каждая ячейка соединена с соседней тремя связями. Ячейка матрицы содержит три коммутатора

единиц и схему управления ячейкой, содержащую элементы И, ИЛИ, инвертор. Входы схемы управления ячейкой соединены со своими входами коммутаторов единиц, а выход - с входами управления этих коммутаторов.

Сложность этого устройства обусловлена большим количеством логических элементов, необходимых для построения ячеек матрицы, а его низкое быстродействие обусловлено структурой устройства, при которой управляющий сигнал на выходе устройства появляется только после того, как требование пройдет через свои ячейки матрицы сначала в одном направлении, затем- в противоположном.

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для обслуживания запросов, содержащее блок управления и коммутатор, выполненный в виде матрицы из однотипных переключательных элементов, группу элементов И, регистр запросов, блок крепления кодов приоритетов, причем каждый переключательный элемент содерлчит дешифратор и два элемента И 3.

Цель изобретения - упрощение устройства.

Достигается это тем, что в устройство для обслуживания запросов, содержащее блок управления и коммутатор, который выполнен в виде матрицы переключательных узлов, причем каждый переключательный узел содержит два элемента И, выходы которых соединены соответственно с первым и вторым выходами узла, первые входы переключательных узлов первого столбца матрицы являются запросными входами устройства, первый выход переключательного узла строки матрицы соединен с первым входом последующего переключательного узла той же строки матрицы, вторые входы переключательпых узлов первого столбца матрицы соединены с блокирующим выходом блока управления, вторые выходы переключательпых узлов столбца матрицы (кроме первого столбца) соединены с соответствующей группой информационных входов блока управления, вторые входы переключательных узлов столбца матрицы соединены с соответствующим дополнительным блокирующим выходом блока управления, первые выходы переключательных узлов последнего столбца матрицы соединены с группой фиксирующих входов блока управления, первые выходы переключательных узлов предпоследнего столбца матрицы являются выходами устройства, а каледый переключательный узел содержит элемент ИЛИ и элемент НЕ, причем первый вход переключательного узла соединен с первыми входами первого и второго элементов И узла, второй вход переключательного узла и выход первого элемента И узла через элемент ИЛИ узла соединены с вторым входом первого элемента И узла и через элемент НЕ узла - с вторым входом второго элемента И узла.

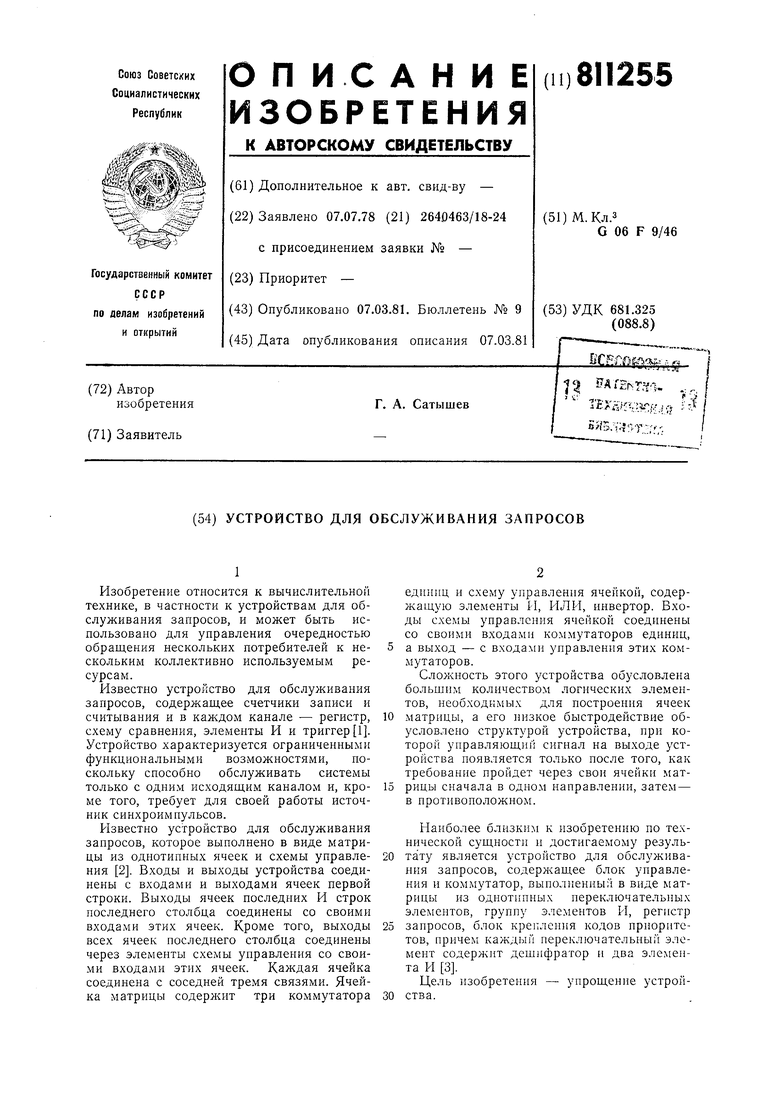

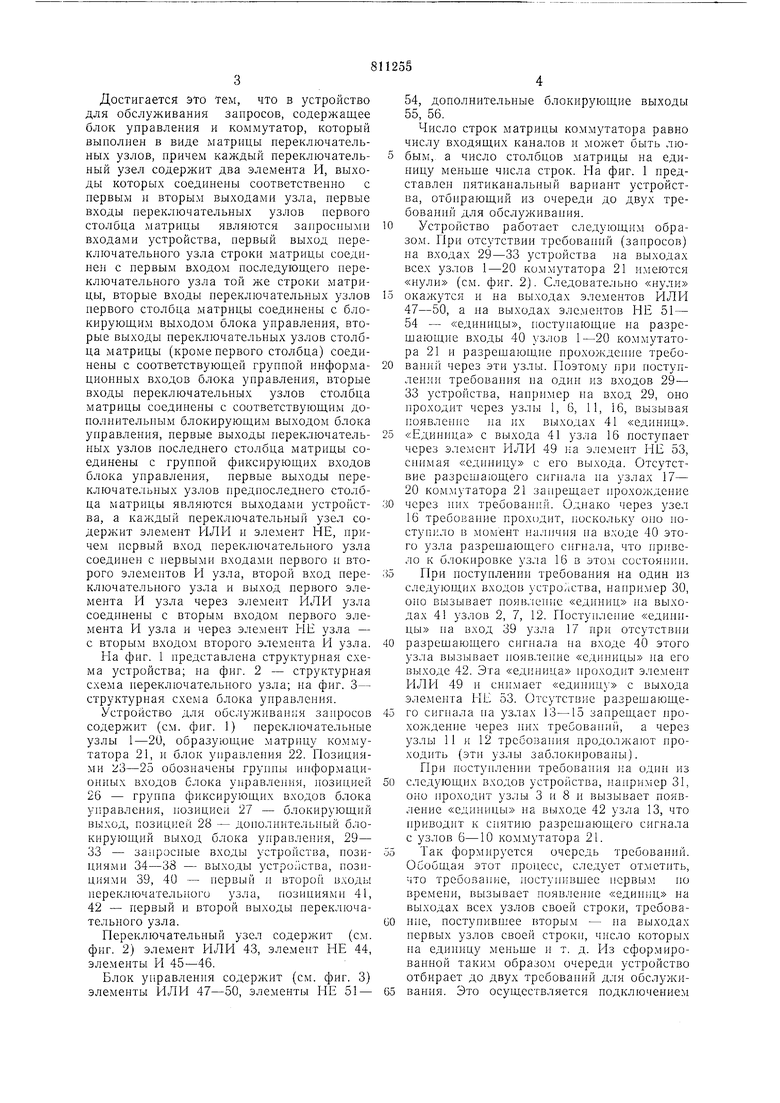

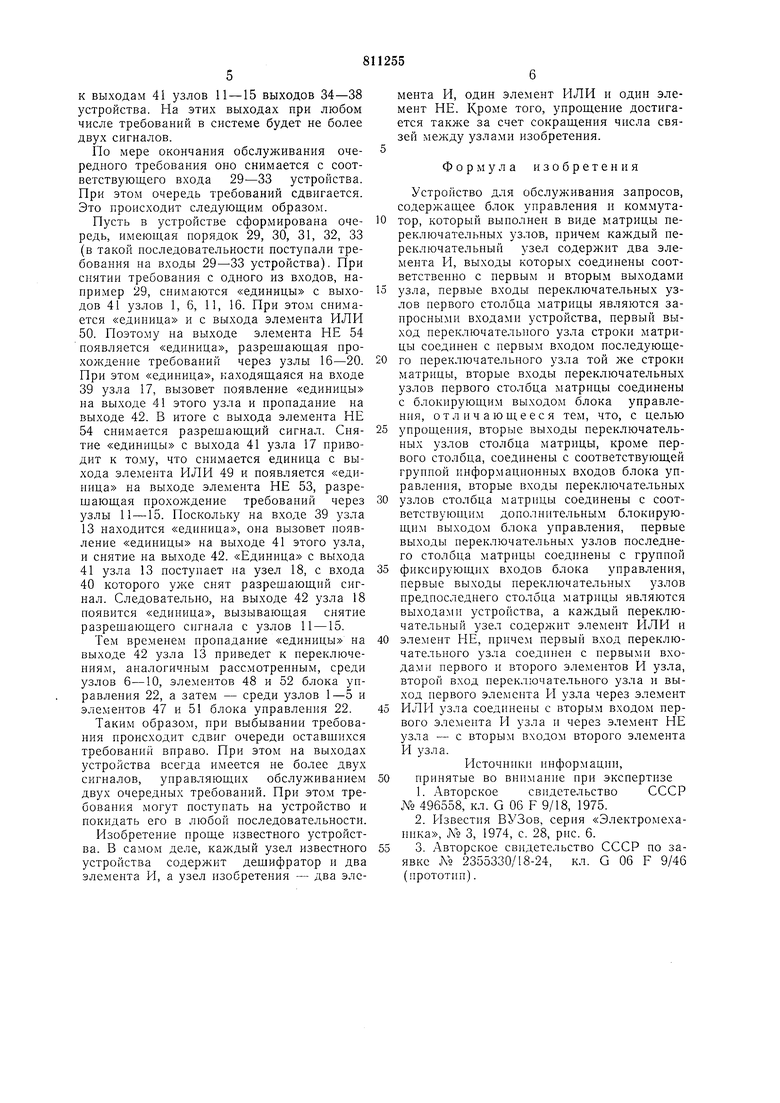

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема переключательного узла; на фиг. 3- структурная схема блока управления.

Устройство для обслуживания запросов содержит (см. фиг. 1) переключательные узлы 1-20, образующие матрицу коммутатора 21, и блок управления 22. Нозициями 23-25 обозначены группы информационных входов блока управления, позицией 26 - группа фиксирующих входов блока управления, позицией 27 - блокирующий выход, позицией 28 - дополнительный блокирующий выход блока управления, 29- 33 - запросные входы устройства, позициями 34-38 - выходы устройства, позициями 39, 40 - первый и второй входы переключательного узла, позициями 41, 42 - первый и второй выходы переключательного узла.

Нереключательный узел содержит (см. фиг. 2) элемент ИЛИ 43, элемент НЕ 44, элементы И 45-46.

Блок управления содержит (см. фиг. 3) элементы ИЛИ 47-50, элементы НЕ 51 -

54,дополнительные блокирующие выходы

55,56.

Число строк матрицы коммутатора равно числу входящих каналов и может быть любым,. а число столбцов матрицы на единицу меньще числа строк. На фиг. 1 представлен пятиканальный вариант устройства, отбирающий из очереди до двух требований для обслуживания.

Устройство работает следующим образом. При отсутствии требований (запросов) на входах 29-33 устройства на выходах всех узлов I-20 коммутатора 21 имеются «нули (см. фиг. 2). Следовательно «нули

окажутся и на выходах элементов ИЛИ 47-50, а на выходах элементов НЕ 51- 54 - «единицы, поступающие на разрешающие входы 40 узлов 1-20 коммутатора 21 и разрешающие прохождение требований через эти узлы. Ноэтому при поступлении требовапия на один из входов 29- 33 устройства, например па вход 29, оно проходит через узлы 1, 6, И, 16, вызывая появление на их выходах 41 «единиц.

«Единица с выхода 41 узла 16 поступает через элемент ИЛИ 49 па элемент НЕ 53, снимая «единицу с его выхода. Отсутствие разрешающего сигнала на узлах 17- 20 коммутатора 21 запрещает прохождение

через них требований. Однако через узел 16 требование проходит, поскольку оно поступило в момент наличия на входе 40 этого узла разрешающего сигнала, что привело к блокировке узла 16 в этом состоянии.

При поступлении требования на один из следующих входов устройства, например 30, оно вызывает появление «единиц на выходах 41 узлов 2, 7, 12. Поступление «единицы на вход 39 узла 17 при отсутствии

разрешающего сигнала на входе 40 этого узла вызывает появление «единицы на его выходе 42. Эта «единица проходит элемент ИЛИ 49 и снимает «единицу с выхода элемента НЕ 53. Отсутствие разрешающего сигнала на узлах 13-15 запрещает прохождение через них требований, а через узлы 11 и 12 требования продол кают проходить (эти узлы заблокированы).

При поступлении требования на один из

следующих входов устройства, например 31, оно проходит узлы 3 и 8 и вызывает появление «единицы на выходе 42 узла 13, что приводит к снятию разрешающего сигнала с узлов 6-10 коммутатора 21.

Так формируется очередь требований. Обобщая этот процесс, следует отметить, что требование, поступившее первым по времени, вызывает появление «единиц на выходах всех узлов своей строки, требование, иоступившее вторым - на выходах первых узлов своей строки, число которых на единицу меньше и т. д. Из сформированной таким образом очереди устройство отбирает до двух требований для обслул ивания. Это осуществляется подключением

к выходам 41 узлов 11-15 выходов 34-38 устройства. На этих выходах при любом числе требований в системе будет не более двух сигналов.

По мере окончания обслуживания очередного требования оно снимается с соответствующего входа 29-33 устройства. При этом очередь требований сдвигается. Это происходит следующим образом.

Пусть в устройстве сформирована очередь, имеющая порядок 29, 30, 31, 32, 33 (в такой последовательности поступали требования на входы 29-33 устройства). При снятии требования с одного из входов, например 29, снимаются «единицы с выходов 41 узлов 1, 6, 11, 16. При этом снимается «единица и с выхода элемента ИЛИ 50. Поэтому на выходе элемента НЕ 54 появляется «единица, разрещающая прохоледение требований через узлы 16-20. При этом «единица, находящаяся на входе

39узла 17, вызовет появление «единицы на выходе 41 этого узла и пропадание на выходе 42. В итоге с выхода элемента НЕ 54 снимается разрешающий сигнал. Снятие «единицы с выхода 41 узла 17 приводит к тому, что снимается единица с выхода элемента ИЛИ 49 и появляется «единица на выходе элемента НЕ 53, разрещающая прохождение требований через узлы 11 -15. Поскольку на входе 39 узла 13 находится «единица, она вызовет появление «единицы на выходе 41 этого узла, и снятие на выходе 42. «Единица с выхода 41 узла 13 поступает на узел 18, с входа

40которого уже снят разрешающий сигнал. Следовательно, на выходе 42 узла 18 появится «единица, вызывающая снятие разрешающего сигнала с узлов 11 -15.

Тем временем пропадание «единицы на выходе 42 узла 13 приведет к переключениям, аналогичным рассмотренным, среди узлов 6-10, элементов 48 и 52 блока управления 22, а затем - среди узлов 1-5 и элементов 47 и 51 блока управления 22.

Таким образом, при выбывании требования происходит сдвиг очереди оставшихся требований вправо. При этом на выходах устройства всегда имеется не более двух сигналов, управляющих обслуживанием двух очередных требований. При этом требования могут поступать на устройство и покидать его в любой последовательности.

Изобретение проще известного устройства. В самом деле, каждый узел известного устройства содержит дешифратор и два элемента И, а узел изобретения - два элемента И, один элемент ИЛИ и один элемент НЕ. Кроме того, упрощение достигается также за счет сокращения числа связей между узлами изобретения.

Формула изобретения

Устройство для обслуживания запросов, содержащее блок управления и коммутатор, который выполнен в виде матрицы переключательных узлов, причем каждый переключательный узел содержит два элемента И, выходы которых соединены соответственно с первым и вторым выходами

узла, первые входы переключательных узлов первого столбца матрицы являются запросными входами устройства, первый выход переключательного узла строки матрицы соединен с первым входом последующего переключательного узла той же строки матрицы, вторые входы переключательных узлов первого столбца матрицы соединены с блокирующим выходом блока уцравления, отличающееся тем, что, с целью

упрощения, вторые выходы переключательных узлов столбца матрицы, кроме первого столбца, соединены с соответствующей группой информационных входов блока управления, вторые входы переключательных

узлов столбца матрицы соединены с соответствующим дополнительным блокирующим выходом блока управления, первые выходы переключательных узлов последнего столбца матрицы соединены с группой

фиксирующих входов блока управления, первые выходы переключательных узлов предпоследнего столбца матрицы являются выходами устройства, а каждый переключательный узел содержит элемент ИЛИ и

элемент НЕ, причем первый вход переключательного узла соединен с первы.ми входами первого и второго элементов И узла, второй вход переключательного узла и выход первого элемента И узла через элемент

ИЛИ узла соединены с вторым входом первого элемента И узла и через элемент НЕ узла - с вторым входом второго элемента И узла.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 496558, кл. G 06 F 9/18, 1975.

2.Известия ВУЗов, серия «Электромехапика, № 3, 1974, с. 28, рис. 6.

3. Авторское свидетельство СССР по заявке № 2355330/18-24, кл. G 06 F 9/46 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления очередностьюОбСлужиВАНия | 1978 |

|

SU805311A1 |

| Умножитель разреженных полиномов | 1989 |

|

SU1649564A1 |

| Устройство управления переключением резерва | 1988 |

|

SU1617675A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРОВ | 1991 |

|

RU2006931C1 |

| ПЕРЕКЛЮЧАТЕЛЬНАЯ МАТРИЦА | 1973 |

|

SU375642A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Микропроцессорное устройство для моделирования систем массового обслуживания | 1984 |

|

SU1196886A1 |

| Устройство для ввода-вывода аналоговых сигналов | 1981 |

|

SU1015369A1 |

Авторы

Даты

1981-03-07—Публикация

1978-07-07—Подача