Изобретение относится к вычислительной технике и может быть использовано при разработке многопроцессорных систем, в частности мультимикропроцессорных.

Известна система коммутации процессоров [1] , содержащая матрицу N, (N+1) коммутаторов данных, где N - количество коммутируемых процессоров, матрицу мультиплексоров адреса, матрицу мультиплексоров управления и матрицу N, (N+2) блоков памяти.

Недостатком известного устройства является сложность его технической реализации.

Наиболее близким по технической сущности к заявляемому (прототипом) является система коммутации процессоров [2] , содержащая матрицу N, (N+1) коммутаторов данных, где N - количество коммутируемых мультиплексоров, матрицу мультиплексоров адреса, матрицу мультиплексоров управления, матрицу N, (N+2), блоков памяти, N контроллеров обмена, два блока управления режимом и элемент И.

Недостатком прототипа являются ограниченные функциональные возможности, заключающиеся в невозможности решения задач, не полностью поддающихся распараллеливанию, т. е. задач, при решении которых N микроЭВМ производит только часть необходимых операций, оставшаяся часть операций может быть выполнена только одной микроЭВМ. Система-прототип, решая полностью распараллеленные задачи, не может реализовать нераспараллеленный режим работы из-за отсутствия аппаратных средств синхронизации начала передачи данных от микроЭВМ, осуществляющей нераспараллеленный режим работы, в оставшиеся микроЭВМ системы при переходе к параллельному режиму работы системы. Это сужает область применения системы-прототипа; кроме того, невозможно конструктивно полностью закончить исполнение отдельных микроЭВМ, входящих в систему-прототип, что не позволяет использовать отдельные микроЭВМ в автономном режиме для решения простых задач. Это ограничение связано, с одной стороны, с наличием только одного синхрогенератора и одного блока сброса на всю систему и, с другой стороны, с наличием элементов, которые трудно отнести к какой-либо микроЭВМ, не нарушив идентичности технической реализации этих микроЭВМ (это затрудняет изготовление и использование таких микроЭВМ). К таким элементам относятся элементы И. Указанное ограничение также сужает область применения системы-прототипа.

Наблюдаются трудности в подготовке задачи к решению, обусловленные тем, что программа должна быть создана (скомпилирована) в одной из микроЭВМ системы и только затем вручную введена в оставшиеся микроЭВМ, так как в системе-прототипе отсутствуют аппаратные средства синхронизации начала передачи программы из одной микроЭВМ системы в другие микроЭВМ.

Цель изобретения - повышения быстродействия за счет решения не полностью распараллеливаемых задач.

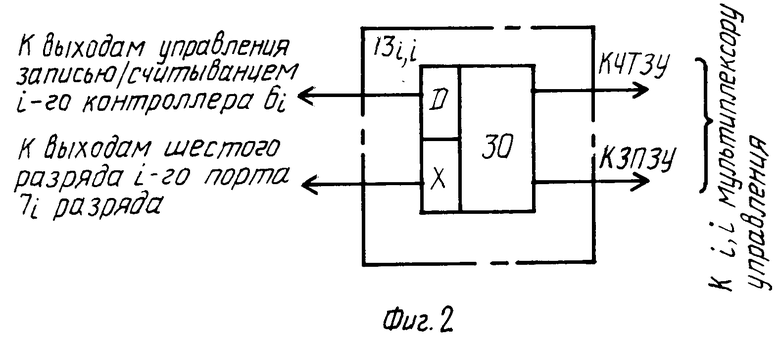

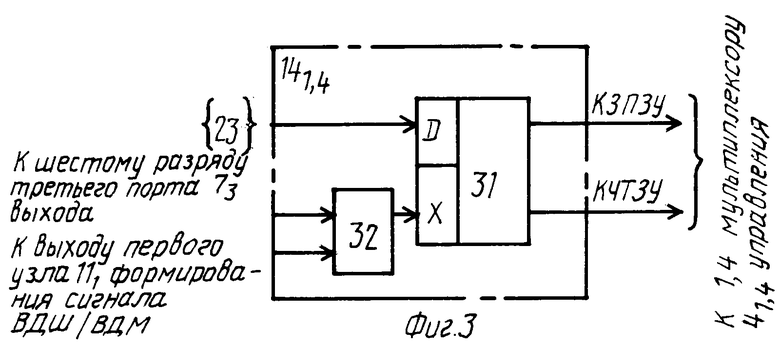

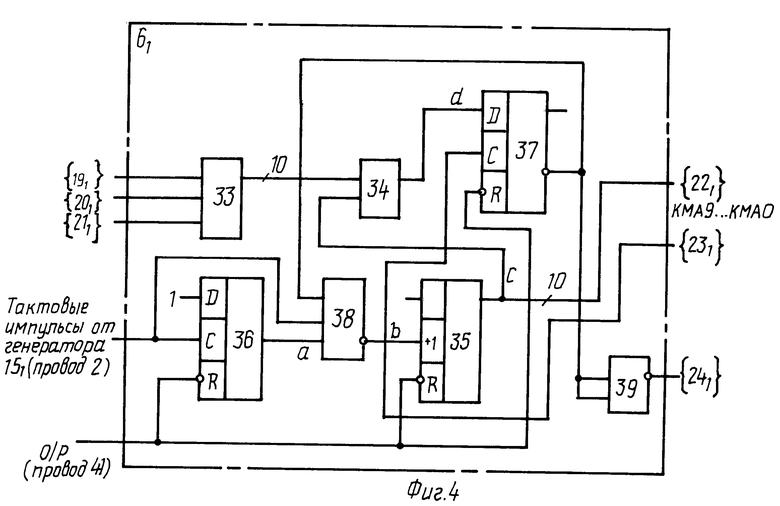

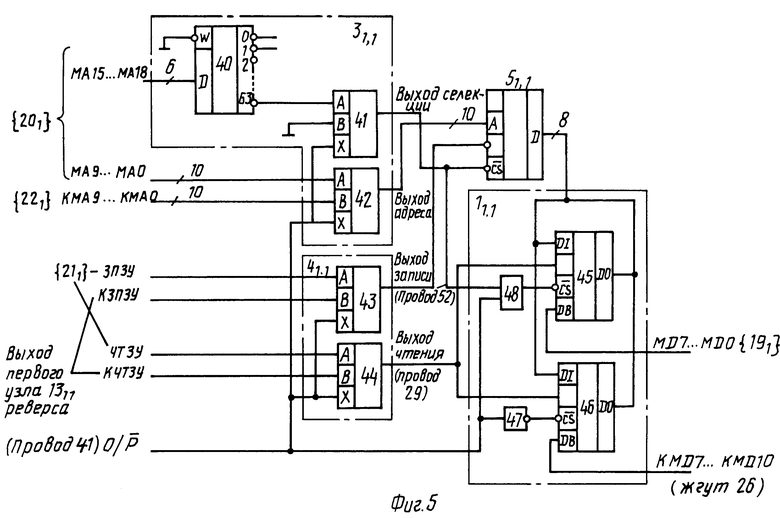

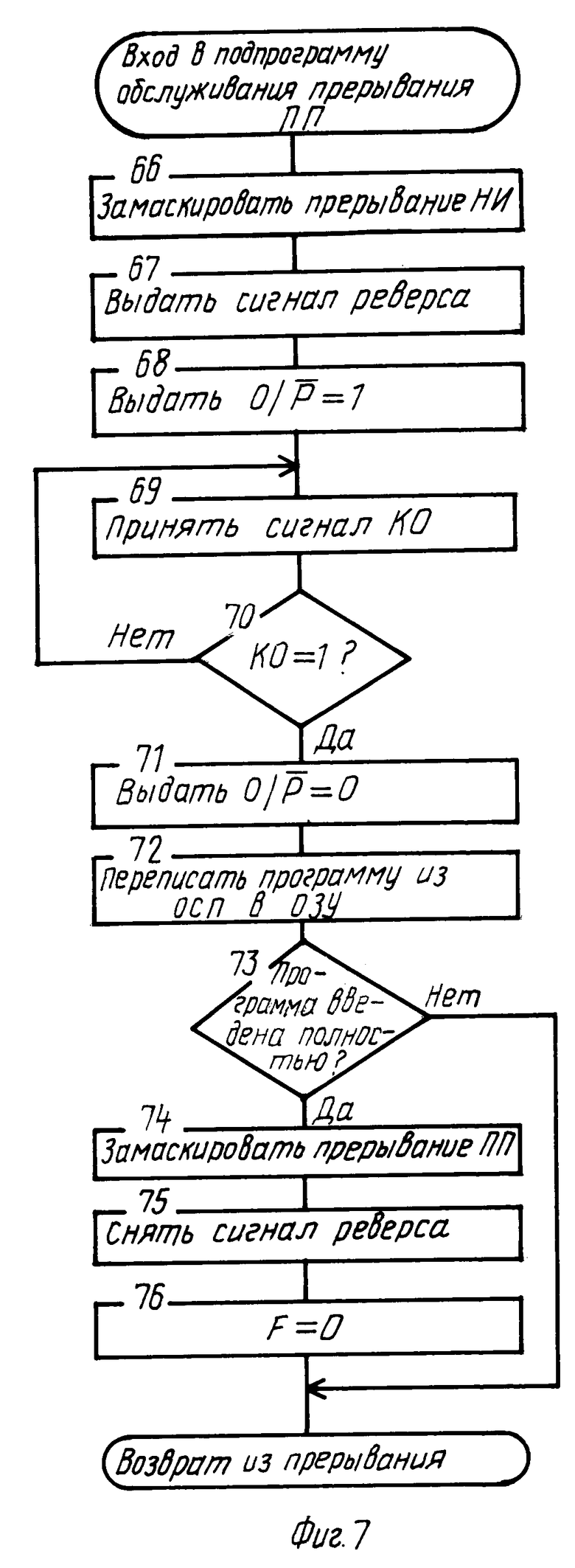

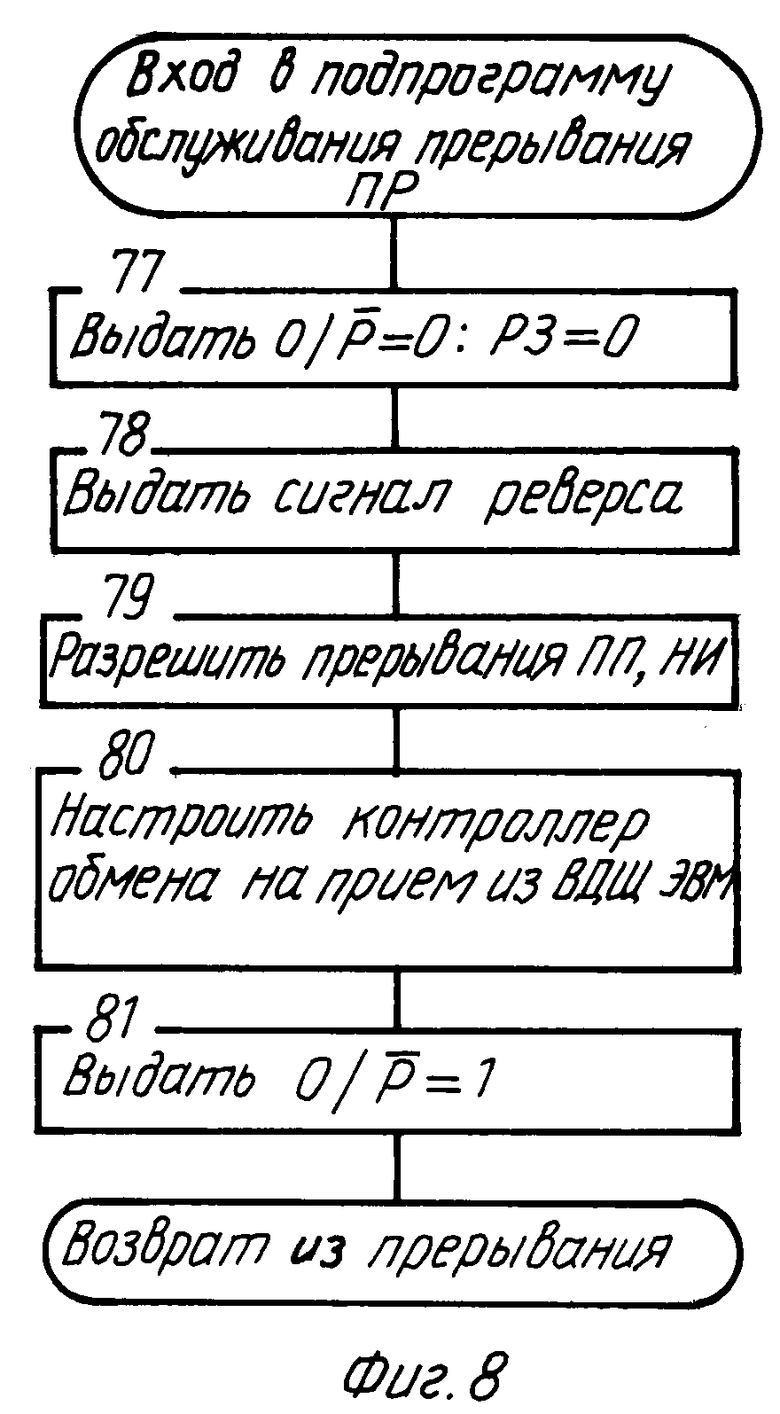

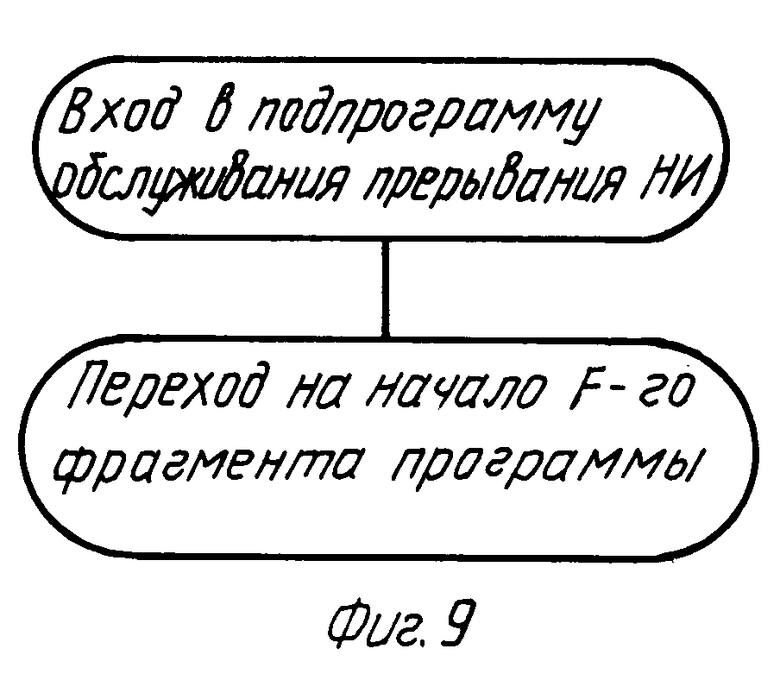

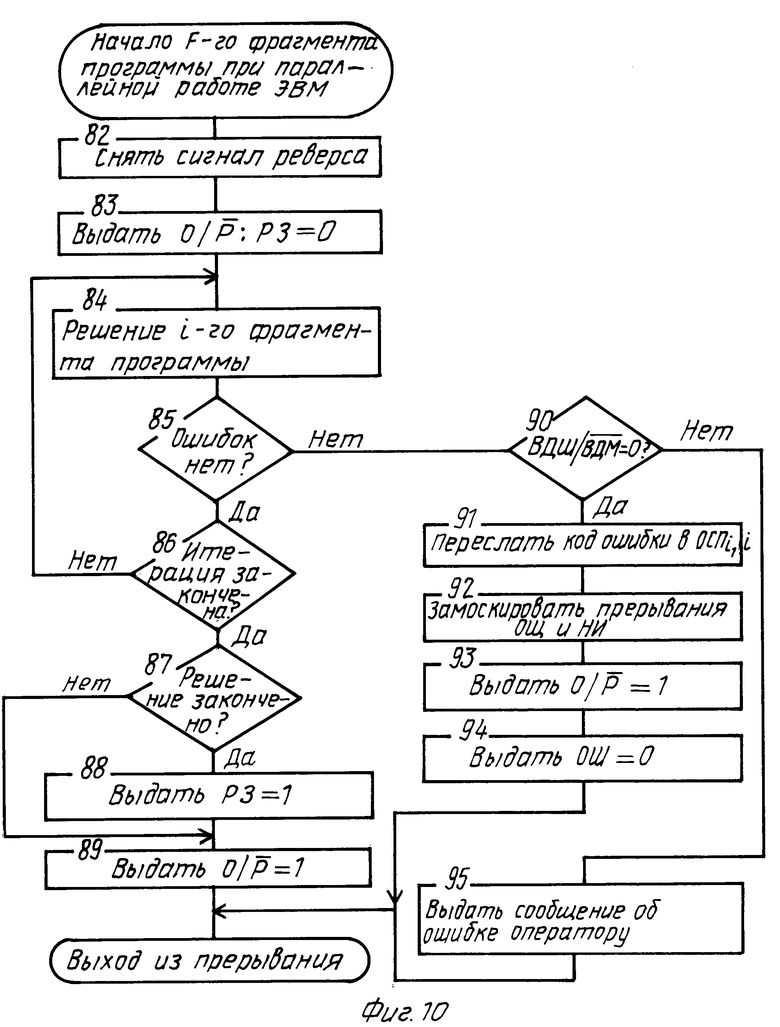

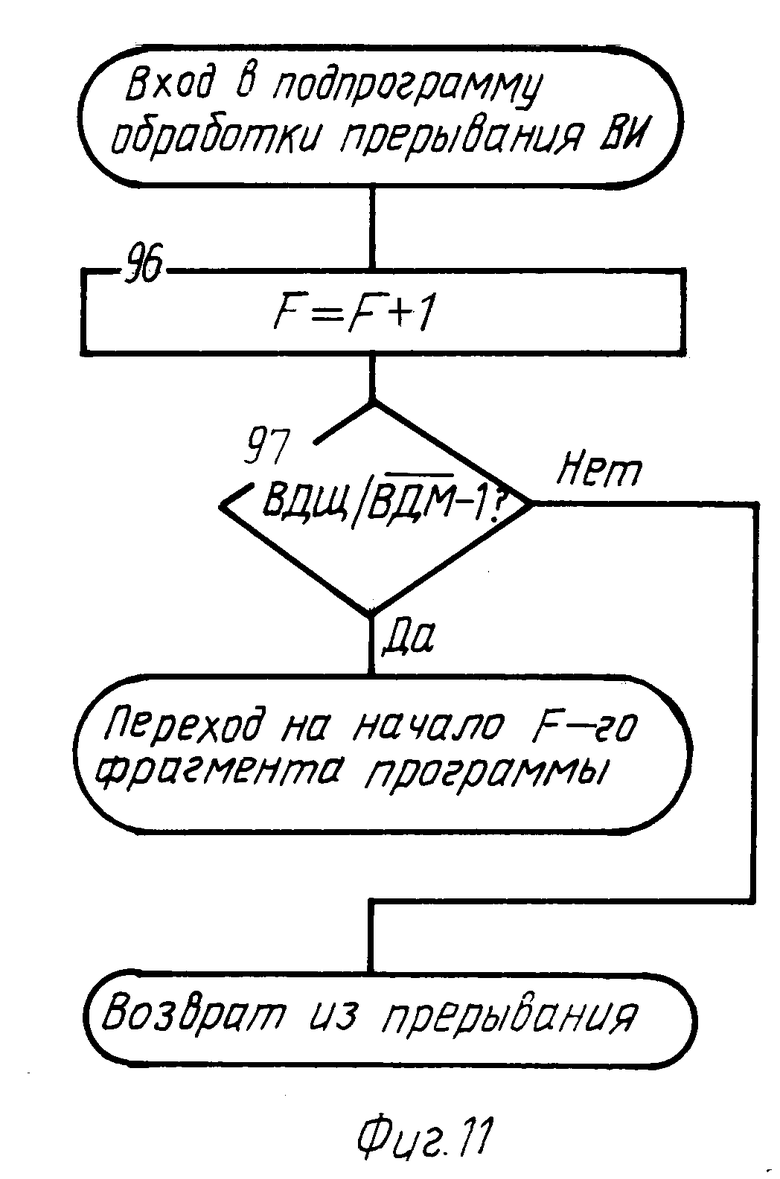

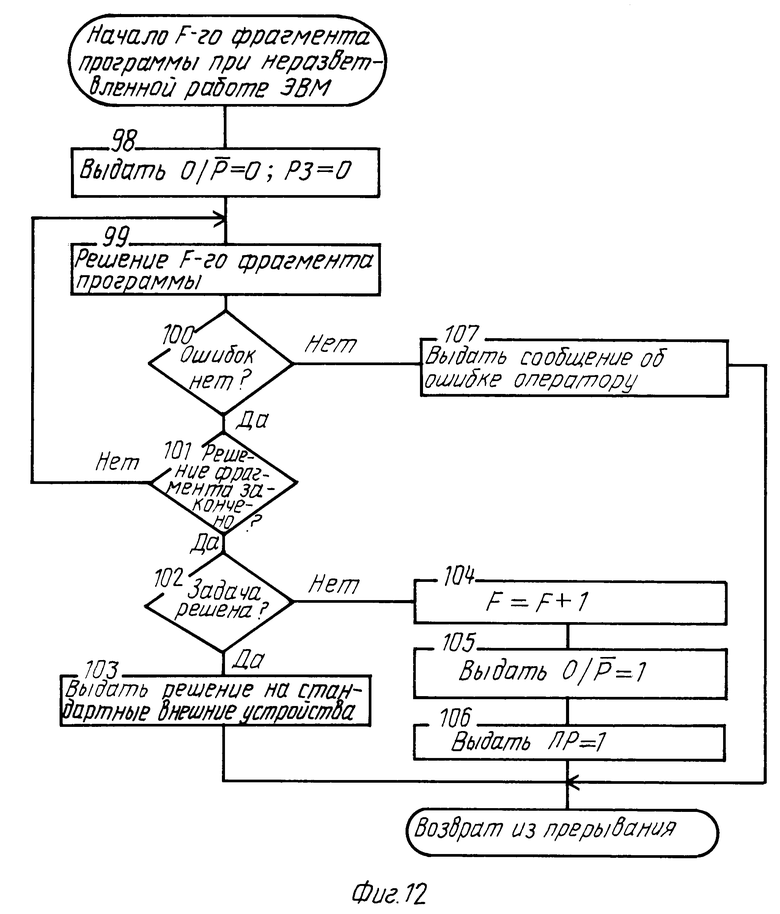

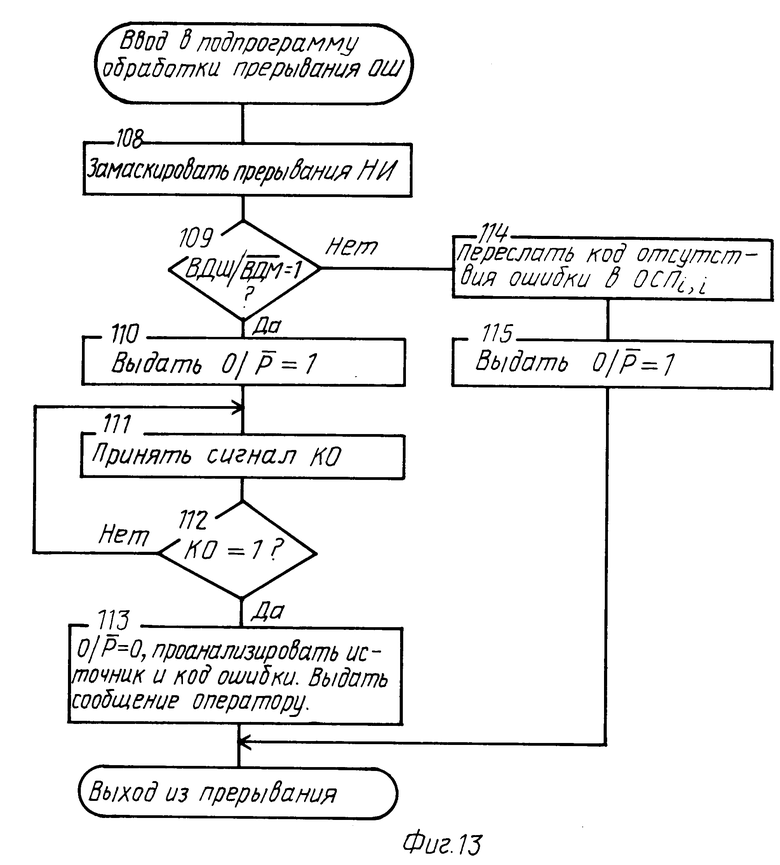

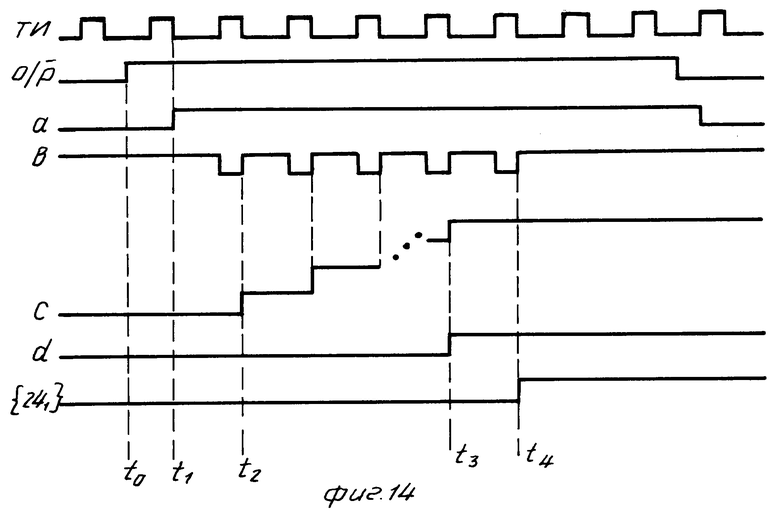

На фиг. 1 представлена функциональная схема системы коммутации при н = 3; i = 1-3; j = 1-5; на фиг. 2, 3 - принципиальная схема используемых демультиплексоров; на фиг. 4 - функциональная схема устройства управление обменом; на фиг. 5 - пример конкретного выполнения коммутаторов для трех матриц коммутаторов; на фиг. 6 - алгоритм функционирования i-й микроЭВМ системы; на фиг. 7 - блок-схема подпрограммы обслуживания прерывания ПРИНЯТЬ ПРОГРАММУ (ПП); на фиг. 8 - блок-схема подпрограммы обслуживания прерывания ПРОДОЛЖИТЬ РЕШЕНИЕ (ПР); на фиг. 9 - блок-схема подпрограммы обслуживания прерывания НАЧАТЬ ИТЕРАЦИЮ (НИ); на фиг. 10 - структура F-го фрагмента программы при параллельной работе микроЭВМ системы; на фиг. 11 - блок-схема подпрограммы обслуживания прерывания ВЫЙТИ ИЗ ИТЕРАЦИИ (ВИ); на фиг. 12 - структура F-го фрагмента программы при неразветвленной работе микроЭВМ системы; на фиг. 13 - блок-схема подпрограммы обслуживания прерывания ОШИБКА; на фиг. 14 - временные диаграммы устройств управления обменом.

Рассмотрим пример конкретного выполнения заявляемого объекта для количества коммутируемых процессоров, равного трем (N = 3).

Система коммутации процессоров (см. фиг. 1) содержит первую матрицу 3х4 коммутаторов 1 процессоры 21, 22, 23, вторую матрицу 3х4 коммутаторов 3 адреса, третью матрицу 3х4 коммутаторов 4, матрицу 3х5 блоков 5 памяти, устройства управления 61, 62, 63 обменом, блоки 71, 72, 73 вывода, блоки 81, 82, 83 ввода, демультиплексоры 91, 92, 93 группы, инверторы 101, 102, 103, узлы формирования 111, 112, 113 сигнала ВЕДУЩАЯ/ВЕДОМАЯ (ВДЩ/ВДМ), узлы формирования 121, 122, 123 сигнала АВТОНОМНО/СИСТЕМА (АВТ/СИС), матрицы Нх(Н+1) демультиплексоров, синхрогенераторы 151, 152, 153 и блоки 161, 162, 163 сброса.

Работает система следующим образом. Каждая строка первой матрицы коммутаторов, например, 11.1, 11.2, 11.3, 11.4, вторая матрица 31.1, 31.2, 31.3, 31.4 коммутаторов, третья матрица коммутаторов 41.1, 41.2, 41.3, 41.4, блоков 51.1, 51.2, 51.3, 51.4, 51.5 памяти совместно с процессором 21 и контроллером 61 обмена образует 1-ую микроЭВМ. Остальные микроЭВМ полностью идентичны 1-й, закончены в схемотехническом смысле и могут быть изготовлены в виде отдельных конструктивов, которые можно использовать для автономной работы за пределами системы. Законченность такой микроЭВМ (в отличие от прототипа) придает наличие индивидуальных синхрогенераторов 151, 152, 153 и блоков 161, 162, 163 сброса, что влечет увеличение входов синхронизации в системе и входов сброса. Для перевода, например, 1-й микроЭВМ в режиме автономной работы достаточно сформировать единичный сигнал на выходе формирователя 121 сигнала АВТ/СИС. Значение этого сигнала может быть считано 1-й микроЭВМ через вход третьего разряда блоков 81 ввода. Кроме этого, сигнал АВТ/СИС= 1 отключает от 1-й микроЭВМ все системные магистрали, что позволяет переходить в автономный режим работы без физического отключения системных магистралей, т. е. не разрушая кабельных соединений системы.

В автономном режиме каждая из 3-х микроЭВМ может использоваться как персональная, поскольку предполагается (как и в прототипе), что все они содержат в своем составе стандартные внешние устройства: клавиатуру, видеотерминал, принтер, дисковводы и т. п. , которые позволяют достаточно просто и полно использовать все ресурсы этих микроЭВМ. Узел 121 (122 или 123) формирования сигнала АВТ/СИС (как и узел 111 (112, 113) формирования сигнала ВДЩ/ВДМ) представляет собой последовательно соединенные резистор и тумблер с фиксацией положения, включенные между шиной питания и общей шиной. Выходной сигнал формируется в точке соединения этих элементов. При включенном тумблере на выходе формируется нулевой сигнал, при выключенном - единичный. Другой особенностью рассматриваемых микроЭВМ является наличие в их составе отключаемых сегментов памяти (ОСП), к которым относятся блоки 51.1. . . 51.4, 52.1. . . 52.4, 53.1. . . 53.4 памяти. Блоки 51.5, 52.5, 53.5 памяти не отключаемы и полностью принадлежат первой, второй и третьей микроЭВМ соответственно. По принципу действия все ОСП являются оперативными запоминающими устройствами (ОЗУ), в то время, как неотключаемые блоки 51.5, 52.5 или 53.5 памяти содержат как ОЗУ, так и постоянное запоминающее устройство (ПЗУ), в котором содержатся части операционной системы (например, программа начальной загрузки, драйверы внешних устройств и т. д. ). Подключение/отключение ОСП к процессорам 21, 22 или 23 через соответствующие магистрали данных, адреса и управления осуществляется с помощью первой матрицы коммутаторов 11.1. . . 11.4, 12.1. . . 12.4, 13.1. . . 13.4, второй матрицы коммутаторов 31.1. . . 31.4, 32.1. . . 32.4, 33.1. . . 33.4 и третьей матрицы коммутаторов 41.1. . . 41.4, 42.1. . . 42.4, 43.1. . . 43.4, которые управляются сигналом, формирующимся на выходе первого разряда соответствующего блока 71, 72 или 73 вывода (на фиг. 1 передается по проводу 41). Этот сигнал может быть условно назван ОБМЕН/РАБОТА (О/Р). Если О/Р = 0, то блоки 51.1. . . 51.4, 52.1. . . 52.4, 53.1. . . 53.4 памяти подключены к внутренним магистралям своих процессоров 21, 22, 23. Так, например, информационные входы блоков 51.1. . . 51.4 памяти через первую матрицу коммутаторов 11.1. . . 11.4 подключаются к магистрали 191 данных, адресные входы блоков 51.1. . . 51.4 памяти через вторую матрицу коммутаторов 31.1. . . 31.4 подключаются к магистрали 201 адреса, входы управления записью/считыванием блоков 51.1. . . 51.4 памяти через третью матрицу коммутаторов 41.1. . . 41.4 подключаются к магистрали 211 управления. При этом блоки 51.1. . . 51.4 памяти (совместно с ОЗУ, входящим в состав блока 51.5) образуют единый модуль оперативной памяти процессора 21, все ячейки которого доступны для адресации их процессором 21. Если сигнал O/P = 1, то блоки 51.1, 51.2, 51.3, 51.4 памяти отключаются от внутренних магистралей процессора 21, при этом возникает возможность обмениваться данными с внешними устройствами одновременно по трем каналам сразу. В рассматриваемой системе такими внешними устройствами являются другие микроЭВМ, для чего они соединяются с помощью кабелей. Других технических средств для комплексирования микроЭВМ в системе не требуется.

В режиме обмена (О/Р = 1), блоки 5i, j памяти матрицы через коммутаторы 1i, j и коммутаторов 3i, j и 4i, j связываются между собой, образуя цепочки блоков 5i, j, где (i = = 1. . . N, j = 1. . . N+1), памяти. Обмен разрешен только внутри определенной цепочки блоков 5i, j памяти и только следующим образом: один блок 5i, j памяти этой цепочки работает на считывание, остальные - на запись. При обмене данными во время параллельного решения задачи системой на считывание работает в первой цепочке блок 51.1 памяти, а остальные блоки 51.2, 52.1, 53.1 памяти - на запись; во второй цепочке - блок 52.2 памяти, а остальные блоки 51.3, 52.3, 53.2 - на запись; в третьей цепочке - блок 53.3, а остальные 51.4, 52.4, 53.4 - на запись, как и в прототипе, такой режим обмена данными в цепочках блоков 5i, j памяти обеспечивается подачей синхроимпульсов, определяющих начало и длительность записи/считывания, которые формируются на выходах 231, 232, 233 управления записью/считыванием соответствующих контроллеров 61, 62, 63 обмена, на вход считывания блоков 51.1, 52.2, 53.3 памяти, из которых производится считывание данных, а на вход записи блоков 51.2, 51.3, 51.4, 52.3, 52.4, 53.1, 53.2, 53.4 памяти, в которые производится запись данных. Передача данных в 1-й, 2-й или 3-й цепочке блоков 51.1, 51.2, 52.1, 53.1; 51.3, 52.2, 52.3, 53.2 или 51.4, 52.4, 53.3, 53.4 находится под управлением устройств управления 61, 62 или 63 обменом, в функции которого входит:

а) формирование адреса перезаписи (формируется на выходе 221, 222 или 223) для всех блоков 5i, j памяти 1-й, 2-й или 3-й цепочки;

б) формирование синхроимпульсов, определяющих начало и длительность записи/считывания (формируются на выходе 231, 232 или 233);

в) осуществление строго определенного числа тактов перезаписи, код числа тактов перезаписи загружается в соответствующий контроллер 61, 62 или 63 обмена перед началом обмена;

г) формирование сигнала "КОНЕЦ ОБМЕНА (КО)", когда реализовано необходимое число тактов перезаписи (такой сигнал с уровнем логической единицы формируется на выходе 241, 242 или 243 признака конца обмена).

На фиг. 4 приведена функциональная схема одного из вариантов устройства управления 61 обменом, отвечающего перечисленным выше требованиям.

Схема содержит блок 33 вывода, схему 34 сравнения, счетчик 35, первый и второй триггеры 36, 37, элемент И-НЕ 38, элемент И-НЕ 39 с открытым коллектором.

Временные диаграммы работы узла приведены на фиг. 14. Перед началом обмена в блок 33 вывода первая микроЭВМ (в общем случае i-я) должна вывести код числа передаваемых байт данных, который устанавливается на первом информационном входе схемы 35 сравнения; сигнал О/Р = 0. Нулевое значение сигнала О/Р обеспечивает нулевое состояние первого триггера 36 (сигнал а = 0), нулевое состояние счетчика 35 (сигнал с = 0) и нулевое состояние второго триггера 37. Сигнал а нулевого значения закрывает элемент И-НЕ 38, что обеспечивает недействующее (единичное) значение сигнала b на выходе 231 управления записью/считыванием. Нулевое состояние счетчика 35 (на выходе 221 адреса перезаписи присутствует код нуля) обеспечивает перезапись с нулевого адреса. Нулевое состояние второго триггера 37 обеспечивает недействующее значение сигнала на выходе 241 признака конца обмена. Запуск контроллера 61 обмена обеспечивается единичным сигналом О/Р (см. момент времени to на фиг. 14).

По срезу первого после перехода сигнала О/Р в единичное состояние тактового импульса (см. момент времени t1) первый триггер 36 переходит в единичное состояние, что открывает элемент И-НЕ 38, на выходе которого при этом формируются импульсы управления записью/считыванием нулевого значения. По фронту этих импульсов инкрементируется содержимое счетчика 35 (см. моменты времени t2. . . t3), что обеспечивает последовательное формирование адресов перезаписи. Когда содержимое счетчика 35 сравнится с кодом числа передаваемых байт данных, сигнал на выходе схемы 34 сравнения перейдет в единицу (см. момент времени t3 на диаграмме d). Это обеспечит переход второго триггера 37 в единичное состояние после формирования последнего необходимого импульса управления записью/считыванием (см. момент времени t4). При этом нулевой сигнал на инвертирующем выходе второго триггера 37 закрывает элемент И-НЕ, что препятствует дальнейшему формированию сигналов управления записью/считыванием, а также закрывает элемент И-НЕ 39 с открытым коллектором, что снимает шунтирование линии признака конца обмена (подразумевается, что к моменту времени t4 устройства управления 62 и 63 обменом установили признаки конца обмена). При переходе сигнала О/Р в нуль (см. момент времени t5) начальный режим устройство 61 восстанавливается.

На фиг. 5 приведена функциональная схема одного из вариантов выполнения узла 1.1 отключаемого сегмента памяти, к которому отнесены коммутатор 11.1 данных; мультиплексор 31.1 адреса; мультиплексор 41.1 управления и блок 51.1 памяти. Мультиплексор 31.1 содержит дешифратор 40, первый и второй мультиплексоры 41, 42. Мультиплексор 41.1 содержит первый и второй мультиплексоры 43, 44. Коммутатор 11.1 данных содержит первый и второй магистральные приемо-передатчики 45, 46 (например, типа 589АП26), элемент НЕ 47 и элемент ИЛИ 48. Дешифратор 40 (селектор адреса) формирует селектирующий сигнал для блока 51.1 памяти и коммутатора 11.1 данных. Этот сигнал подается на первый информационный вход мультиплексора 41, на второй информационный вход которого подается сигнал логического нуля. Выход мультиплексора 41 является выходом селекции мультиплексора 31.1 адреса. При O/P = 0 на выходе мультиплексора 41 присутствует сигнал с выхода дешифратора 40, который может быть нулевым, если произошло совпадение старших шести разрядов кода адреса, формируемого процессом 21, с адресом блока 51.1 памяти (блок 51.1 памяти выбран), или единичным в противном случае (блок 51.1 памяти не выбран). При О/Р = 1 на выходе мультиплексора 41 присутствует нулевой сигнал, что соответствует выбранному состоянию блока 51.1 при обмене данными между микроЭВМ.

Мультиплексор 42 коммутирует десять младших разрядов кода адреса магистрали 201 адреса процессора 21 (МА9. . . МА0) или магистрали 221 адреса контроллера 61 (КМА9. . . КМА0). Выход мультиплексора 42 является выходом адреса мультиплексора 31.1. При О/Р = 0 на выходе мультиплексора 42 присутствует адрес устанавливаемый процессором 21, а при О/Р = 1 - контроллером 61. Мультиплексор 43 коммутирует сигналы записи в блок 51.1 памяти, формируемые процессором 21 (сигнал ЗПЗУ на линии 21) или контроллером 61 обмена (сигнал КЗПЗУ, проходящий через первый узел реверса 131.1). Выход мультиплексора 43 является выходом записи мультиплексора 41.1 управления. При О/Р = 0 на выходе мультиплексора 43 присутствует сигнал ЗПЗУ, а при О/Р = 1 - КЗПЗУ. Мультиплексор 44 коммутирует сигналы чтения из блока 51.1 памяти, формируемые процессором 21 (сигнал ЧТЗУ на линии 21) или контроллером 61 обмена (сигнал КЧТЗУ, проходящий через первый узел реверса 131.1). Выход мультиплексора 44 является выходом чтения мультиплексора 41.1 управления. При О/Р = 0 на выходе мультиплексора 44 присутствует сигнал ЧТЗУ, а при О/Р = 1 - КЧТЗУ. Первым информационным входом/выходом коммутатора 11.1 данных является вход D1, D0 магистральных приемо-передатчиков 45, 46. Вторым информационным входом/выходом коммутатора 11.1 данных является вход/выход DB магистрального приемо-передатчика 45, подключенного к магистрали 191 данных процессора 21 (МД7. . . МД0). Третим информационным входом/выходом коммутатора 11.1 данных является вход/выход DB магистрального приемо-передатчика 46, принадлежащей первой цепочки обмена (КМД7. . . КМДО, жгут 26 на фиг. 1). При О/Р = = 0 информационный вход/выход блока 51.1 памяти может быть подключен к магистрали 191 данных процессора 21, если блок 51.1 памяти выбран. При этом на выходе элемента ИЛИ 48 формируется нулевой сигнал, который открывает приемо-передатчик 45. Если блок 51.1 памяти не выбран, т. е. на выходе селекции мультиплексора 31.1 адреса действует единичный сигнал, то приемо-передатчик 45 не может быть открыт, что исключает конфликт на магистрали 191 данных. При О/Р = 0 приемо-передатчик 46 закрыт единичным выходным сигналом элемента НЕ 47. При О/Р = 1 закрыт приемо-передатчик 45 и открыт приемо-передатчик 46, что обеспечивает подключение информационного входа/выхода блока 51.1 памяти к магистрали данных первой цепочки обмена (КМД7. . . КМД0, жгут 26 на фиг. 1). Направление передачи данных через открытый приемо-передатчик 45, 46 определяется значением сигнала на выходе чтения мультиплексора 41.1 управления.

Таким образом, видно, что при обмене данными при параллельной работе всех микроЭВМ системы источником информации в i-й цепочке является блок 5i, i памяти, в конкретном примере это блоки 51.1, 51.2, 51.3. Остальные блоки 5i, j памяти являются приемниками информации. В предложенном устройстве такой порядок обмена может быть изменен (реверсирован), тогда источниками информации становятся все отключаемые блоки 5i, j памяти одной микроЭВМ (назовем такую микроЭВМ ведущей), а приемниками информации - отключаемые блоки 5i, j памяти остальных микроЭВМ системы (ведомые), принадлежащие соответствующей цепочке. Необходимость в реверсе возникает при передаче программ из ведущей микроЭВМ в ведомые, а также - при передаче данных, когда система переходит из неразветвленного режима работы (задачу решает ведущая микроЭВМ) в параллельный режим работы (задача решается всеми микроЭВМ системы или в общем случае более чем одной микроЭВМ). Реверс осуществляется с помощью матрицы демультиплексоров 13ii (131.1, 132.2, 133.3) реверса и узлов 14ij (141.3, 141.4, 142.1, 142.4, 143.1, 143.2). В процессе работы все микроЭВМ формируют служебные сигналы (большая часть которых является для i-ых процессоров: 21, 22 или 23 запросами на прерывание):

а) О/Р (формируется на выходе первого разряда блока 7i вывода i-той микроЭВМ) - определяет режим работы отдельных микроЭВМ системы. При О/Р = 0 происходит автономное (независимое от других микроЭВМ) решение основной или фоновой задачи, при O/P = 1 - обмен данными между всеми микро-ЭВМ сразу по N каналам (цепочкам блоков 5i, j памяти). Обменом управляют устройства управления 6i обменом, а микроЭВМ без ОСП продолжают решать фоновую задачу, поскольку в их составе остаются, как ОЗУ, так и ПЗУ (блоки памяти 5i, 5; 51.5, 52.5, 53.5). При О/Р = 1 не только отключаются ОСП от своих внутренних магистралей, но и запускаются устройства управления 6i обменом, поскольку этот сигнал подается на их входы запуска;

б ) РЕШЕНИЕ ЗАКОНЧЕНО (РЗ, формируется на выходе второго разряда порта 7i вывода i-й микроЭВМ) - определяет степень завершенности процесса решения задачи при исполнении очередного фрагмента программы при параллельной работе микроЭВМ системы. При РЗ = 0 условия выхода из процесса итерационных вычислений не выполнены хотя бы в одной микроЭВМ, при РЗ = 1 условия выхода из процесса итерационных вычислений выполнены во всех микроЭВМ системы. Сигнал РЗ воздействует на вход управления демультиплексоров 9i, что позволяет в зависимости от значения сигнала РЗ формировать два запроса на прерывание НИ или ВИ. При РЗ = 0 формируется запрос на прерывание НИ, который физически создается сигналом КО, подаваемым на информационные входы демультиплексоров 9i. Сигнал КО инициируется сигналом О/Р = 1, который всегда формируется совместно с сигналом РЗ (см. фиг. 6. . . 13). Такое использование сигналов О/Р и РЗ позволяет переходить на следующий фрагмент программы только после обмена результатами решения предыдущим фрагментом программы. При РЗ = 1 формируется запрос на прерывание ВИ;

в) ПП (формируется на выходе третьего разряда порта 7i вывода i-й микроЭВМ) - инициализирует процесс передачи программ из ведущей микроЭВМ в ведомые. При ПП = 1 формируется запрос на прерывание ПП, в ходе обслуживания которого происходит запись в ведомые микроЭВМ программ решения задачи, которые компилируются в ведущей микроЭВМ. Значение ПП = 0 является пассивным;

г) ПР (формируется на выходе четвертого разряда порта 7i вывода i-й микроЭВМ) - инициализирует процесс перехода ведомых микроЭВМ в начало нового фрагмента программы при переходе системы от неразветвленного режима работы к параллельному. При ПР = 1 формируется запрос на прерывание ПР, в ходе обслуживания которого ведомые микроЭВМ переходят в начало нового фрагмента программы решения задачи. Значение ПР = 0 является пассивным;

д) ОШ (формируется на выходе пятого разряда порта 7i вывода i-й микроЭВМ) - инициализирует останов решения задачи при возникновении ошибки в ходе работы ведомых микроЭВМ. При ОШ = 0 формируется запрос на прерывание ОШ, поскольку подается на входы инверторов 10i (при ОШ = 0 на выходе инверторов 10i формируется единичный сигнал, который для входа прерывания процессора 2i считается действующим). В ходе обслуживания прерывания ОШ ведущая микроЭВМ получает диагностическую информацию от ведомых микроЭВМ, анализирует ее и сообщает оператору об источнике и виде возникшей ошибке;

е) РЕВЕРС (формируется на выходе шестого разряда блока 7i вывода i-й микроЭВМ) - устанавливает реверсивный режим работы i-й цепочки блоков 5i, j памяти. При РЕВЕРС = 1 - в i-й цепочке устанавливается реверсивный режим работы, при РЕВЕРС = = 0 - обычный режим работы.

Необходимо помнить, что первые пять выходов блоков 7i вывода (также как и выходы признаков конца обмена устройств управления 6i обменом) имеют открытый коллектор, что позволяет достаточно просто комплексировать отдельные микроЭВМ в систему, а также унифицировать состав отдельных микроЭВМ (устранить элементы, которые в прототипе принадлежат системе в целом, а не микроЭВМ в отдельности).

Упрощенный алгоритм функционирования каждой отдельной микроЭВМ системы представлен на фиг. 6. При подаче питания (или после нажатия "СБРОС", которая входит в состав блока 16i сброса) i-я микроЭВМ запрещает прерывания для того, чтобы провести инициализацию, далее устанавливается (блок 50) пассивное состояние сигналов: ПП = ПР = О/Р = РЗ = 0, ОШ = 1, что является исходным режимом для системы. Блоком 51 производится проверка значение сигнала АВТ/СИС, для чего производится чтение порта 8i ввода и проверка третьего разряда введенного кода. Если значение этого разряда равно 1, то это означает, что рассматриваемая микроЭВМ должна работать автономно и происходит передача управления на блок 57, который разрешает все прерывания. МикроЭВМ при этом работает (блок 58) аналогично персональным ЭВМ (ПЭВМ). При решении задач в этом режиме ОСП подключены к внутренним шинам и используются, как обычные ОЗУ. Программы решаемых задач могут располагаться в любом месте адресного пространства i-го процессора 21, с учетом особенностей операционной системы. Если сигнал АВТ/СИС = 0, то это означает, что рассматриваемая микроЭВМ подключена к системе и происходит передача управления на блок 52, в котором проверяется сигнал ВДЩ/ВДМ (при этом также производится чтение блока 8i ввода, но проверяется второй разряд введенного кода). Если сигнал ВДЩ/ВДМ = 0 (этот сигнал формируется блоком 11i формирования сигнала ВДЩ/ВДМ), то рассматриваемая микроЭВМ в системе будет ведомой и произойдет передача управления на блок 60, в котором устанавливается активное состояние сигналов ПП = ПР = 1. Это деблокирует линии ПП и ПР и позволяет ведущей микроЭВМ быть единственным в системе источником этих сигналов. Блок 61, разрешая прерывания, позволяет перейти к решению фоновой задачи (блок 62), которой может являться пользовательская задача пользователя i-й микроЭВМ. Решение основной для системы задачи в ведомых микроЭВМ происходит в ходе обработки соответствующих прерываний (см. фигуры 7. . . 11).

Для пользователя i-й микроЭВМ, которая является ведомой, работа в системе будет проявляться в несколько меньшей скорости решения его задачи, посколько ресурсы этой микроЭВМ будут иногда (при параллельной работе системы) использоваться для решения основной задачи. Для совместного решения основной и фоновой задач их программы и рабочие ячейки не должны пересекаться в адресном пространстве ОЗУ, прерывания системы должны иметь больший приоритет, чем прерывания необходимые для решения фоновой задачи, а обслуживание системных прерываний должно начинаться сохранением в стеке содержимых регистров общего назначения процессора 2i, его счетчика команд и заканчивается возвратом этих значений (на фиг. 7. . . 11 эти блоки условно не показаны). Если сигнал ВДЩ/ВДМ = 1, то это означает, что рассматриваемая микроЭВМ ведущая и происходит передача управления на блок 53, в котором маскируется прерывания ПП и ПР для того, чтобы исключить реакцию на запросы, которые ведущая микроЭВМ формирует только для ведомых. После разрешения (блок 54) оставшихся прерываний (НИ, ВИ, ОШ) ведущая микроЭВМ начинает принимать задачу (блок 55) от пользователя всей системы в целом. При этом предполагается, что в состав операционной системы ведущей микроЭВМ входит компилятор с алгоритмического языка высокого уровня, позволяющего производить вычисления параллельно (компиляция программы является частью функций блока 56). После компиляции программы (создания законченных программ в машинных кодах для всех N микроЭВМ системы) ведущая микроЭВМ передает программы работы в ведомые микроЭВМ, используя сигнал запроса на прерывание ПП. Для передачи программ используются цепочки блоков 5i памяти, которые в этом случае находятся в реверсивном режиме. Так, если ведущей является микроЭВМ с номером 1, то по i-й цепочке (i = 2. . . N) передается программа для i-й микроЭВМ соответственно.

Объем передаваемой программы за один сеанс передачи не может превосходить объем ОСП-М. Если необходимо передавать достаточно большую программу, то сигнал ПП передается несколько раз, что соответствует нескольким сеансам передачи. Переход на параллельный режим работы происходит после формирования ведущей микроЭВМ сигнала ПР, выход из параллельной работы (переход на неразветвленный режим) происходит, когда все микроЭВМ сформируют сигналы О/Р = 1 и РЗ = 1. Если в F-ом фрагменте при параллельной работе системы решается итерационная задача и очередная итерация закончена, но условие выхода из процесса итерационных вычислений не выполнено хотя бы в одной микроЭВМ, то эта микроЭВМ формирует сигналы O/P = 1, РЗ = 0 и система после обмена данными продолжает процесс итерационных вычислений.

Если задача системой решена, то при отсутствии признака конца работы, т. е. при сигнале ПРК = 0, происходит прием новой задачи для системы и ее решение по описанному выше алгоритму. На фиг. 7 представлен более подробный алгоритм обслуживания прерывания ПП. В блоке 66 происходит максирование прерывания НИ, которое формируется всегда после окончания обмена в системе, т. е. тогда когда сигнал КО = 1. Это прерывание обычно вызывает переход на начало текущего фрагмента программы. В рассматриваемом случае, когда происходит передача программ из ведущей микроЭВМ в ведомые такой переход нежелателен хотя бы потому, что для передачи программ в разные микроЭВМ может потребоваться разное число сеансов передачи. В этом случае переход на начало работы должен происходить после формирования ведущей микроЭВМ сигнала ПР = 1, когда все сеансы передачи программ закончены.

В блоке 67 происходит выдача сигнала РЕВЕРС = 1 всеми ведомыми микроЭВМ на выходе шестого разряда порта 7i вывода. Эти сигналы поступают по i-ым цепочкам блоков 5i, j памяти на соответствующие входы узлов 13i, j и узлов 14i, j реверса, принадлежащих этим цепочкам, подготавливая их к реверсивной передаче информации, т. е. от ведущей микроЭВМ к ведомым. Достигается это тем, что в узлах 13i, j сигнал реверса поступает на управляющий вход мультиплексора 30. При РЕВЕРС = 0 импульсы управления записью/считыванием i-го котроллера 6i обмена проходят через вывод мультиплексора 30, который связан с входом чтения блока 5i, j памяти (через входы КЧТЗУ мультиплексора 44, входящего в состав мультиплексора 4i, j управления). Это соответствует нормальной работе i-й ячейки, когда блок 5i, j памяти является источником информации для остальных ОСП i-й цепочки. При РЕВЕРС = 1 импульсы управления записью/считыванием i-го контроллера 6i обмена проходят через вывод демультиплексора 30, который связан с входом записи блока 5i, j памяти (через вход КЗПЗУ мультиплексора 43, входящего в состав мультиплексора 4i, j управления). Это соответствует реверсивному режиму работы, когда источником информации в цепочке является ОСП, принадлежащий ведущей микроЭВМ и в блоке 5i, i памяти ведомых микроЭВМ происходит запись программы. В узлах 14i, j реверса сигнал РЕВЕРС поступает на один из входов элемента И 32, на второй вход которого поступает сигнал ВДЩ/ВДМ. Если РЕВЕРС = 1 и ВДЩ/ВДМ = 1, то на выходе элемента И 32 появляется единичный уровень, который программирует демультиплексор 31 на передачу импульсов управления записью/считывания i-го контроллера 6i обмена через вывод, который соединен с входом чтения (через вход КЧТЗУ мультиплексора 44, который входит в состав мультиплексора 4i, j управления).

Т. е. ОСП, принадлежащий ведущей микроЭВМ (ВДШ/ВДМ = 1) в реверсивном режиме (РЕВЕРС = 1) является источником информации программы для всех других ОСП i-й цепочки. В других случаях (т. е. при ВДЩ/ВДМ = 0) или РЕВЕРС = 0) ОСП является приемником информации. В блоке 68 происходит выдача сигнала О/Р = 1 на своем выходе, т. е. на выходе первого разряда порта 7i вывода i-й микроЭВМ. Когда все микроЭВМ системы выставят этот сигнал, то он появится на всей линии (выполнится операция "монтажное И") и все ОСП отключатся от внутренних магистралей и соединятся в цепочки, а контроллеры 6i обмена начнут управление процессом обмена. Все микроЭВМ системы программно следят за окончанием этого процесса (блоки 69, 70 на фиг. 7). Если процесс обмена закончен, то происходит переход на блок 71, в котором выдается сигнал О/Р = 0, что подключает все ОСП к своим внутренним магистралям. В блоке 72 происходит перезапись программы из ОСП в ОЗУ, при этом формат передаваемого сообщения строго определен, например, в самой первой ячейке ОСП помещается длина программы -m, во второй - начальный адрес, в последующих (m-2) ячейках - пакет программы. Если m = M, то программа может иметь продолжение, т. е. введена не полностью, если m < М, то необходимо проанализировать содержимое (m+1) ячейки. Если содержимое (m+1) ячейки не равно нулю, то это код длины следующего фрагмента программы, за которым следует начальный адрес и пакет программы этого фрагмента. Если сумма m всех фрагментов программы, записанной в ОСП равна М, то программа введена не полностью. В противном случае программа введена полностью. Все это проверяется в блоке 73. Если программа введена не полностью, то ведомая микроЭВМ выходит из прерывания и продолжает решение фоновой задачи, ожидая следующего сеанса передачи программы.

Если программа передана полностью, то максируется (блок 74) прерывание ПП, поскольку в оставшиеся микроЭВМ могут еще вводиться программы и сигналы ПП = 1 повторяться (реакция микроЭВМ, закончивших уже прием программ на этот сигнал прерывания нежелательна). В блоке 75 снимается сигнал реверса (т. е. РЕВЕРС = 0), поскольку в цепочке с законченным процессом передачи программ такой сигнал уже не нужен. В блоке 76 устанавливается начальное значение счетчику фрагментов программ F = 0.

По значению счетчика выбирается начальный адрес F-го фрагмента из таблице, которая передается в ведомую микроЭВМ при передаче программы. После передачи программ во все ведомые микроЭВМ ведущая микроЭВМ выполняет программу, относящуюся к неразветвленной части процесса решения (если она имеется перед параллельными вычислениями), выдает сигнал ПР и переходит на решение фоновой задачи. Такой задачей для ведущей микроЭВМ может являться опрос клавиатуры. Сигнал ПР для ведомых микроЭВМ является запросом на прерывание, алгоритм обслуживания которого приведен на фиг. 8.

В блоке 77 этого алгоритма производится сброс сигналов О/Р и РЗ для установки начального состояния сигналов на этих линиях. В блоке 78 выдается сигнал реверса, поскольку предполагается, что перед началом параллельных вычислений начальные данные для F-го фрагмента подготовлены в ведущей микроЭВМ и должны быть оттуда переданы в ведомые микроЭВМ. В блоке 79 разрешаются прерывания ПП и НИ, запрещенные в подпрограмме обслуживания прерывания ПП, после чего все микроЭВМ снова становятся восприимчивыми к этим запросам на прерывание. В блоке 80 i-я ведомая микроЭВМ производит передачу в i-е устройство управления 6i обменом код числа передаваемых данных (максимальное значение этого кода - М). В блоке 81 происходит выдача сигнала О/Р = 1 и выход из подпрограммы. Когда такой сигнал выдадут все микроЭВМ системы, то системный сигнал О/Р = 1 (выполнится операция "монтажное И") и в системе возникает режим обмена, который закончится выдачей сигнала КО = 1 всеми контроллерами 6i обмена. Этот сигнал вызывает запрос на прерывание НИ (поскольку сигнал РЗ = 0) во всех микроЭВМ системы, обслуживание которого (см. фиг. 9) заключается в передаче управления на начало F-го фрагмента программы, структура которого приведена на фиг. 10. В блоке 82 снимается сигнал реверса (т. е. РЕВЕРС = 0) поскольку после решения F-го фрагмента обмен производится обычным порядком. В блоке 83 снимаются сигналы О/Р и РЗ - первый для подключения ОСП к внутренним магистралям, а второй - поскольку решение фрагмента еще не закончено. Собственно решение производится в блоке 84 и, если ошибок нет, то происходит передача управления на блок 86, в котором производится проверка конца итерации.

Если итерация не закончена, то решение продолжается; в противном случае проверяется (в блоке 87) выполнение условия выхода из процесса итерационных вычислений. Если условия выхода из процесса итерационных вычислений не выполнено (необходимая точность вычисления не достигнуты), то происходит переход на блок 89, в котором формируется сигнал О/Р = 1. Когда такой сигнал установят все микроЭВМ системы, то произойдет обмен данными и после обмена переход на начало F-го (текущего) фрагмента программы всех микроЭВМ, т. е. система начинает новую итерацию. Описанный выше процесс проходит по следующей цепочке событий: О/Р = 1 -> обмен ->КО = 1-> запрос на прерывание НИ, поскольку РЗ = 0. Если условия выхода из процесса итерационных вычислений выполнены, то происходит выдача РЗ = 1 (блок 88) и О/Р = 1 (блок 89), что вызывает выход из текущего фрагмента программы по следующей цепочке событий: О/Р = 1 -> обмен -> КО = - ВИ, поскольку РЗ = 1. Необходимо отметить, что после выполнения блока 89 происходит выход из подпрограммы, т. е. возврат к решению фоновой (пользовательской) задачи, которая решается, по крайней мере, в течение всего времени обмена.

Описанный выше процесс итерационных вычислений полностью идентичен аналогичному процессу в прототипе за исключением обработки ошибок вычислений (деление на нуль и т. п. ). В прототипе отсутствуют аппаратные средства для останова вычислений при возникновении ошибок. В заявляемом устройстве при наличии ошибок вычислений происходит передача управления на блок 90, в котором определяется в ведущей или в ведомой микроЭВМ обнаружена ошибка. Если ошибка обнаружена в ведомой микроЭВМ, то происходит передача управления на блок 91, в котором код ошибки засылается в блок 5i, i памяти (i-й номер отказавшей микроЭВМ) для его передачи в ведомую микроЭВМ. После этого (блок 92) маскируются запросы на прерывание ОШ и НИ, первое - поскольку самопрерывание нежелательно, т. е. код ошибки уже заслан в ОСПi, i, а это является содержанием подпрограммы обработки запроса на прерывание ОШ, а второе - для того, чтобы после обмена кодами состояния микроЭВМ (производится в ходе облуживания прерывания ОШ) не переходить на новую итерацию, т. к. в решении уже есть ошибки. В блоке 93 выдается сигнал О/Р = 1, чтобы инициировать обмен кодами состояния микроЭВМ. В блоке 94 выдается сигнал ОШ = 0 (на выходе пятого разряда порта 7i вывода). Этот сигнал сразу вызывает сигнал запроса на прерывание ОШ (реализуется операция "монтажное ИЛИ" на выходах пятого разряда портов 7i вывода). Если ошибка обнаружена в ведущей микроЭВМ, то сообщение об этом выдается оператору сразу после ее возникновения (блок 95). Ведомые микроЭВМ при этом выполняют итерацию, а после ее выполнения, установив соответствующие значения сигналов О/Р и РЗ, переходят на решение пользовательской задачи.

Из сказанного выше видно, что параллельные вычисления заканчиваются практически одновременной установкой сигналов O/P = 1 РЗ = 1. Когда эти сигналы установят все микроЭВМ системы, то формируется запрос на прерывание ВИ, алгоритм обслуживания которого приведен на фиг. 11. В блоке 96 инкреминтируется счетчик фрагментов F. В блоке 97 проверяется статус микроЭВМ. Если микроЭВМ ведомая, то происходит выход из подпрограммы; если ведущая, то переход в начало следующего фрагмента, структура которого приведена на фиг. 12. Такое различие в реакции на запрос прерывания ВИ связано с тем, что ведомые микроЭВМ участвуют только в параллельных вычислениях, а ведущая микроЭВМ выполняет также и неразветвленные части программы решения системной задачи. Структура фрагментов при параллельной работе системы в основном совпадает со структурой фрагментов, решающих неразветвленные части задачи, так блоки 99. . . 101 фиг. 12 полностью идентичны блокам 84. . . 86 фиг. 10.

Отличие заключается в том, что после решения фрагмента в программе фиг. 12 (блок 102) осуществляется проверка окончания решения всей системной программы в целом, а не окончания итерационного процесса (блок 87 фиг. 10). Если системная задача не решена, то происходит переход на блок 104, в котором инкрементируется счетчик фрагментов программы F; выдается (блок 105) сигнал О/Р = 1, поскольку предполагается переход на параллельную работу системы, и связанный с ней обмен. В блоке 106 производится выдача сигнала ПР = 1, который инициирует переход на параллельную работу системы с новыми фрагментами программы. Если решение системной задачи закончено, то в блоке 103 происходит выдача результатов решения. Если в процессе решения возникают ошибки, то происходит передача управления на блок 107, в котором выдается сообщение оператору об ошибке.

На фиг. 13 приведен алгоритм обработки запроса на прерывание ОШ. В блоке 108 маскируется запрос на прерывание НИ, поскольку при обнаружении ошибки при решении системной задачи нет смысла продолжать вычисления. Ведомые микроЭВМ далее реагируют (блок 114) пересылкой кода отсутствия ошибки в блок 5i, i памяти, где i-номер ведомой микроЭВМ и выдачей сигнала О/Р = 1, чтобы создать в системе условия для обмена. Ведущая микроЭВМ выдает сигнал О/Р = 1 (блок 110), а затем программным путем (блоки 111, 112) проверяет окончание обмена. Далее, в блоке 113, выдается сигнал О/Р = 0, что подключает ОСПi, j к внутренним магистралям и анализируется источник и код ошибки о чем выдется сообщение оператору. (56) 1. Авторское свидетельство СССР N 1012232, кл. G 06 F 15/16, 1979.

2. Авторское свидетельство СССР N 1242977, кл. G 06 F 15/16, 1984.

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| ОТКАЗОУСТОЙЧИВЫЙ МУЛЬТИМИКРОКОНТРОЛЛЕР | 1999 |

|

RU2156492C1 |

| Модуль матричного коммутатора | 1990 |

|

SU1793436A2 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2198417C2 |

| Устройство обмена данными распределенной управляющей системы | 1990 |

|

SU1718226A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке многопроцессорных систем. Целью изобретения является повышение быстродействия за счет решения не полностью распараллеливаемых задач. Поставленная цель достигается тем, что система содержит три матрицы коммутаторов HX(H + 1), матрицу HX(H + 2) блоков памяти H устройств управления обменом, H демультиплексоров, H блоков ввода, H блоков вывода, матрицу HX(H + 1) демультиплексоров второй группы и H элементов НЕ. 14 ил.

СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРОВ, содержащая с первой по третью матрицы коммутаторов размером H · (H+1) каждая, где H - число коммутируемых процессоров, матрицу размером H · (H+2) блоков памяти, H устройств управления обменом и первый демультиплексор группы, первые блок ввода и блок вывода, причем первый вход синхронизации системы подключен к входу синхронизации первого устройства управления обменом, информационный вход-выход, адресный вход и вход записи считывания блока памяти а-й строки б-го столбца матрицы блоков памяти (где а= 1, . . . H, б= 1, . . . , H+1) подключены соответственно к первому информационному входу-выходу коммутатора а-й строки б-го столбца первой матрицы коммутаторов, к первому выходу коммутатора а-й строки б-го столбца второй матрицы коммутаторов и к первому выходу коммутатора а-й строки б-го столбца третьей матрицы коммутаторов, а-й информационный вход-выход системы подключен через а-ю магистраль данных к первому информационному входу а-го устройства управления обменом, к вторым информационным входам-выходам коммутаторов а-й строки первой матрицы коммутаторов и к информационному входу-выходу блока памяти а-й строки (H+2)-го столбца матрицы блоков памяти, а-й адресный вход системы подключен через а-ю магистраль адреса к второму информационному входу а-го устройства управления обменом, к первым информационным входам коммутаторов а-й строки второй матрицы коммутаторов и к адресному входу блока памяти (H+2)-го столбца а-й строки матрицы блоков памяти, а-й вход режима системы подключен через а-ю магистраль управления к первому управляющему входу а-го устройства управления обменом, к первым информационным входам коммутаторов а-й строки третьей матрицы коммутаторов и к входу записи/считывания блоков памяти (H+2)-го столбца а-й строки матрицы блоков памяти, третий информационный вход-выход коммутатора а-й строки а-го столбца первой матрицы коммутаторов подключен к третьим информационным входам-выходам коммутаторов к-й строки а-го столбца и коммутаторов в-й строки (а+1)-го столбца первой матрицы коммутаторов (где к= а, . . . , H, б= 1, . . . , a), вторые выходы коммутаторов а-й строки б-го столбца третьей матрицы коммутаторов подключены соответственно к входам режима коммутаторов а-й строки б-го столбца первой матрицы коммутаторов, вторые выходы коммутатора а-й строки б-го столбца второй матрицы коммутаторов подключены соответственно к входам синхронизации блоков памяти а-й строки б-го столбца первой матрицы коммутаторов, первый выход а-го устройства управления обменом подключен к вторым информационным входам коммутаторов к-й строки а-го столбца и коммутаторов в-й строки (а+1)-го столбца второй матрицы коммутаторов, второй выход а-го устройства управления обменом подключен к второму информационному входу коммутатора а-й строки (а+1)-го столбца третьей матрицы коммутаторов, отличающаяся тем, что, с целью повышения быстродействия за счет решения не полностью распараллеливаемых задач, она содержит с второго по H-й блоки ввода, с второго по H-й блоки вывода, с второго по H-й демультиплексоры группы, матрицу размером H · (H+1) демультиплексоров 2-й группы и H элементов НЕ, причем входы синхронизации системы с второго по H-й подключены соответственно к входам синхронизации устройств управления обменом с второго по H-й, первые информационные входы а-го блока ввода и а-го блока вывода через а-ю магистраль данных подключены к а-му информационному входу-выходу системы, вторые информационные входы а-го блока ввода и а-го блока вывода через а-ю магистраль адреса подключены к а-му информационному входу системы, первый управляющий вход а-го блока ввода и управляющий вход а-го блока вывода через а-ю магистраль управления подключены к а-му входу режима системы, первые выходы блоков вывода объединены по схеме "монтажное ИЛИ" и подключены к управляющим входам коммутаторов первой, второй и третий матриц коммутаторов и к вторым управляющим входам всех устройств управления обменом, третьи выходы которых через схему МОНТАЖНОЕ ИЛИ подключены к вторым управляющим входам всех блоков ввода и к информационным входам всех демультиплексоров группы, вторые выходы всех блоков вывода через схему МОНТАЖНОЕ ИЛИ подключены к управляющим входам всех демультиплексоров группы, первый и второй выходы а-го демультиплексора группы подключены соответственно к а-м входам первой и второй групп прерывания системы, третьи выходы всех блоков вывода через МОНТАЖНОЕ ИЛИ подключены к выходам с первого по H-й третьей группы прерывания системы, четвертые выходы всех блоков вывода через схему МОНТАЖНОЕ ИЛИ подключены к выходам с первого по H-й четвертой группы прерывания системы, пятые выходы блоков вывода с первого по H-й через схему МОНТАЖНОЕ ИЛИ подключены к входам элементов НЕ с первого по H-й, выходы которых подключены соответственно к выходам с первого по H-й пятой группы прерывания системы, второй выход а-го устройства управления обменом подключен к информационному входу демультиплексора а-го столбца а-й строки матрицы демультиплексоров и к информационным входам демультиплексоров к-й строки с-го столбца и р-й строки (с+1)-го столбца матрицы демультиплексоров (где с= 1, . . . , H; . . . К= а, . . . H, р= 1, . . . , а), шестой выход а-го блока вывода подключен к управляющему входу демультиплексора а-й строки а-го столбца матрицы демультиплексоров и к первым управляющим входам демультиплексоров к-й строки с-го столбца матрицы демультиплексоров и к первым управляющим входам демультиплексоров к-й строки с-го столбца и р-й строки (с+1)-го столбца матрицы демультиплексоров, а-й вход признака "Ведущий/ведомый" системы подключен к третьему управляющему входу а-го блока ввода и к вторым управляющим входам демультиплексоров а-й строки Т-го столбца матрицы демультиплексоров (где Т-1, . . . , H+1; T ≠ a, T ≠ a+1), а-й вход признака "Автономно/система" системы подключен к четвертому управляющему входу а-го блока ввода, первый и второй выходы демультиплексора а-й строки а-го столбца матрицы демультиплексоров подключены соответственно к второму и к третьему информационным входам коммутатора а-й строки а-го столбца третьей матрицы коммутаторов, первый и второй выходы демультиплексора а-й строки Т-го столбца матрицы демультиплексоров подключены соответственно к второму и к третьему информационным входам коммутатора а-й строки Т-го столбца третьей матрицы коммутаторов.

Авторы

Даты

1994-01-30—Публикация

1991-06-24—Подача