(54) ИНТЕГРИР1ТОЩЕЕ УСТРОЙСТВО

ой масштабный реэио-тор к замлкаюему контакту третьего переключаеля, разкыкающий контакт которого одключен через второй запоминающий лемент к инвертирующему входу втоого операционного усилителя, выход оторого соединен с переключающим онтактом третьего переключателя, переключающий контакт первого пееключателя через первый переменный масштабный резистор под;1ключен ко входу устройства, и датчик временных интервалов, подключенный к уп-. равляющим входам переключателей, дополнительно введены два переменных масштабных резистора, Операционные усилители выполнены дифференциальными, причем их неинвертирующие входы через соответственно второй и третий переменные масштабные резисторы соединены со входом устройства, а раз ыкающий контакт второго переключателя и замыкающий контакт третьего переключателя подключены к выходу устройства.

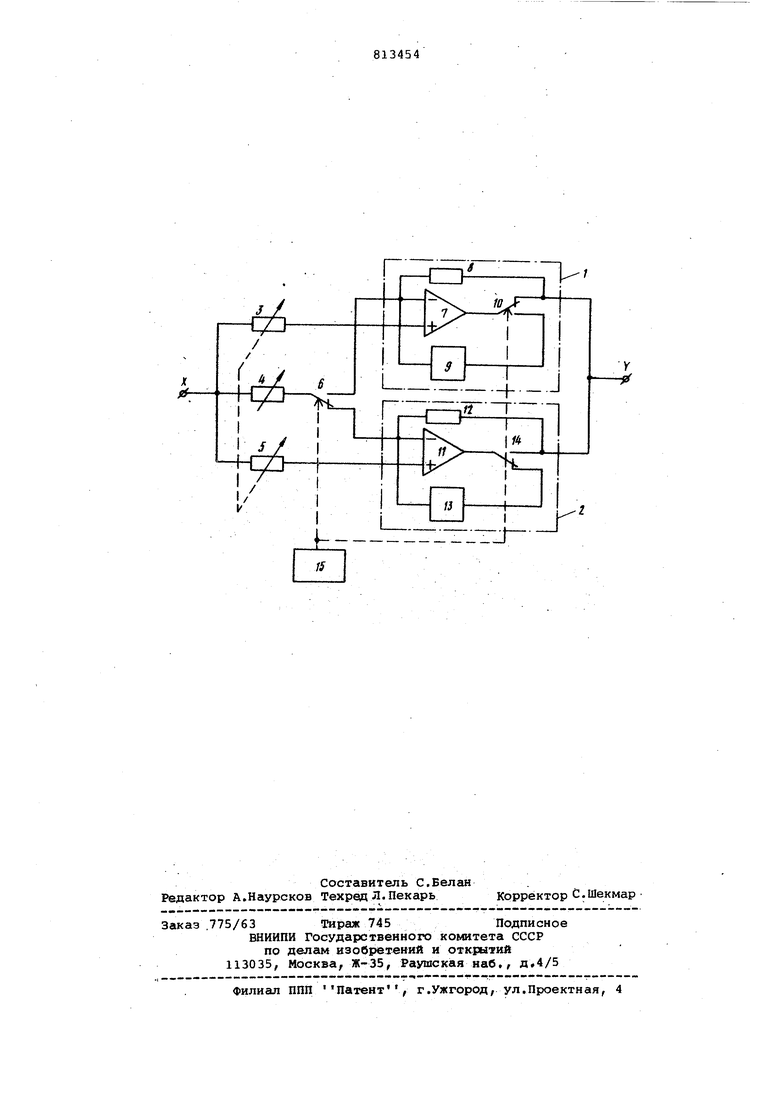

На чертеже представлена схема предлагаемого интегрирующего устройства.

Устройство содержит запоминающие блоки 1 и 2, переменные масштабные резисторы 3,4 и 5 и переключатель б. Запоминающий блок 1 состоит из дифференциального операционного усилителя 7 с масштабным резистором 8 в цепи обратной связи, запоминающего элемента 9 и переключателя 10.Запоминающий блок 2 состоит из дифференциального операционного усилителя 11 с масштабным резистором 12 в цепи обратной связи, запоминающего элемента 13 и переключателя 14. Все переключатели управляются- от датчика 15 временных интервалов.

Входом устройства является точка соединения всех переменных резисторов, а выходом - точка соединения выходов запоминающих блоков 1 и 2.

Интегрирующее устройство работает следующим образом.

Переключающий контакт переключателя 10 находится в верхнем положении, а переключателей 6 и 14 - в нижнем. При этом запоминающий блок

1находится в режиме считывания выходного сигнала, а запоминающий блок

2- -в р ежиме записи поступгиощих сигналов. Шлходной сигнал Y(t)-Ha выходе усилителя 7 представляет собой алгебраическую- сумму текуъа/его входного сигнгша x(t), подаваемого через переменный резистор 3, и сигнала, здписанного в запоминающий элемент

9 на предыдущем такте.

В это же время на инвертируюищй вход усилителя 11 подается входной сигнал x(t), поступающий через переменный резистор 4 и переключатель €, и выходной сигнал Y(t) - через резистор 12. На неинвертирующий вход этого же усилителя подается

через переменный резистор 5 входной сигнал x(t).

Предположим, в исходном состоянии в оба элемента памяти 9 и 13 записаны нули (). На первом шаге с появлением входного сигнала ,Хц(Ъ) получим на выходе запоминающего блока 1

У (t)KHX(t) , где К, | |.

Q В запоминающий блок 2 в это время записывается токовый сигнал

Bl.

ill (t)i-: - x-,(t).i- - x(t)

Rf

R4

15 «

По команде датчика 15 временных интервалов в режим записи, переводится блок 1, а считывания блок 2. Тогда на втором шаге на выходе запоминающего блока 2 получим

ft) ir- x.(t)-Ra (i i 1л R, -Rj RA RS

)x (t)+KiXi, где

R g R

X - значение входного сигнала в конце первого шага. Знак минус перед вторым слагаемым взят ввиду того, что записанный в запоминающий элемент сигнал в режиме считывания инвертируется.

В это же время идет запись сигналов в запоминающий блок 1

Ri7

i,(t)-, c,(t).-x.

(t)

Rj

Rjf

1

- X4-K,

R8

Q После команды датчика 15 снова запоминающий блок 2 переводится в режим записи, а запоминающий блок 1 - в режим считывания.

Вь)ходной сигнал на третьем шаге

Y3(t) K,X3(t)-R5(|- -|;-K,.)Xif

+ ,- , ft)(Xi+Xi)

и т.д.

Предлагаемое устройство реализует алгоритм

yrt(t)Kj,X,(t)+Kt 5 Х4 , при 0.

Как видно из формулы, первое слагаемое представляет собой пропорционсшьную составляющую текущего значения входного сигнала. Второе слагаемое есть сумма значений входных сигнёшов HSL предыдущих п-1 шагах, т.е. дискретный интеграл от входного сигнала на этих шагах. Следовательно, устройство формирует сигнал по пропорционально-интегральному saxoHj.

Настройка коэффициентов К осуществляется резисторгики 3 и 5, К резистором 4. При (сопротивле-

ние резисторов 3 и ) устройство работает в режиме дискретного интегратора. При (сопротивление ) устройство вырождается в линейное звено.

Постоянная времени интегрировани определяется величиной коэффициента KI и длительностью интервала квантования. Она равна 4 T/Kf .

Таким образом, наличие дополнительных переменных резисторов, выполнение операционных усилителей дифференциальными и связь их неинвертирующих входов через переменные резисторы со входом устройства, а также соединение выходов запомингиощих блоков с выходом устройства расширило его функциональные возможности. Данное интегрирующее устройство формирует выходной сигнал по пи-закону, причем настройка коэффициентов К, и Kjj. независима В качестве запомингио(аих элементо в устройстве использовался электромагнитный модулятор света с фотоэлектрическим считыванием, функции элемента памяти может выполнять Любой активный запоминающий элемент с непрерывным токовым выходом.

Использование данного устройства для управления технологическими процессами улучшает качество регулирования, так как наличие пропорциональной составляющей является эффективным способом управления.

Формула изобретения

Интегрирующее устройство, содержащее два операционных усилителя, инвертирующий вход первого из которых соединен с заг«1каю1цим коН-тактом первого переключателя, через первый масштабный резистор - с разкыкгиощим контактом второго переключателя и через первый запоминающий элемент с замыкающим контактом второго переключателя, переключгиощий контакт которого подключен к выходу первого операциоиного усилителя, размыкающий контакт первого.переключателя соединен с инвертирующим входом второго операционного усилителя, подключенного через второй масштабный резистор к за|«2кающему контакту третьего переключателя, размыкающий контакт которого подключен через

О второй запоминающий элемент к инвертирующему входу второго операционного усилителя, выход.котсфого соединен с переключающим контактом третьего переключателя, а переключающий контакт первого переключателя через первый переменный масштабный резистор подключен ко входу устройства, и датчик временных интервалов, подключенный к управляющим входам пеQ реключателей, отличающееся тем, что, с целью расширения класса решаемых задач за счет формирования пропорциональной составляющей, в него дополнительно введены два переменных масштабных ре зистора, операционные усилители выполнены дифференциальными, причем их неинвертирующие входы через соответственно второй и третий переменные масштабные резисторы соединены

0 со входом устройства, а размыкающий контакт второго переключателя и закыкгисшсий контакт -третьего переключателя подклоочены к выходу устройства.

5

Источники информации, принятые во внимание Лри экспертизе

1.Розенблат М.А. Магнитные элементы автоматики и вычислительной

л техники. М., Наука, 1974, с.607609.

2.Авторское свидетельство СССР по заявке 2124758,кл.С 06 G 7/18, 1975 (прототип.) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Перемножающее устройство | 1987 |

|

SU1465896A1 |

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| Дискретный фильтр | 1982 |

|

SU1029186A1 |

| Функциональный преобразователь | 1978 |

|

SU781838A1 |

| Многоразрядное суммирующее устройство | 1976 |

|

SU602967A1 |

| Устройство для измерения электрических параметров четырехполюсника | 1978 |

|

SU767655A1 |

| Цифровой омметр | 1982 |

|

SU1046707A1 |

| Дискретный интегратор | 1975 |

|

SU705468A1 |

| ИНТЕГРАТОР | 1990 |

|

RU2020580C1 |

| Вычислительное устройство и запоминающий масштабно-суммирующий блок | 1980 |

|

SU1043670A1 |

Авторы

Даты

1981-03-15—Публикация

1979-01-15—Подача