Изобретение относится- к области автоматики и вычислительной техники и может быть использовано в адаптийИьгх сисд-емах управления и специализированных вычислительных машинах. При решении разностных уравнений и реализации алго{зитмов экстремального управления используются накапливающие схемы для выполнения операции суммирования, усреднения, автоматического ступенчатого изменения параметров, Известно экспоненциальное сглаживаю щее устройство, используемое для ступенчатого -изменения параметров при регистрации переменных в логарифмическом масштабе, состоящее из двух интеграторов, используемых как аналоговые элементы памяти, резисторов и ключей, в котором выход первого интегратора соединен со входом второго, а выход второ го через делитель соединен со входом первого, при этом задержанный выходной сигнал с определенным весом сумми руется на пеовом интеграторе с входным сигналом flj.,1 Недостатком указанного устройства являетсч то, что второй интенгратор пассивен, так как употребляются только для перезаписи сигнала с первого интегратора и его задержки. Известно также интегрирующее устройство, которое осуществляет последовательное суммирование входных и выхоп«-ных сигналов через равные интервалы времени. Оно содержит два аналоговых запоминающих устройства, компаратор| перекидные ключи на входах и выходах АЗУ 2. Недостатком данного устройства является большая сложность, так как каждое аналоговое запоминающее устройство представляет собой усилитель с резисторами, ключом, выпрямителем и запоминающим элементом на магнитном сердечнике. Наиболее близким к изобретению является устройство, содержащее запомн-

нающие блокиг,. каждый из Koropbjx выполнен на операционном усилителе, ко входу которого подключены запоминающий элемент и один вывод резистора обратной связи, а выходы запоминающих блоков через первый переключатель и переменный масштабный резистор соеди- ненбт со входом интегратора, второй переключатель, включенный на вьпгоде интегратора, и датчик временных интервалов, соединенный с управляющими входами переключателей.

Недостатком прототипа являетря его сложность и недостаточная точность, так как из-за того, что запоминающие блоки инвертируют знак, для обеспечение функционирования устройства необходим третий усилитель.

Цель изобретения - повышение точности и упрощение устройства.

Поставленная цель достигпется тем, что дискретный интегратор содержит допoднитeJ7ьный переменный масштабный резистор, а в каждый запоминающий блок введен ключ, переключающий контакт которого соединен с выходом операционного усилителя, замыкающий и размыкающий контакты ключа первого запоминающего блока соединены соответственно с запоминающш д элементом н другим выводом резистора обратной связи операционного усилителя этого блока, а замыкающий и размыкающий контакт ключа второго запоминающего блока соединены соответственно с другим выводом резистора обратной связи и с запоминающим элементом второго запоминающего блока, при этом размыкающий контакт ключа первого запоминающего блока и. замыкающий контакт ключа второго запоминающего блока подключены к выводам дополнительного переменного масштабного резистора и ко входам второго переключателя.

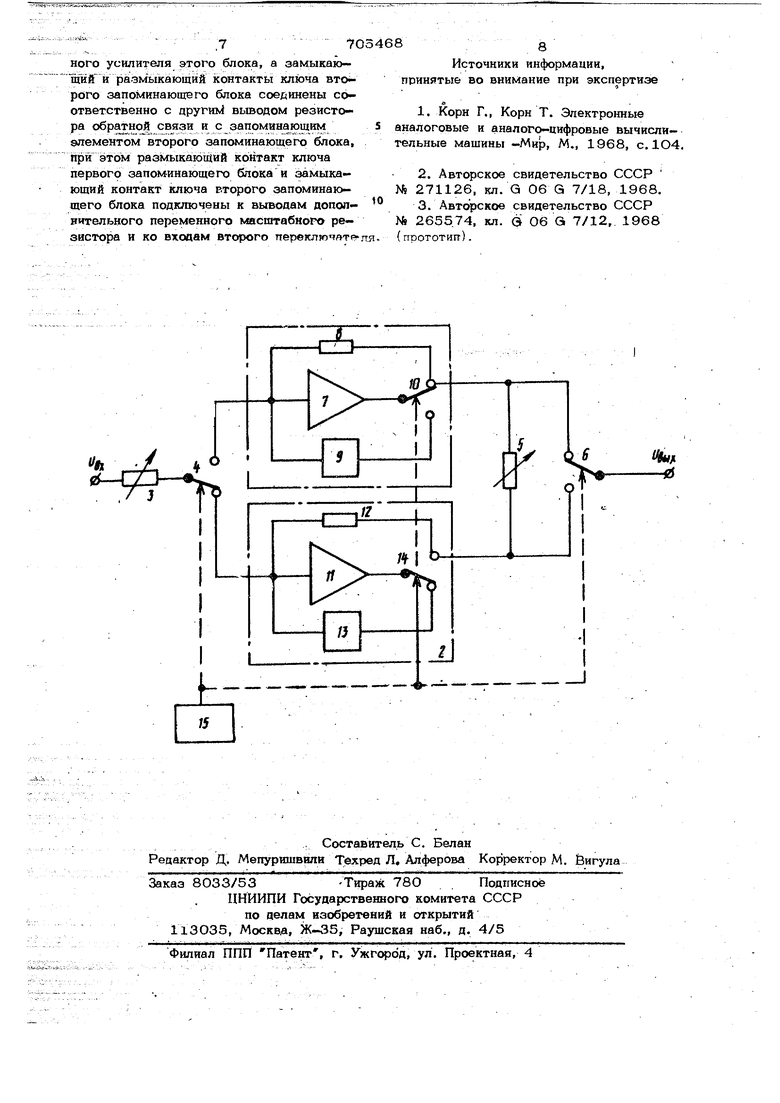

На чертеже представлена схема предлагаемого дискретного интегратора. Оа содержит: запоминающий блок 1, запоминающий блок 2, переменный масштабный резистор 3, первый переключат.ель 4, дополнительный переменный масштабный резистор 5 второй переключатель 6. Запоминающий блок 1 состоит из операционного усилителя 7 с резистором 8 обратной связи, запоминающего элемента 9 и 10. Запоминающий блок 2 состоит из операционного усилителя И с резистором 12 обратной связи, запо1у1инающего элемента 13 и ключа 14.

Датчик временных интервалов 15 управляет ключами..

Дискретный интегратор - фильтр реализует алгоритм:

вх( -Т).

1 1,2,3,...,

IJBb.)

- выходное напряжение

0 где в момент отсчета ii;

UaxHiV

- входное напряжение в момент tj ;

.-т) - выходное напряжение в -предыдущйй отсчет () ; Т - интервал квантования; ( - коэффициент передачи

входного сигнала; К2 - коэффициент передачи

выходного сигнала. В исходном состоянии переключатель 4 и ключ 14 находятся в нижнем положении, переключатель 6 и ключ 10 - в верхнем положении. Выходной сигнал считывается с усилителя 7 запоминающего блока 1. Входной сигнал подается через резистор 3 и переключатель 4 на вход усилителя 11 запоминающего блока 2. При этом он умножается на коэффициент К , подбираемый с помощью переменного резистора 3 и резистора 12 и удовлетворяющий равенству К Обратная связь усилителя 11 разорвана и с резистора 12 на а го вход подается вЬ1ходной сигнал с запоминающего блока 1 через переменный резистор 5, определяющий совместно с резистором 12 коэффициента передачи выходного сигнала

. находится в режиме слежения. На его выходе

образуется напряжение ошибки, величина и знак которого определяются входными сигналами. Это напряжение через ключ .14 подается на вход запоминающего элемента 13. В контуре записи обеспечивается отрицательная обратная связь. Под действием управляющего напряжения запоминающий элемент 13 отрабатыва,ет эту ошибку, в результате чего уравниваются токи во входной цепи усилителя 11.

В следующем такте в режим слежения (записи) переводится запоминающий блок 1, а в режим считывания - запоминающий блок 2. Переключатель 4 и ключ 14 переводятся в верхнее положение, а переключатель 6 и ключ 10 - нижнее. Записанный сигнал считывается через пе- ре лючатель 6 с выхода усилителя 11. Входной сигнал поступает через резистор 3 с весом К переключатель 4 на вход усилителя 7. Обратная связь, осуществляемая через резистор 8 - разорвана. Высодной сигнал с запоминающего блока 2 с весом через переменный резистор 5 и резистор 8 также подается на вход усилителя 7. Суммарное напряжение с выхода усилителя 7 лодается на вход запоминающего элемента 9, отрабатывающего этот сигнал. После следующего-срабатывания всех контактов весь шкл повторяется. Если сопротивление переменного резистора 5 равно , то коэффициент передачи выходного сигнала K-, / СЯ 6-vTZjVR |R 81 Kgttl устройство работает в режиме дискретного интегрирования. На выходе при этом имеем: . Благодаря тому, что в предлагаемом устройстве резисторы 8 и 12 используются в режиме записи выходного сигна- .ла как входные, а в режиме считывания записанных сигналов - как резисторы обратной связи, достигается автоматическая установка коэффициентов передачи сигналов ме-,хпу запоминающими бл.оками 1 и 2, равных единице. Постоянная времени интегрирования зависит от коэффициента передачи вхоД ного Сигнала К /J и интервала квантования Т и равна Т . При использовании устройства в адаптивных системах, когда объект нестацио:нарен, не имеет смысла брать результаты опытов с одинаковым .весом, так как ценность старой информации значительно ниже новой, потому что стррые данные могут не соответствов.ать деиствительности. В этих случаях необходим алгоритм забывающий старые значения Напрймер, в алгоритме с экспоненциальной памятью слагаемые, входящие 6 су1«- му, берутся с весом, экспоненциально /бы вающим по мере удаления от момента -fc . . Аналогична этому алгоритму и формула рекуррентного уравнения экепотГёнШального сглаживания первого порядка,ПриК оСиКгИ-оС предлагаемый дискретный интегратор реализует алгоритмы экспоненциального сглаживания: (t,r-ocu /4.,,), 7 8 где сС - коэффициент сглаживания. Так как запоминаюишё элементы 9 и v 13 в режиме записи компенсируют входные сигналы, на выходе усилителей 7 и Ц в режиме считывания образуются после инвертирования выходные сигналы той же полярности, что и входные. , Поэтому предлагаемое устройство в третьем инвертирующем усилителе не нуждается. Предлагаемый дискретный интегратор обладает рядом преимуществ по сравнению с устройством для скользящего усреднения переменного параметра. Благодаря наличию ключей на выходах каждого из усилителей запоминающих блоков и связи между ними через переменный резистор удалось, при использовании устройства в режиме интегрирования (сопротивление резистора 5 равно нулю) автоматически получать коэффициенты передачи между этими блоками, равные единице. Это также облегчает использо- ванне устройства и в режиме сглаживания, так как требует меньщего числа настроек. Предлагаемое устройство обладает теми же функциональными возможностями, что и прототип, однако содер- жит на 1 усилитель и на 3 резистора меньше. Формула изобретения Дискретный интегратор, содержащий запоминающие блоки, каждый из которых выполнен на операционном усилителе, ко входу которого подключены запоминаю-. щий элемент и один вывод резистора обратной связи, входы запоминающих блоков через первый переключатель и переменный масштабный резистор соединены со входом интенгратора, второй переключатель, включенный на выходе интегратора и датчик временных интервалов, соединенный с управляющими входами переключателей, отличающийся тем, что, c целью повьплёния точности Упрощения устройства, он содержит дополнительный переменный масщтабный резистор, а в каждый запоминающий блок введен ключ, переключающий контакт которого соединен с выходом операдионно . замыкающей размыкающий контакты ключа первого запоминающего блока соединены соответственно с запоминающим элементом и другим выводом резистора обратной свя,зи операцион- 770 . ,-. -. ного усилителя этого блока, а замыкающий и ра-змыкающйй контакты ключа вто рого запоминающего блока соединены соответственно с другик вьтодом резистора обратной связи и с запоминающим элементом второго запоминающего блока, при этЬм размыка ющий контакт ключа первого запоминающего блока и замыкающий контакт ключа второго запоминающего блока подключены к вьтодам дополнительного переменного масштабного резистора н ко входам второго переключите 8 Источники информации, принятые во внимание при экспертизе 1. Корн Г., Корн Т. Электронные аналоговые и аналого-цифровые вычислительные мащины -Мир, М., 1968, с.1О4. 2.Авторское свидетельство СССР 271126, кл. Q 06 G 7/18, 1968. 3.Авторское свидетельство СССР № 2655,74, кл. G 06 в 7/12, 1968 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующее устройство | 1979 |

|

SU813454A1 |

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| Устройство для моделирования упругого гистерезиса | 1980 |

|

SU966708A1 |

| Дискретный фильтр | 1982 |

|

SU1029186A1 |

| Логарифмический аналого-цифровой преобразователь | 1985 |

|

SU1277146A1 |

| Интегратор | 1979 |

|

SU847330A1 |

| Интегратор | 1985 |

|

SU1298775A1 |

| Устройство для моделирования упругого гистерезиса | 1986 |

|

SU1397946A1 |

| Устройство для интегрирования знакопеременных сигналов | 1981 |

|

SU962991A1 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112375A1 |

ж Jf I

Авторы

Даты

1979-12-25—Публикация

1975-04-07—Подача