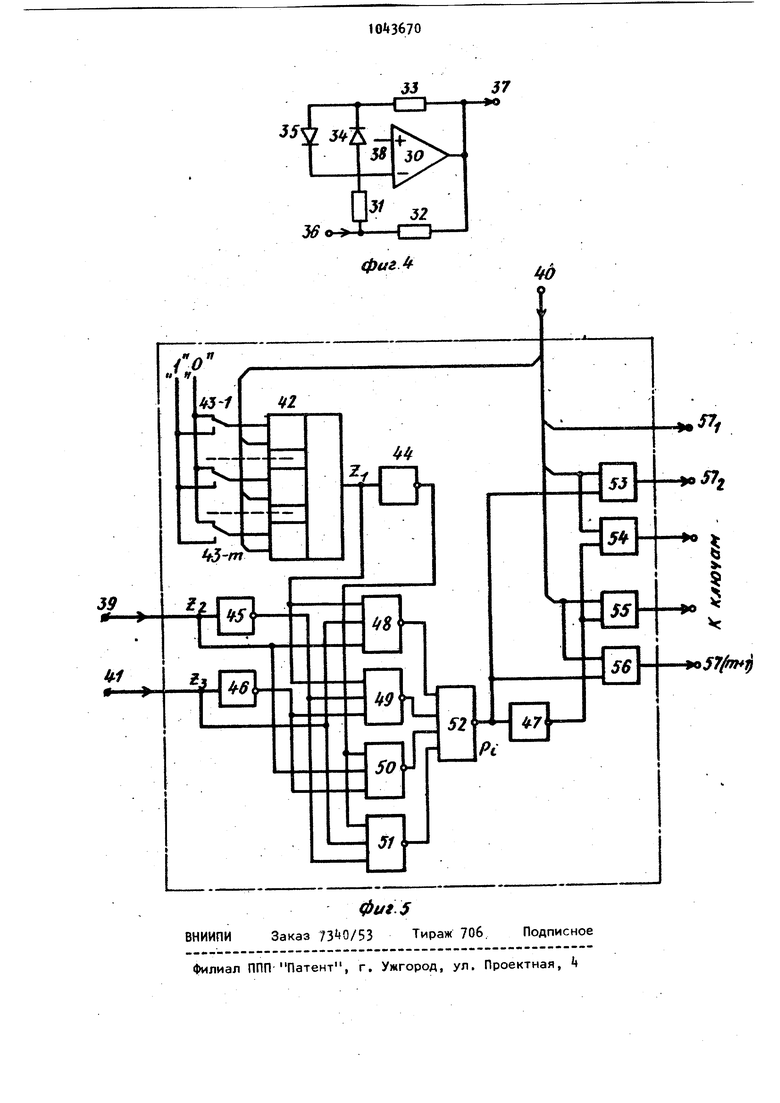

усилитель, неинвертирующии вход которого соединен с шиной нулевого потенциала, между инвертирующим входом и выходом операционного усилителя подключены соединенные последовательно первый и второй масштабные резисторы, к инвертирующему входу операционного усилителя подключен анод первого логарифмующего диода катод которого через третий масштабный рези ст.ор соединен с выходом операционного усилителя, который является выходом преобразователя, вт&рой вывод первого масштабного резистора является входом преобразователя, второй логарифмирующий диод, катод и йнод которого соединены соответственно с анодом и катодом первого логарифмирующего диода.

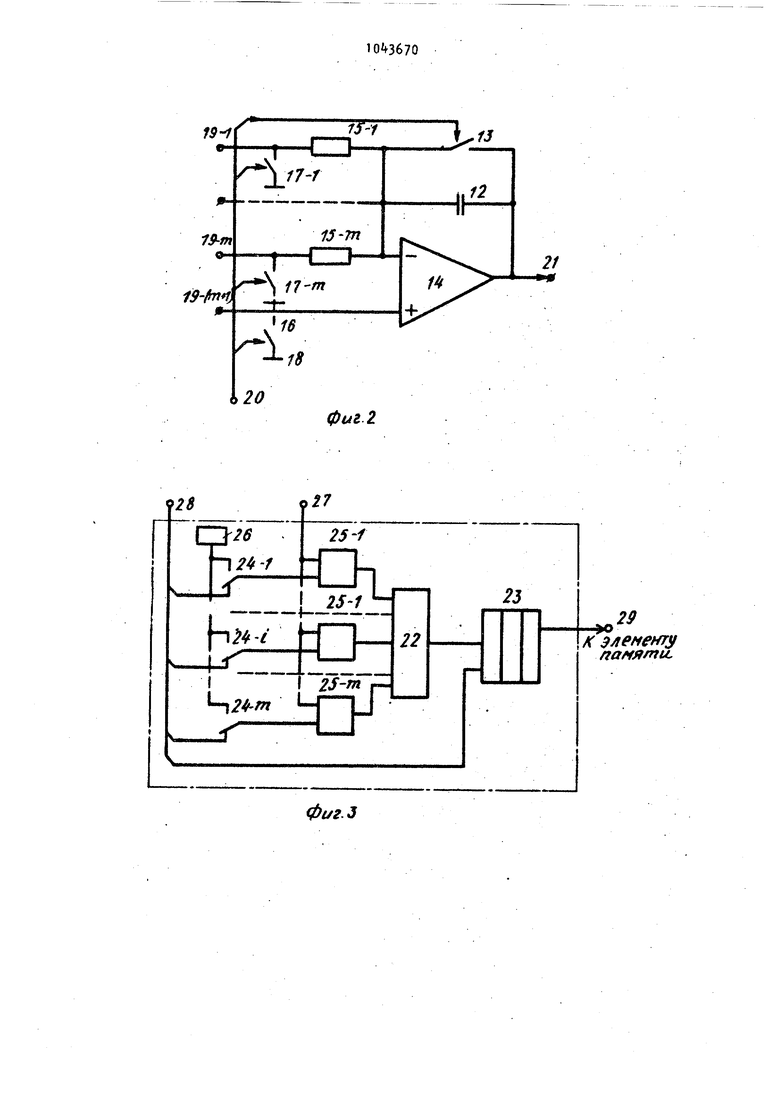

3. Устройство по п. 1, о т л и чающееся тем, что блок вычисления знака результирующего сигнала содержит одноразрядный двоичный счетчик, информационный вход которого подключен к выходу элемента ИЛИ, tn двухпозиционных переключателей и mэлементов И, установочный вход одноразрядного двоичного счетчика и первые входы двухпозиционных переключателей образуют управляющий вход блока, вторые входы двухпозиционных переключателей подключены к источнику логического О, первые входы элементов И объединены и являются информационным входом блока, выходы двухпозиционных переключателей соединены с вторыми входами соответствующих элементов И, выходы которых подключены к входам элемента ИЛИ, выход Одноразрядного двоичного счетчика является выходом блока.

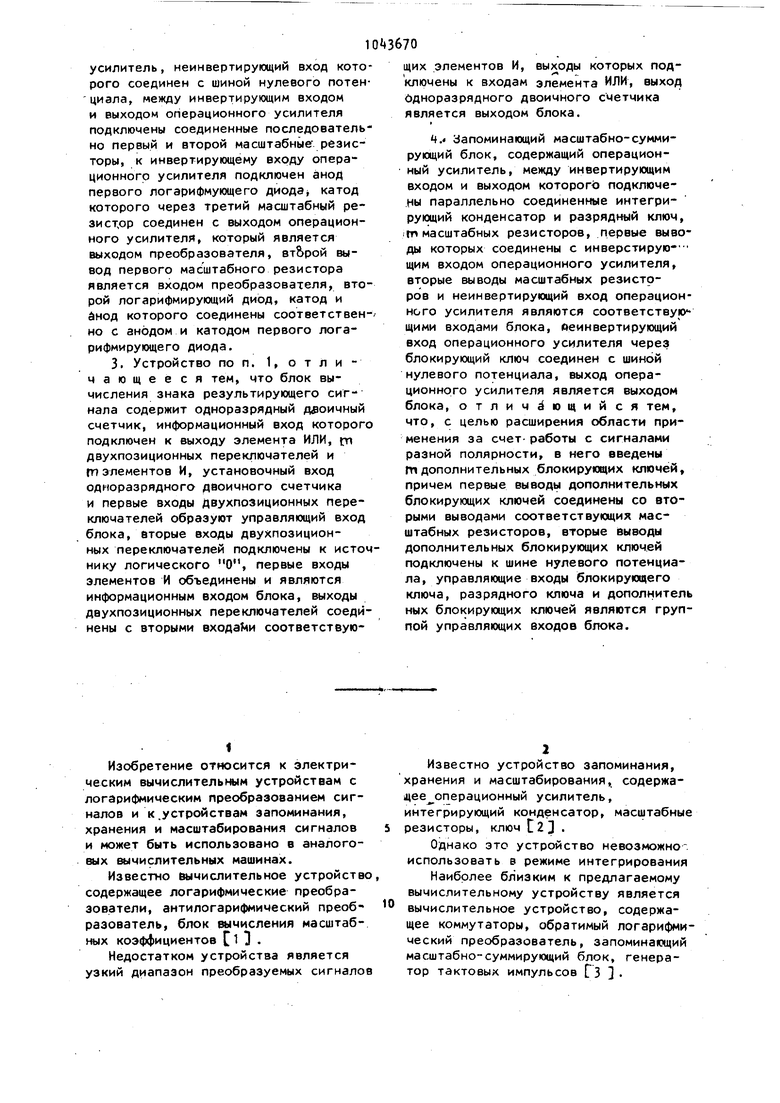

Ч. Запоминающий масштабно-суммирующий блок, содержащий операционный усилитель, между инвертирующим входом и выходом которого подключены параллельно соединенные интегрирующий конденсатор и разрядный ключ, im масштабных резисторов, первые выводы которых соединены с инверстирую- щим входом операционного усилителя, вторые выводы масштабных резисторов и неинвертирующий вход операционного усилителя являются соответствую щими входами блока, оеинвертирующий вход операционного усилителя через блокирующий ключ соединен с шиной нулевого потенциала, выход операционного усилителя является выходом блока, отличающийся тем, что, с целью расширения области применения за счет-работы с сигналами разной полярности, в него введены mдополнительных блокирующих ключей, причем первые выводы дополнительных блокирующих ключей соединены со вторыми выводами соответствующих масштабных резисторов, вторые выводы дополнительных блокирующих ключей подключены к шине нулевого потенциала, управляющие входы блокирующего ключа, разрядного ключа и дополнител ных блокирующих ключей являются группой управляющих входов блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1981 |

|

SU978159A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Логарифмический преобразователь | 1982 |

|

SU1064283A1 |

| Логарифмический аналого-цифровой преобразователь | 1985 |

|

SU1277146A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| Логарифмический преобразователь (его варианты) | 1982 |

|

SU1078442A1 |

| Логарифмический преобразователь | 1983 |

|

SU1166146A1 |

| Логарифмический преобразователь | 1970 |

|

SU868785A2 |

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

| Аналоговый логарифмический преобразователь | 1980 |

|

SU934499A1 |

Изобретение относится к электрическим вычислительным устройствам с логарифмическим преобразованием сигналов и к.устройствам запоминания, хранения и масштабирования сигналов и может быть использовано в аналоговых вычислительных машинах.

Известно вычислительное устройство содержащее логарифмические преобразователи, антилогарифмимеский преоб разователь, блок вычисления масштабных коэффициентов СОНедостатком устройства является узкий диапазон преобразуемых сигналов

Известно устройство запоминания, хранения и масштабирования, содержащее огперационный усилитель, интегрирующий конденсатор, масштабные резисторы, ключ С2 .

Однако это устройство невозможно , использовать в режиме интегрирования

Наиболее близким к предлагаемому вычислительному устройству является вычислительное устройство, содержащее коммутаторы, обратимый логарифмический преобразователь, запоминающий масштабно-суммирующий блок, генератор тактовых импульсов Гз

Наиболее близким по техническому решению к запоминающему масштабносуммирующему блоку является запоминающий масштабно-суммирующий блок, содержащий операционный усилитель, интегрирующий конденсатор, разрядный и блокирующий ключи, масштабные резисторы L .

Недостатком устройства является узка;я область применения.

Целью изобретения является расширение области применения за счет работы с сигналами разной полярности

С этой целью в вычислительное устройство, содержащее первый коммут татор, вход-выход которого соединен со входом обратимого логарифмического преобразователя, выход которого подключен к входу-выходу второго коммутатора, запоминающий масштабносуммирующий . блок , выход которого подключен к одному из информационнь1х входов-выходов второго коммутатора, другие информационные входы-выходы. которого соединены со входами запЪминающего масштабно-суммирующего блока, один из информационных входов-выходов первого коммутатора является выходом устройства, другие информационные входы-выходы первого коммутатора являются соответствующими входами устройства, управляющие входы первого и второго коммутаторов соединены с выходом генератора тактовых импульсов, введены блок определения знака, блок памяти, блок вычисления знака результирующего сигнала, формирователь тактовых импульсов режимов суммирования, причем обратимый логарифмический преобразователь выполнен двухполярным, вход-выход второго коммутатора соединен со входом блока определения знака, выход которого подключен к информационному входу блока вычисления знака результирующего сигнала и. к первому входу формирователя тактовых импульсов режимов суммирования, управляющие входы которых и управляющий вход блока памяти соединены с выходом ген ратора тактовых импульсов, выход блока вычисления знака результирующего сигнала подключен к информационному входу блока памяти, выход KOTOрого соединен с вторым входом формирователя тактовых импульсов режимов суммировакия, выходы которого подключены к группе управляющих входов Запоминающего масштабно-суммирующего блока.

Обратимый двухполярный логарифмический преобразователь содержит операционный усилитель, неинвертирующий вход которого соединен с шиной нулевого потенциала, между инвертирующим входом и выходом операционного усилителя подключены соединенные последовательно первый и второй масштабные резисторы, к инвертирующему входу операционного усилителя подключен анод первого логарифмирующего диода, катод которого через третий масштабный резистор соединен с выходом операционного усилителя, который является выходом преобразователя, вто5рой вывод первого масштабного резистора является входом преобразователя второй логарифмирующий диод, катод и анод которого соединены соответствент но с анодом и катодом первого лога0рифмирующего диода.

лок вычисления знака результирующего сигнала содержит одноразрядный двоичный счетчик, информационный вход которого подключен к выходу

5 элемента ИЛИ,т двухпозиционных переключателей и jm эелментов И, устано|вочный вход одноразрядного двоичного ;счетчика и первые входы двухпози-щионных переключателей образуют

0 управляющий вход блока, вторые входы двухпозиционных переключателей подключены к источнику логического О первые входы .элементов И объединены и являются информационным входом

5 блока, выходы двухпозиционных переключателей соединены совторыми входами соответствующих элементов И. выходы которых подключены ко входам элемента ИЛИ, выход одноразрядного

0 двоичного счетчика является выходом блока.

В запоминающий масштабно-суммирующий блок, содержащий операционный усилитель, между инвертирующим входом

5 и выходом которого подключены параллельно соединенные интегрирующий конденсатор и разрядный ключ,/ масштабных резисторов, первые выводы которых соединены с инвертирующим

0 входом операционного усилителя, вторые выводы масштабных резисторов и неинвертирующий вход операционного усилитеяя являются соответствующими входами блока, неинвертирующий

5 вход операционного усилителя через блокирующий ключ соединен с шиной нулевого потенциала, выход опера- ционного усилителя является выходом

блока, введены hi дополнительных блокирурощих ключей, причем первые выводы дополнительных блокирующих ключей соединены со вторыми выводами соответствующих масштабных резисторов, вторые выводы дополнительных блокирующих ключей подключены к шине нулевого потенциала, управляющие входы блокирующего ключа, разрядного ключа и дополнительных блокирую щих ключей являются группой управляющих входов блока.

о

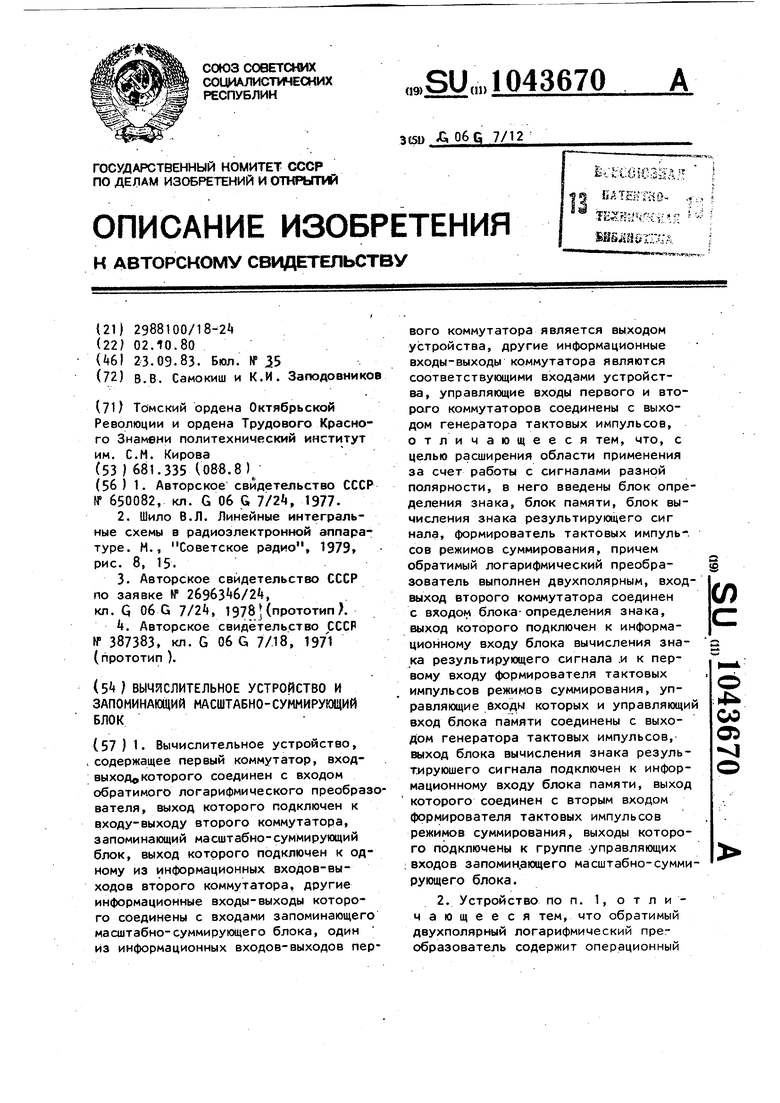

На фиг. 1 изображена функциональная схема логарифмического вычислительного устройства} на фиг . 2 функциональная схема запоминающего масштабно-суммирующего блока, Иа фиг. 3 функциональная схема блокавычисления знака результирующего сигнала; на фиг. t - функциональная схема обратимого двухполярного логарифмического преобразователя на фиг, 5 - схема формирователя тактовы импульсов режимов суммирования.

Устройство содержит первый ком/мутатор 1, логарифмический преобразователь 2, второй коммутатор 3, запоминающий масштабно-суммирующий блок i, блок 5 определения знака, блок 6 вычисления знака результирующего сигнала, формирователь 7 тактовых импульсов режимов суммирования, блок 8 памяти, генератор 9 тактовых импульсов, входы 10, ..., 10,..., выход 11 устройства, интегрирующий конденсатор 12, разрядный ключ 13| операционный усилитель Н, масштабные резисторы 15,.. ., 15 блокирующий ключ 16, дополнительные блокирующие ключи 17,... 17. шину 18 нулевого потенциала, входы 19-,,..., 19, 19т-и1 управляющие входы 20 и выход 21 запоминающего масштабно-суммирующего блока, элемен ИЛИ 22, одноразрядный двоичный счетчик 23, двухпозиционные переключател 2+,,,..., 2,..., , элементы И ;25,..., 25i-,..., 2, источник

26сигнала логического О, первый

27и второй 28 входы блока 29 вычисления знака результирующего сигнала, операционный усилитель 30, первый, второй и третий масштабные резисторы

31 - 33, логарифмирующий диод 3, дополнит,ельный логарифмический диод 35, вход Зб и выход 37 обратимого двухполярного логарифмического преобразователя, шину 38 нулевого потенциала. .

Формирователь 7 тактовых импульсов режимов суммирования сожержит первый, второй и третий входы 39, 40 и fl, многввходовой элемент И-НЕ k2, двухпозиционные переключатели ,... инверторы -Ц7, элементы И 4856, выходы 57,..., .

Вычислительное устройство работает

по логарифмическому алгоритму п

i zantiPog IZn.. , (1)

1

Х4- входные сигналы;

где h ,-- показатель степени. При работе устройство моделирует выражение вида (

У П х.. (2)

Входные сигналы через первый коммутатор 1 поочередно, по тактам, задаваемым генератором 9 тактовых импульсов, поступают на лога0ифмически преобразователь 2. Логарифмы входных сигналов через второй коммутатор 3 поступают на запоминающий масштабно-суммирующий блок 4. Блок 5 определения знака в каждый такт логарифмирования входных сигналов определяет их полярность. Блок 6 вычисления знака результирующего сигнала по выходным сигналам блока 5 определния знака, а также в соответствии с видом реализуемого выражения (2 ) с учето знака показателя степени этого сигнала, к концу каждого цикла работы определяет знак результирую1цего сигнала, информацию о котором запоминает на время следующего цикла блок 8 памяти.

Формирователь 7 тактовых импульсо режимов суммирования в каждый такт логарифмирования какого-либо из входных сигналов в соответствии со знаком показателя степени, с каким этот сигнал входит в выражение (2), с полярностью этого сигнала и знаком результирующего сигнала, определенны в предшествующий цикл работы, определяет режим суммирования логарифма входного сигнала в запоминающем масштабно-суммирующем блоке 4, т.е. полярность, с которой он вводится в линейную комбинацию логарифмов входных сигналов.

В т+ 1 такт цикла работы производится операция потенцирования сум7Юкм логарифмов входных сигналов, знак которой сооответствует знаку результаВыходной сигнал запоминающего масштабно-суммирующего блока через второй коммутатор 3 поступает на логарифмический преобразователь 2, работающий в этом режиме на потенцирование. этом на выходе первого коммута тора-1 формируется результат преобразования .

Фи1 f О Формирователь тактовых.импульсов режимов суммирования является логическим автоматом, работа которого сведена в таблицу. По сравнению с известным предлагаемое логарифмическое вычислительное устройство обладает новым качеством так как оно работает с сигналами любой полярности, причем достижению этого эффекта способстЪует и техни.ческое решение запоминающего масштабносу ммирующе го блока.

фиг 2

фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логарифмическое вычислительное устройство | 1977 |

|

SU650082A1 |

| Прялка для изготовления крученой нити | 1920 |

|

SU112A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Линейные интегральные схемы в радиоэлектронной аппаратуре | |||

| М., Советское радио, 1979, рис | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-09-23—Публикация

1980-10-02—Подача