I

Изобретение относится к аналоговой и гибридной вычислительной технике.

Известно устройство для суммирования и вычитания , содержащее решающий усилитель с входными резисторами н резистором в обратной связи, в котором каждое слагаемое представлено в виде на пряжения. Недостатком этого устройства является низкая точность вычислений.

Нанболее близким к изобретению по технивеской сущности является многоразрядное суммирующее устройство (2), содержащее суммирующий усилитель с первым масштабным резистором обратной связи, выход которого через функциональный преобразователь соединен с выходом устройства, вход сум латора соединен с выходами управляемых ключей, входы которых через соответствующие масщтабные резисторы соединены с первой группой входов устройства, вторая группа входов которого соедннена с управляющими входами управляемых ключей.

Указанное устройство позволяет повысить точность, однако является сравнительно сложным.

Для упрощения конструкции прн условии сохранения цифровой точности предлагаемое

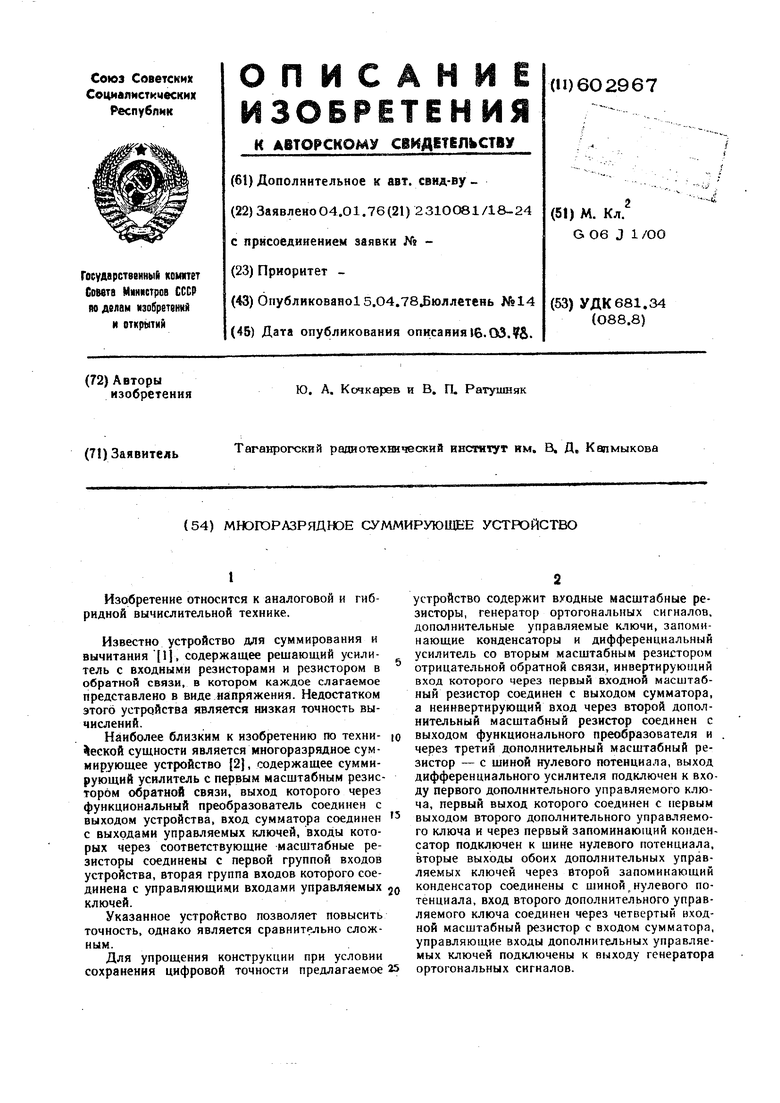

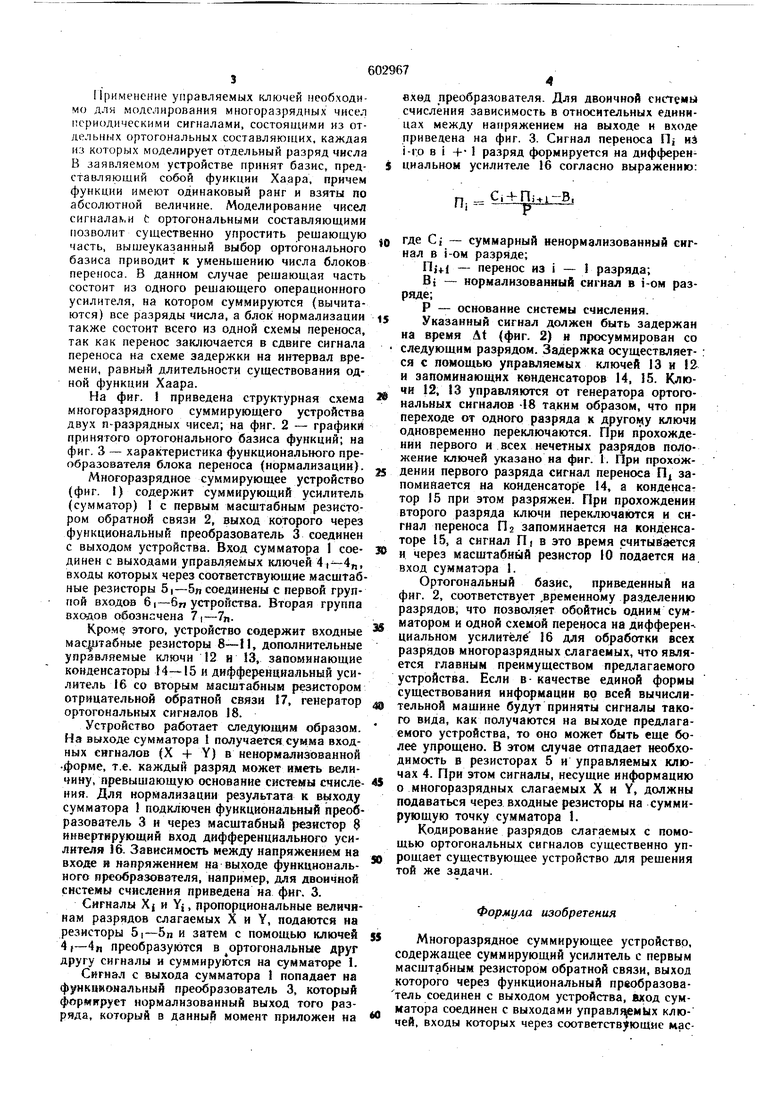

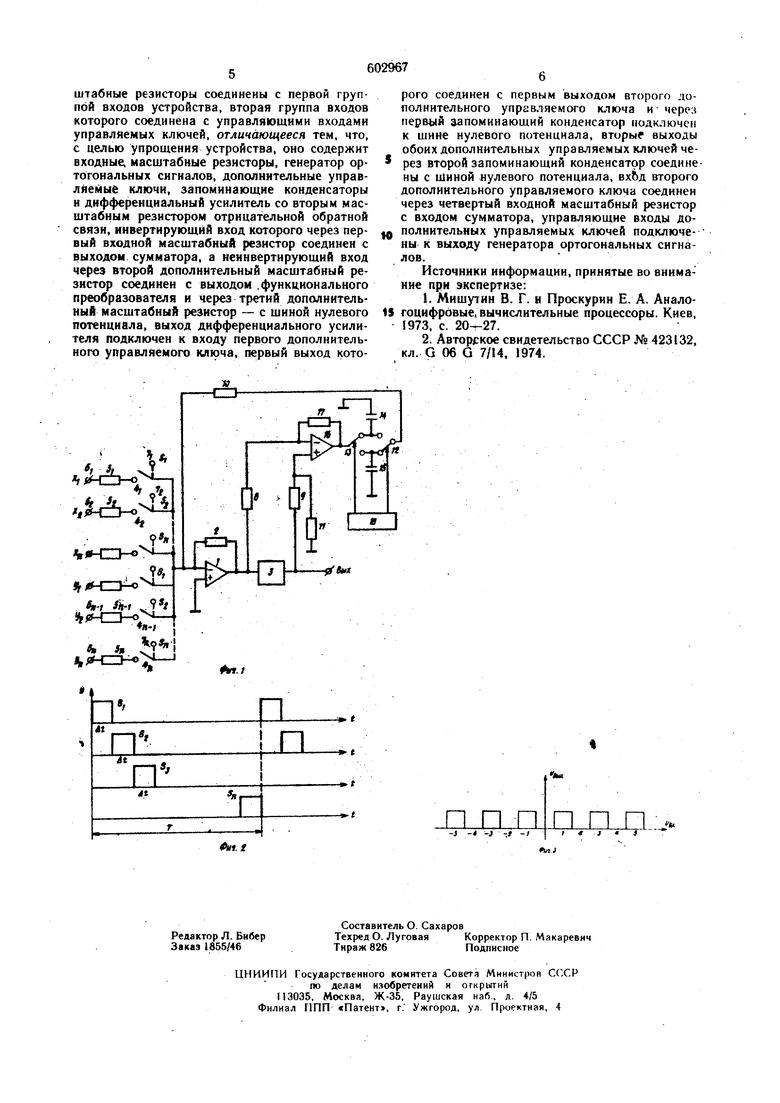

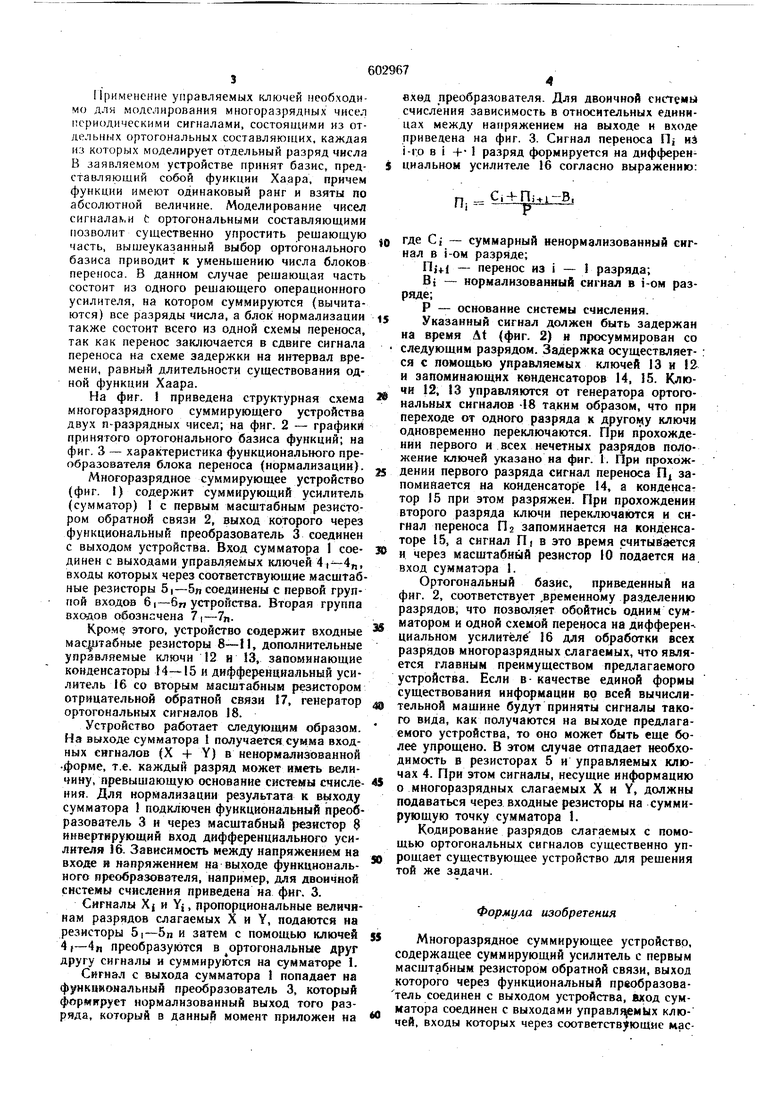

устройство содержит входные масштабные резисторы, генератор ортогональных сигналов, дополнительные управляемые ключи, запоминающие конденсаторы и дифференциальный усилитель со вторым масщтабным резистором отрицательной обратной связи, инвертирующий вход которого через первый входной масштабный резистор соединен с выходом сумматора, а неинвертирующий вход через второй дополнительный масщтабный резистор соединен с выходом функционального преобразователя и через третий дополнительный масщтабиый резистор - с щнной нулевого потенциала, выход дифференциального усилнтеля подключен к входу первого дополнительного управляемого ключа, первый выход которого соединен с первым выходом второго дополнительного управляемого ключа и через первый запоминающий конденсатор подключен к щине нулевого потенциала, вторые выходы обоих дополнительных управляемых ключей через второй запоминающий конденсатор соединены с шиной нулевого потенциала, вход второго дополнительного управляемого ключа соединен через четвертый входной масштабный резистор с входом сумматора, управляющие входы дополнительных управляемых ключей подключены к выходу генератора ортогональных снгналов. Применение управляемых ключей необходимо для моделирования многоразрядных чисел периодическими сигналами, состоящими из отдельных ортогональных составляющих, каждая из которых моделирует отдельный разряд числа В заявляемом устройстве принят базис, предctaвляIpший собой функции Хаара, причем функции имеют одинаковый ранг и взяты по абсолютной величине. Моделирование чисел сигнала,и С ортогональными составляющими позволит существенно упростить решающую часть, вышеуказанный выбор ортогонального базиса приводит к уменьшению числа блоков переноса. В данном случае решающая часть состоит нз одного рещающего операционного усилителя, на котором суммируются (вычитаются) все разряды числа, а блок нормализации также состоит всего из одной схемы переноса, так как перенос заключается в сдвиге сигнала переноса на схеме задержки на интервал времени, равный длительности существования одной функции Хаара. На фиг. I приведена структурная схема многоразрядного суммирующего устройства двух п-разрядных чисел; на фиг. 2 - графики принятого ортогонального базиса функций; на фиг. 3 - характеристика функционального преобразователя блока переноса (нормализации). Многоразрядное суммирующее устройство (фиг. I) содержит суммирующий усилитель (сумматор) 1 с первым масщтабным резистором обратной связи 2, выход которого через функциональный преобразователь 3 соединен с выходом устройства. Вход сумматора 1 соединен с выходами управляемых ключей 41-4, входы которых через соответствующие масштабные резисторы 5i-5п соединены с первой группой входов 6|-бп устройства. Вторая группа входов обозначена 7|-7п. Кро.м этого, устройство содержит входные масштабные резисторы , дополнительные управляемые ключи 12 и 13, запоминающие конденсаторы 14-15 и дифференциальный усилитель 16 со вторым масштабным резистором отрицательной обратной связи 17, генератор ортогональных сигналов 18. Устройство работает следующим образом. На выходе сумматора t получается сумма входных сигналов (X -f Y) в ненормализованной форме, т.е. каждый разряд может иметь величину, превышающую основание системы счисления. Для нормализации результата к выходу сумматора 1 подключен функциональный преобразователь 3 и через масштабный резистор $ инвертирующий вход дифференциального усилителя 16. Зависимость между напряжением на входе и напряжением на выходе функционального преобразователя, например, для двоичной системы счисления приведена на фиг. 3. Сигналы Xj и Yj, пропорциональные величинам разрядов слагаемых X н У, подаются на резисторы 5|-5п и затем с помощью ключей 4f-4п преобразуются в ортогональные друг другу сигналы и суммируются на сумматоре 1. Сигнал с выхода сумматора 1 попадает на функциональный преобразователь 3, который формирует нормализованный выход того разряда, который в данный момент приложен на ехед преобразователя. Для двоичной снстемь счисления зависимость в относительных единицах между напряжением на выходе и входе приведена на фиг. 3. Сигнал переноса Hj из i-ro в i -)- 1 разряд формируется на дифференциальном усилителе 16 согласно выражению: П C.-f , ,,. -р. где С, суммарный ненормализованный сигнал в i-OM разряде; П,Ч1 - перенос из i - 1 разряда; Bj - нормализованный сигнал в i-ом разряде;Р -- основание системы счисления. Указанный сигнал должен быть задержан на время At (фиг. 2) н просуммирован со следующим разрядом. Задержка осуществляет- : ся с помощью управляемых ключей 13 и 2 и запоминающих кенденсаторов 14, 15. Ключи 12, 13 управляются от генератора ортогональных сигналов -18 таким образом, что при переходе от одного разряда к другол|у ключи одновременно переключаются. При прохождении первого и всех нечетных разрядов положение ключей указано на фиг. 1. При прохождении первого разряда сигнал переноса П запоминается на конденсаторе 14, а конденсатор 15 при этом разряжен. Прн прохождении второго разряда ключи переключаются и сигнал переноса Пг запоминается на конденсаторе 15, а сигнал П( в это время считывается н через масштабный резистор 10 подается на вход сумматора 1. Ортогональный базис, приведенный на фиг. 2, соответствует .временному разделению разрядов, что позволяет обойтись одним сумматором и одной схемой переноса на днфференциальном уснлитёлё J6 для обработки всех разрядов многоразрядных слагаемых, что является главным преимуществом предлагаемого устройства. Если в-качестве единой формы существования информации во всей вычислительной мащнне будут приняты снгналы такого вида, как получаются на выходе предлагаемого устройства, то оно может быть еще более упрощено. В этом случае отпадает необходнмость в резисторах 5 и управляемых ключах 4. При этом сигналы, несущие информацию о многоразрядных слагаемых X и У, должны подаваться через входные резисторы на суммирующую точку сумматора 1. КодированНе разрядов слагаемых с помощью ортогональных сигналов существенно упрощает существующее устройство для рещення той же задачи. Формула изобретения Многоразрядное суммирующее устройство, содержащее суммирующий усилитель с первым масщтабным резистором обратной связи, выход которого через функциональный првобразователь соединен с выходом устройства, вход сумматора соединен с выходами управляемых ключей, входы которых через соответствующие маештабные резисторы соединены с первой группой входов устройства, вторая группа входов которого соединена с управляющими входами управляемых ключей, отличающееся тем, что, с целью упрощения устройства, оно содержнт входные, масштабные резисторы, генератор ортогональных сигналов, дополнительные управляемые ключи, запоминающие конденсаторы и дифференциальный усилитель со вторым масшт абным резистором отрицательной обратной связи, инвертирующий вход которого через первый входной масштабный резистор соединен с выходом сумматора, а неинвертирующий вход через второй дополнительный масштабный резистор соедииен с выходом .функционального преобразователя и через третий дополнительный масштабный резистор - с шиной нулевого потенциала, выход дифференциального усилителя подключен к входу первого дополнительного управляемого ключа, первый выход котоfffvx

А«./

рого соединен с первым выходом второго дояолннтельного управляемого ключа и череа первый аапоминаюший конденсатор подключен к шине нулевого потенциала, вторы выходы обоих дополнительных управляемых ключей через второй запоминающий конденсатор соединены с шиной нулевого потенциала, вхЬд второго дополнительного управляемого ключа соедииен через четвертый входной масштабный резистор с входом сумматора, управляющие входы дополнительных управляемых ключей подключены к выходу генератора ортогональных сигналов.

Источники информации, принятые во внимание при экспертизе:

1.Мишутин В. Г. н Проскурин Е. А. Аналогоцифровые, вычислительные процессоры. Киев

1973, с. .

2.Авторское свидетельство СССР № 423132, кл. G 06 G 7/14, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоразрядное множительное устройство | 1977 |

|

SU721837A1 |

| Многоразрядное устройство для алгебраического суммирования | 1981 |

|

SU1056214A1 |

| Многовходовый одноразрядный двоичный сумматор | 1973 |

|

SU462179A1 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| Многоразрядный функциональный преобразователь | 1975 |

|

SU585506A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU645206A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Генератор сигналов для формирования управляющих токов доменной памяти | 1989 |

|

SU1725255A1 |

| Время-импульсный амплитудный преобразователь | 1978 |

|

SU752796A1 |

| ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2002 |

|

RU2228540C1 |

Л./

О.

п п п -j.

I f I S

-i -t -) -I -I

Авторы

Даты

1978-04-15—Публикация

1976-01-04—Подача