Изобретение откосится к частотноселективньом устройствам, а именно к многоканальным цифровым фильтрам, и может быть использовано в системах обработки информации частотных датчиков с целью разделения по каналам последовательностей полос частот сле дования импульсов для .зьщачи соответствующих исполнительных команд. Известны цифровые фильтры для -выделения полос частот с заданными средними частотами и границами полос пропускания. Известно устройство, представляющее собой систему цифровых фильтров, каждый из которых настроен на згщанную область частот и имеет общий кварцевый генератор импульсов эталон ной частоты L1. Однако данное устройство достаточ но сложно и требует тщательной настройки . Наиболее близким к предлагаемому по технической сущности является уст ройство, содержащее счетчик, счетный вход которого соединен с выходом генератора эталонной частоты, и п параллельно включенных каналов фильтра :ции, каждый из которых состоит -из дешифратора, элемента памяти и элемента совпадения, выход которого соединен с первым входом накопителя f2. Недостаток устройства заключается в том, что возникающий случайно на выходе устройства ложный сигнал, например, в результает сбоя каких-либо элементов схемы, а также помех по цепи питания или входного сигнгша, будет присутствовать в течение всего времени, пока дешифратор несколько раз не примет одно из фиксированных состояний. Кроме,того, указанное устройство не позволяет обрабатьшать входной сигнал, частота которого изменяется непрерывно. Цель изобретения - повышение помехоустойчивости. Для этого в многоканальный полосовой цифровой фильтр, содержащий счетчик, счетный вход которого соединен с.выходом генератора эталонной частоты, и г1 параллельно включенных каналов фильтрации, каждый из которых состоит из дешифратора, элемента памяти и элемента .совпадения, выход которого соединен с первым входом накопителя, введены синхронизатор, распределитель частоты., дойолнительный счетчик и в каждый канал фильтрации - дополнительный дешифратор/ дополнительный элемент памяти и дополнительный элемент совпадения, при этом в кэзкдом канале фильтрации первый вход элемента совпадения соединен с прямым выходом элемента памяти своего канала фильтрации. второй вход - с инверсным выходом элеме-нта памяти последующего какала фильтра ции, третий вход - с прямым выходом дополнительного элемента памяти своего канала фильтрации, а четвертый вход - с первым выходом синхронизатора, первый вход дополнительного элемента совпадения подключен к прямому выходу элемента памяти последу101цего канала фильтрации, второй вход К инверсному выходу элемента памяти Явоего канала фильтрации, третий щхоц к инверсному выходу дополнительного элемента своего канала фильтрации , четвертый вход - к первому выходу синхронизатора, а выход ко второму входу накопителя, первый екод элемента памяти соединен с выходом дешифратора, первый вход дополнительного элемента памяти - с выходом дополнительного дешифратора входы дешифраторов и первые входы дополнительных дешифраторов объеди-. иены и подключены к выходу счетчика а вторые входы дополнительных дешифраторов - к выходу дополнительного счетчика, причем выход генератора эталонной частоты соединен со счетWb входом дополнительного счетчика к со входом распределителя частоты, выходы которого подключены к тактовым входам -синхронизатора, второй выход которого соединен с установочными входами счетчика, дополнительного счетчика, элементов памяти каждого канала фильтрации.

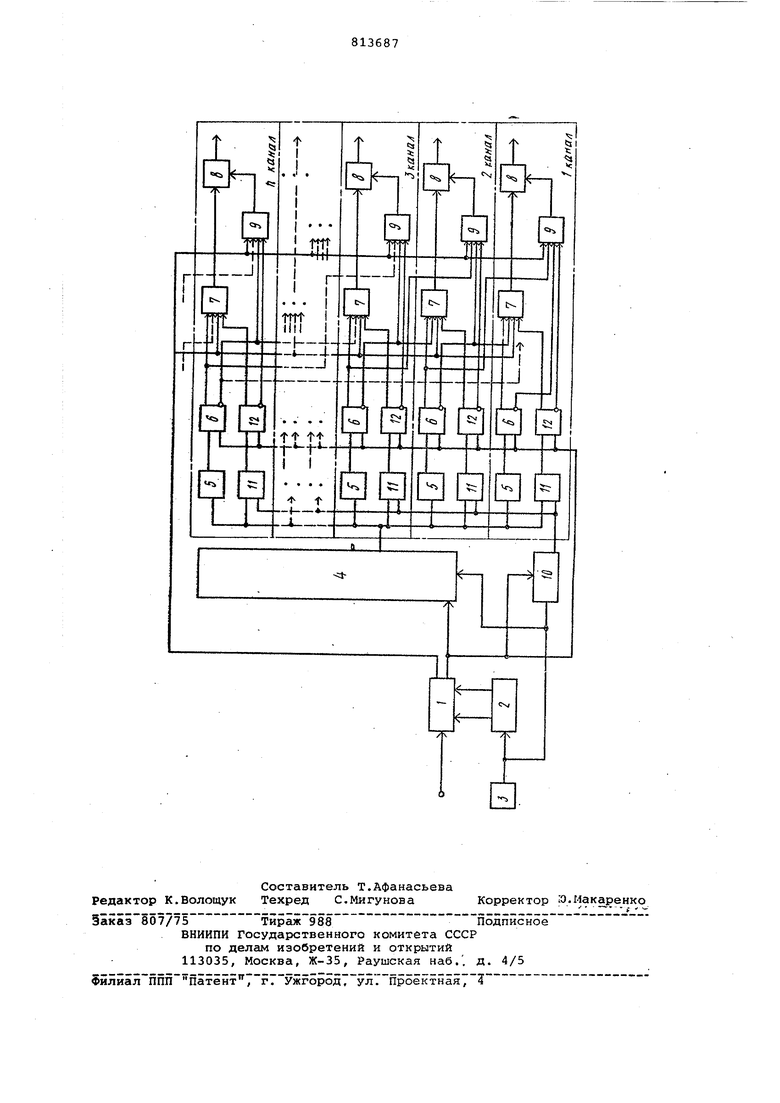

На чертеже представлена структурная электрическая схема многоканального полосового цифрового фильтра.

Источник импульсов измеряемой частоты подключен к входу синхронизтора 1, тактовые входы которого подсоединены к выходам распределителя частоты 2, подключенного к генератору эталонной частоты 3. На вход счечика 4 подаются .импульсы с выхода генератора 3. Выходц счетчика 4 подключены к дешифраторам 5 заданных состояний, выходы которых соединены с входами элементов 6 памяти, выполненных на триггерах. Прямые выходы элементов б памяти соединены с первыми входами соответствующих эле- ментов совпадения 7, второй вход каждого элемента совпадения 7 сое-динен с инверсным выходом элемента памяти б следующего канала. Выход каждого элемента совпадения 7 подключен к входу соответствующего накопителя 8. Установочный вход каждого накопителя 8 подключен к выходу дополнительного элемента совпадения 9. ncpBLMH вход каждого дополнительного элемента совпадения 9 подключен к прямому выходу элемента б памяти, второй вход - к инверсному выходу соответствующего элемента памяти 6. Третьи входы схем дополнительных элементов совпадения 9, объединенные с третьими.входами элементов совпадения 7, подсоединены к выходу Опрос синхронизатора 1. Установочные входы элементов 6 памяти и счетчика 4 подключены к другому выходу (Сброс) синхронизатора 1. Вход дополнительного счетчика 10 объединен с входом счетчика 4, выход его подключен ко вторым входам дополнительных дешифраторов 11, каждому из которых соответствует контрольное состояние счетчика 4, близкое к фиксированному, выделяемому соответствующим дешифратором 5, и кратное состоянию дополнительного счетчика 10. Входы дополнительных элементов памяти 12 подключены к выходам дополнительных дешифраторов 11, а выходы - к четвертьЕ входам элементов совпадения 7 и 9.

При необходимости получения на выходе какого-либо канала полосы частот с заданной величиной перекрытия по отношению к соседним каналам, вторые входы элементов совпадения 7 и 9 п-го канала могут быть подключены соответственно к инверсному и прямому выходам элемента памяти (п + к) канала, где К 2,3 и т. д. как, например, это показано пунктиром на чертеже для первого и третьего каналов.

Устройство работает следующим образом.

При поступлении на вход устройства последовательности импульсов синхронизатор 1, управляемый сдвинутыми по фазе тактовыми импульсами с выхода распределителя 2, вырабатывает две последовательности импульсов с периодом входного сигнала, сдвинутые друг относительно друга на период тактовой частоты. При этом импульсы на первом выходе распреде.пителя 2 опережают по времени импульсы на другом его выходе. Импульсы тактовой частоты генератора 3 поступают на счетчик 4. При этом счетчик принимает ряд состояний, фиксируемых соответствующими дешифраторами, сначала дополнительным 11, затем основным 5 выходные сигналы которых фиксируются в элементах 12 и б памяти. При этом чем ниже частота поступающих на вход устройства импульсов , тем большее количество элементов 12 и 6 памяти переключится и.вьщаст разрешающий уровень сначала на четвертый, а затем и на первый вход соответствующих элемеь:тоБ совпадения 7. Однако с приходом сигнала Опрос на третьи входы элементов coвпaлef кя 7 вкход ой сиг.чал будет присутствовать только

на ёыходе того элемента совпадения 7, который соответствует последнему из дешифраторов 5, выдавшему сигнал на элемент 6 памяти до прихода сигнала Опрос, поскольку на втором входе этого элемента имеется разрешающий уровень соседнего элемента б памяти, соответствующего очередному дешифратору 5, не получившему сигнал.со счетчика 4. Таким образом на выходе каждого элемента совпадедения 7 будут присутствовать импульсы, совпадающие по времени с импульсами Опрос, частоты которых лежат в границах, задаваемых соседними дешифраторами .

На выходе накопителей 8 командный сигнал появляется только после уверенного приема соответствующим элементом совпадения 7 заданной полосы частот- (например, в количестве трех импульсов). Сигнал, случайно прошедший на выход элемента совпадения 7, в следующем цикле опроса сбрасывается с накопителя 8 с помощью дополнительного элемента совпадения 9. Сигналом Сброс с выхода синхронизатора элементы памяти 6 и 12 и счетчики 4 и 10 устанавливаются в исходное состояние.

Применение в устройстве четкой

организации частот Сброс и Опрос введение дополнительных элементов совпадения, включение определенным образом накопителей импульсов и элементов памяти, а также введение дополнительных дешифраторов с контрольными элементами памяти позволяет сократить до минимума вероятность появления на выходе ложной информации, что особенно важно когда выходные сигналы являются.командными для приведения в действие исполнител1)Ных механизмов .как при обработке информации с заданной стабильностью полос частот, так и с непрерывно меняющейся частотой. Кроме того, включение синхронизатора в иепь-входного сигнала значительно пов.ышает помехоустойчивость фильтра; фильтр не сложен по конструкции, по настройке и может быть реализован на микросхемах широкого применения.

Формула изобретения

Многоканальный полосовой цифровой фильтр, содержащий счетчик, счетный вход которого соединен с выходом генератора эталонной частоты, и П параллельно включенных каналов фильтрации, каждый из которых состоит ии дешифратора, элемента памяти и элемента совпадения, выход которого соединен с первым входом накопителя, отлич-ающийся тем, что, с целью повышения помехоустойчивости в него введены синхрон-изатор, распределитель частоты, дополнительный счетчик и в каждый канал фильтрации- дополнительный дешифратор, дополнительный элемент памяти и дополни0тельный элемент совпадения, при в каждом канале фильтрации первый вход элемента совпадения соединен с прямым выходом элемента памяти своего канала фильтрации, второй

5 вход - с инверсным выходом элемента па.мяти последующего канала фильтрации , третий вход - с прямым выходом дополнительного элемента памяти своего канала фильтрации, а четвертый

0 вход - с первым выходом синхронизатора, первый вход дополнительного элемента совпадения подключен к прямому выходу элемента памяти последующего канала фильтрации, второй вход к инверсному выходу элемента памяти

5 своего канала фильтрации, третий вход - к инверсному выходу дополнительного элемента памяти своего канала фильтрации, четвертый вход - к первому выходу синхронизатора, а вы0ход - ко второму входу накопителя, первый вход элемента памяти соединен с выходом дешифратора, первый вход дополнительного элемента памяти с выходом дополнительного дзшифр.атора, входы дешифраторов и первый входы дополнительных дешифраторов объединены и подключены к выходу счетчика, а вторые входы дополнительных дешифраторов - к выходу дополнитель0ного счетчика, причем выход генератора эталонной частоты соединен со счетным входом дополнительного счетчика и со входом распределителя частоты , выходы которого подключены к тактовым входам синхронизатора,, второй выход которого соединен с уст-ановочнымр входами счетчика, дополнительного счетчика, элементов памяти и дополнительных- элементов памяти каждого канала фильтрации.

Источники информации, принятые во внимание при экспертиз е 1. Машбиц Л.М. Синтез систем частотной селекции с помощью числовых схем. Радиотехника, т. 24, № 9, 1969, с. 63-70.

2. Авторское свидетельство СССР f 250225. кл. Н 03 У 17/62, 1968 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный полосовой цифровой фильтр | 1983 |

|

SU1092706A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ЧИСЛА ПРОСТОЕВ ОБОРУДОВАНИЯ | 1991 |

|

RU2017219C1 |

| Устройство для приема сигналов двойной частотной телеграфии | 1982 |

|

SU1136321A2 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

| Устройство для циклической телесигнализации | 1976 |

|

SU703854A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство для управления процессом смешения жидких продуктов | 1985 |

|

SU1272314A1 |

| Устройство для группового управления лифтами | 1982 |

|

SU1089024A1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

Авторы

Даты

1981-03-15—Публикация

1978-03-28—Подача