1

Изобретение относится к вычислительной технике и цифровой высокочастотной автоматике и может быть использовано преимущественно при построении радиоимпульсных однородных вычислительных структур, предназначенных для обработки радиосигналов, в качестве носителя информации в которых используется фаза высокочастотных колебаний.

Известны элементы однородной вычислительной структуры, предназначен ные для обработки высокочастотных сигналов, содержащие функциональную и настроечную части 1 .

Недостатком элементов однородной вычислительной структуры является ограниченные функционгшьные возможности и сложность конструкции.

Наиболее близким к предлагаемому является элемент однородной вычислительной структуры, используемый преимущественно при построении радиоимпульсных однородных вычислительных структур, предназначенных для обработки радиосигналов и носителем информации в которых является фаза высокочрстотных колебаний и содержащих идентично построенные функциональный и настроечный емкостные параметроны, включающие катушку индуктивности с отводом от .средней точки, два варикапа и два диода., .а также два транзисторных ключа 2 .

Недостатком элемента однородной вычислительной структуры является большое количество элементов схемы (20 шт) и ограниченные функциональные возможности.

0

Выполнение функции памяти в элементе однородной вычислительной структуры, осуществляется функциональным параметром при его работе в непрерывном режиме, а считывание

5 информации производится через инверсный выход (вход) настроечного параметрона, возбуждаемого в необходшллй момент времени при подаче на него видеоимпульсов первого, второго или

0 третьего тактов. Этот элемент однородной вычислительной структуры при соответствующей настройке может быть использован преимущественно в качестве элемента памяти в запоминающих

5 устройствах. Выполнение указанными элементами функции памяти затруднительно, а иногда и нецелесообразно, так как в однородных структурах входы (выходы) функциональных парамет0ронов соседних элементов соединены

через резисторы связи, а инверсные входы С,эыходы) настроечных параметронов всех элементов однородной вычислительной структуры подключены через развязывающие резисторы к одной общей шине опорного напряжения частоты субгармоники, что исключает использование настроечных параметронов для считывания информации. Кроме того, при изготовлении однородных вычислительных структур в виде микросборок с высоким уровнем интеграции имеется доступ для ввода информации только к периферийным элементам. Но при этом для выполнения одним из элементов однородной вычислительной структуры функции памяти все соседние элементы структуры, т.е. непосредственно соединенные с данным элементом, должны быть выключены и выполнять функцию разрыва в цепи передачи сигнала на все время хранения информации, что позволяет исключить прохождение сигнала с данного элемента на остальные элементы однородной вычислительной структуры. Таким образом, соседние элементы структуры практически не используются при регшизации автомата в однородной вычислительной структуре, а считывание информации производится с помощью одного из соседних элементов однородной вычислительной структуры, настроенного на выполнение функции соединения и возбуждаемого в первом, втором или третьем тактах по окончаНИИ времени хранения.

Цель изобретения - упрощение конструкции и расширение функциональных возможностей за счет одновременного выполнения логических функций и функции памяти.

Поставленная цель достигается тем что в элемент однородной вычислительной структуры, содержащий первую и вторую катушки индуктивности с отводами от средних точек, первый, второй, третий и четвертый резисторы связи, первый и второй транзисторы, причем отводы средних точек катушек индуктивности соединены между собой, первый вывод первой катушки индуктивности через последовательно соединенные первый и второй резисторы связи соединен с первым выводом второй катушки индуктивности, а второй вывод второй катушки индуктивности через последовательно соединенные третий и четвертый резисторы связи соединен с первым выводом первой катущки индуктивности, коллектор первого транзистора подключен к общему выводу первого и второго резисторов связи, а коллектор второго транзистора подключен к общему выводу третьего и четвертого резисторов связ.и, дополнительно введены третий, четвертый, пятый, шестой и седьмой транзисторы, причем первый и второй выводы

первой катушки индуктивности соединены соответственно с коллектором третьего и четвертого транзисторов, а первый и второй выводы второй катушки индуктивности соединены соответственно с коллекторами пятого и шестого транзисторов, база третьего, четвертого, пятого и шестого транзисторов соединены между собой и подключены к общему выводу элемента,отводы средних точек катушек индуктив0ности подключены к шине напряжения накачки элемента, первый и второй выводы первой катушки индуктивности соединены соответственно с инверсными и прямыми сигнальными входами

5 (выходами) элемента, эмиттер седьмого транзистора соединен с шиной опорного напряжения частоты субгармоники, а база - с первым входом управления элемента, второй вход управле0ния элемента соединен с базой первого транзистора, а третий вход управления элемента соединен с базой второго транзистора, четвертый вход управления элемента соединен с эмитте5рами третьего и четвертого транзисторов, а пятый вход управления элемента соединен с эмиттером пятого и шестого транзисторов, эмиттеры первого и второго транзисторов соединены между собой и подключены к общему

0 выводу элемента.

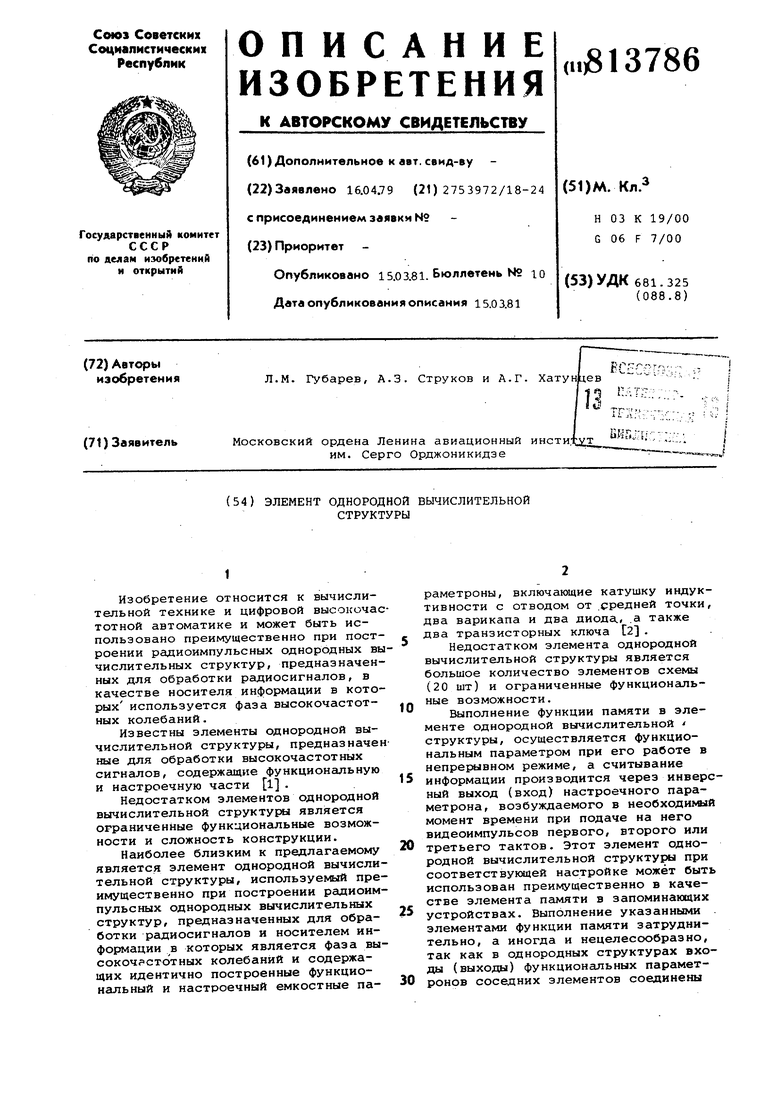

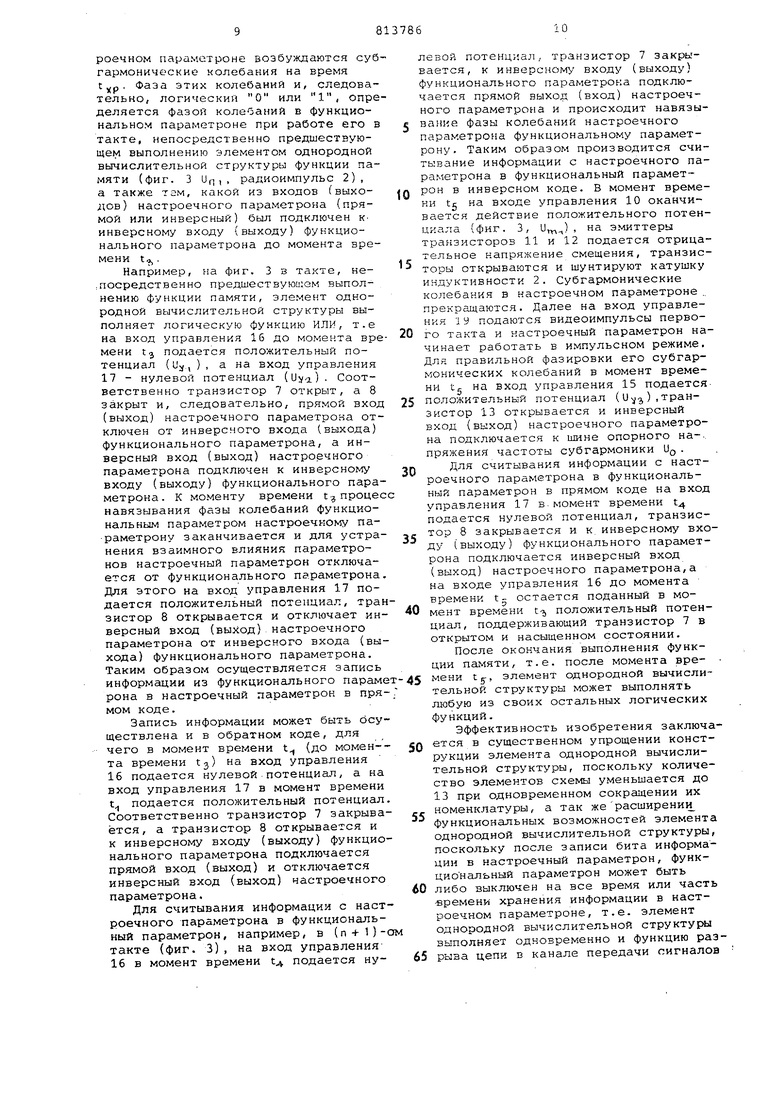

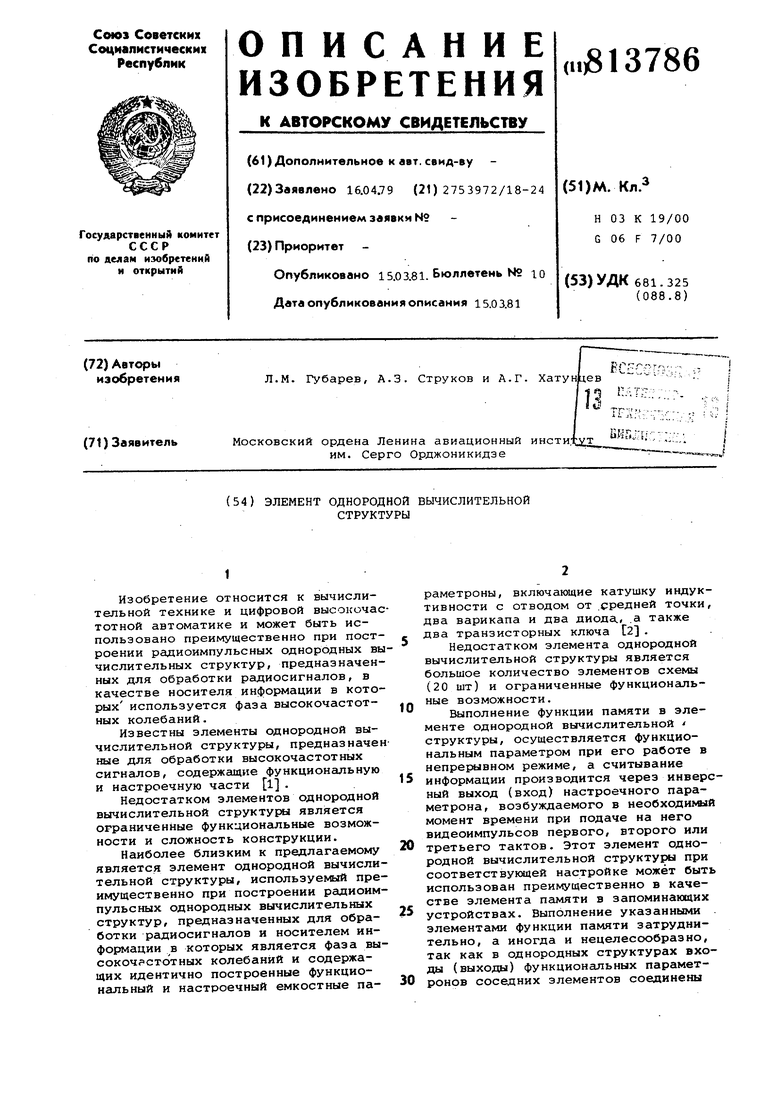

На фиг. 1 приведена принципиальная схема элемента однородной вычислительной структуры, содержащего

5 первую и вторую катушки индуктивности с отводом от средней точки 1 и 2, первый, второй, третий и четвертый резисторы связи 3-6, первый, второй, третий, четвертый, пятый, шестой и

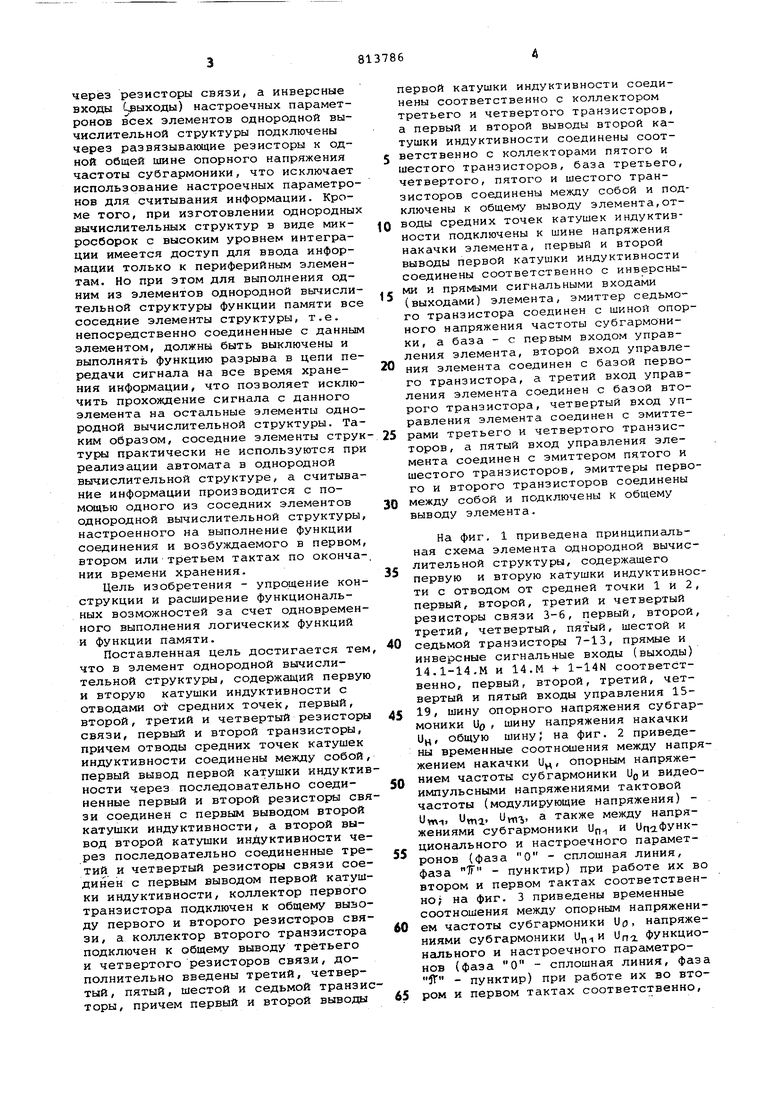

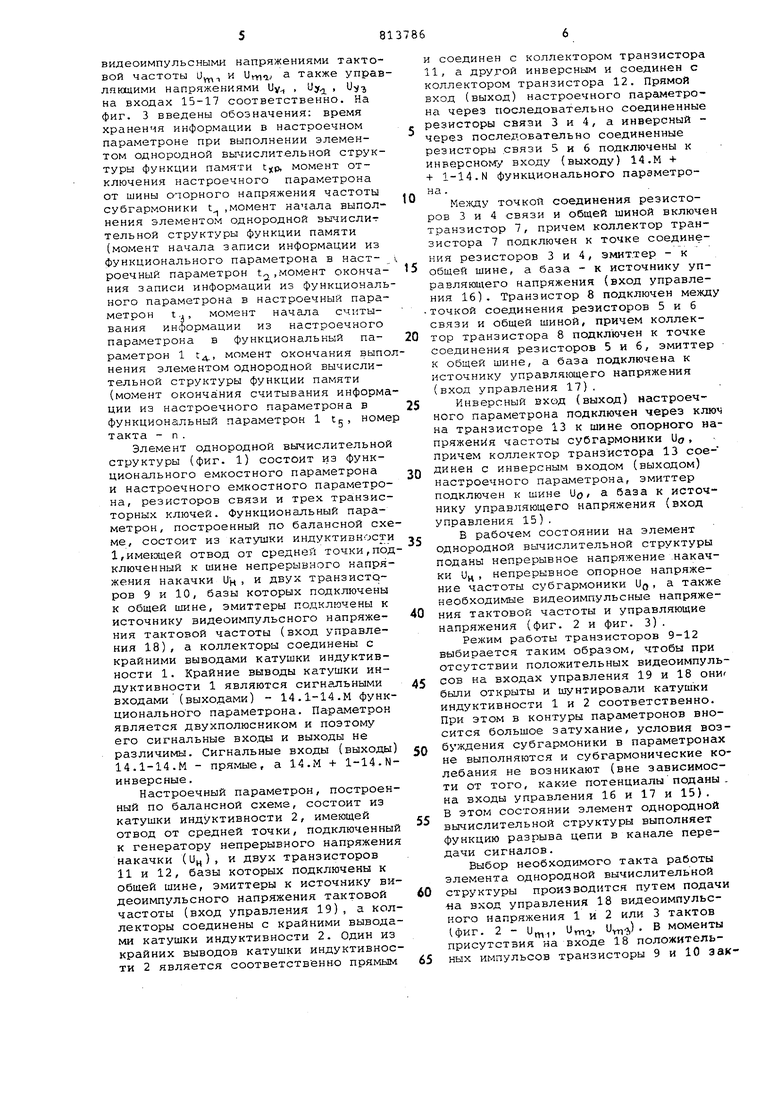

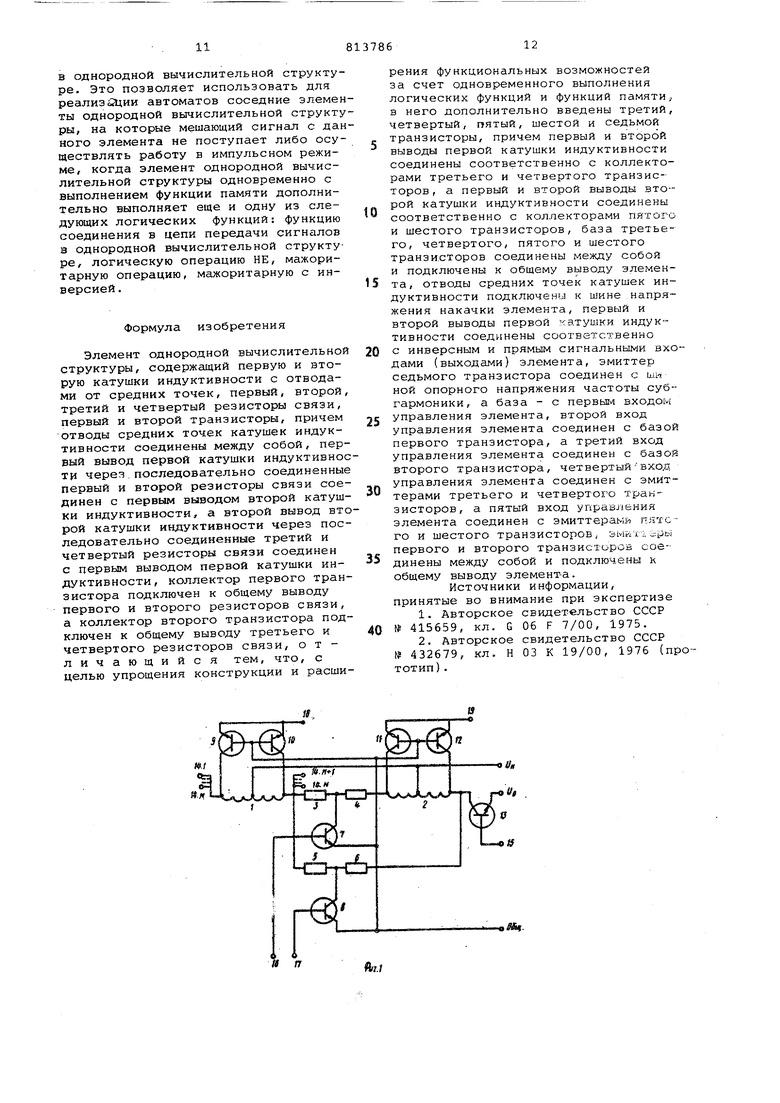

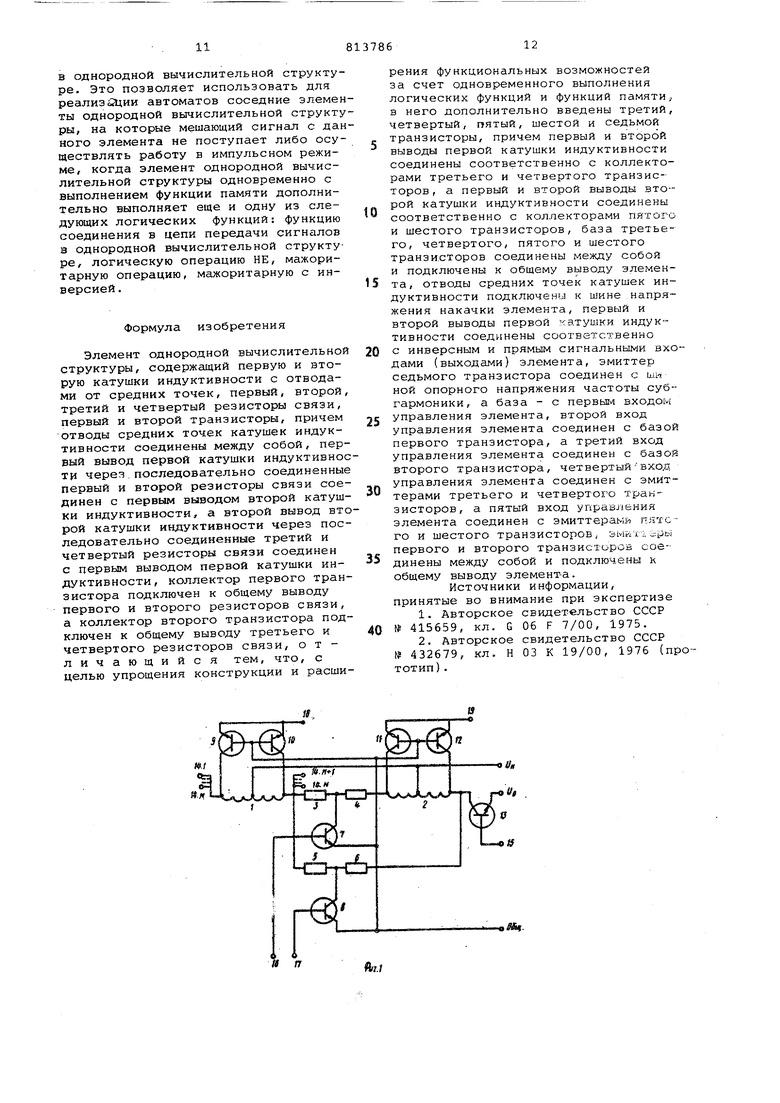

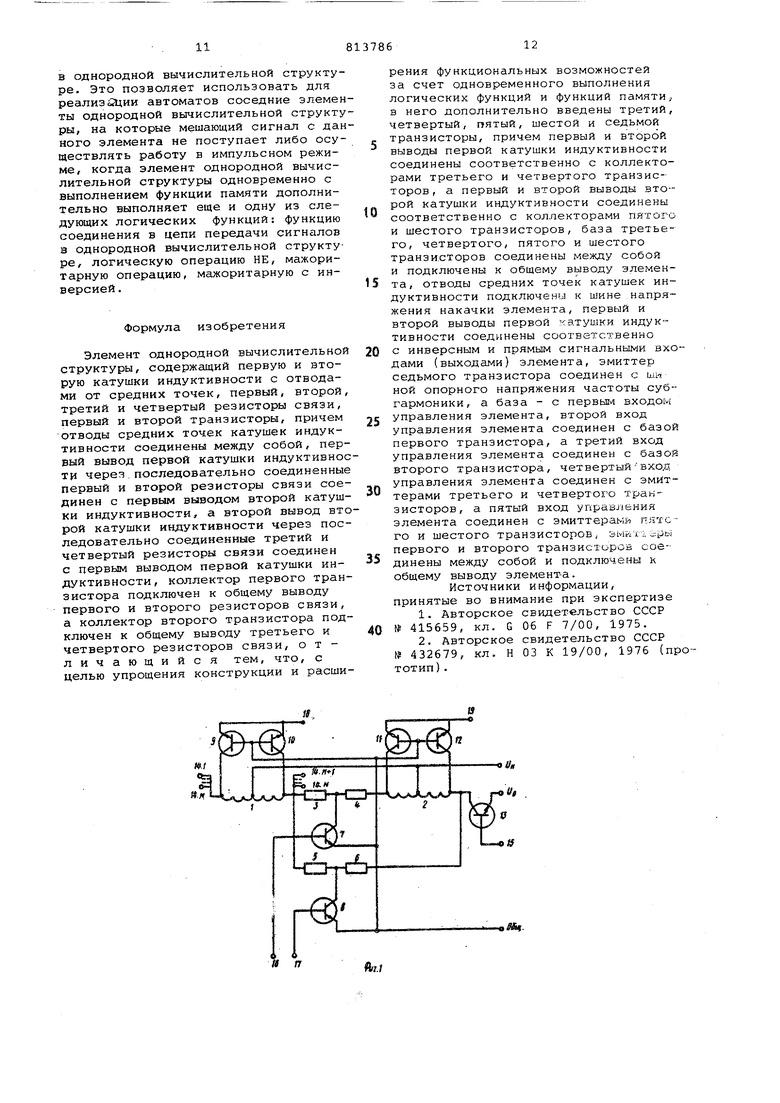

0 седьмой транзисторы 7-13, прямые и инверсные сигнальные входы (выходы) 14.1-14.М и 14.М + 1-14N соответственно, первый, второй, третий, четвертый и пятый входы управления 1519, шину опорного напряжения субгар5моники Uo, шину напряжения накачки Уц, общую шину; на фиг. 2 приведены временные соотношения между напряжением накачки Уц, опорным напряжением частоты субгармоники UQи видео0импульсными напряжениями тактовой частоты (модулирующие напряжения) Uwi. тЪ э также между напряжениями субгармоники Uf,-, и ипаФУНкционального и настроечного парамет5ронов (фаза О - сплошная линия, фаза F - пунктир) при работе их во втором и первом тактах соответственно; на фиг. 3 приведены временные соотношения между опорным напряжени0ем частоты субгармоники Uo, напряжениями субгармоники Una Функционального и настроечного параметронов (фаза О - сплошная линия, фаза 5Т - пунктир) при работе их во вто5ром и первом тактах соответственно.

видеоимпульсными напряжениями тактовой частоты UyY,T и а также управляющими напряжениями Uy , Uy , U на входах 15-17 соответственно. На фиг. 3 введены обозначения: время хранения информации в настроечном параметроне при выполнении элементом однородной вычислительной структуры функции памяти t.(p, момент отключения настроечного параметрона от шины опорного напряжения частоты субгармоники t .момент начала выполнения элементом однородной вычислит тельной структуры функции памяти (момент начала записи информации из функционального параметрона в настроечный параметрон t,момент окончания записи информации из функционального параметрона в настроечный параметрон t ,,j, момент начала считывания информации из настроечного параметрона в функциональный параметрон 1 t., момент окончания выпонения элементом однородной вычислительной структуры функции памяти (момент окончания считывания информации из настроечного параметрона в функциональный параметрон 1 tc, номе такта - п.

Элемент однородной вычислительной структуры (фиг. 1) состоит из функционального емкостного параметрона и настроечного емкостного параметрона, резисторов связи и трех транзисторных ключей. Функциональный параметрон, построенный по балансной схеме, состоит из катушки индуктивности 1, отвод от средней точки,подключенный к шине непрерывного напряжения накачки иц, и двух транзисторов 9 и 10, базы которых подключены к общей шине, эмиттеры подключены к источнику видеоимпульсного напряжения тактовой частоты (вход управления 18), а коллекторы соединены с крайними выводами катушки индуктивности 1. Крайние выводы катушки индуктивности 1 являются сигнальными входами (выходами) - 14.1-14.М функционального параметрона. Параметрон является двухполюсником и поэтому его сигнальные входы и выходы не различимы. Сигнальные входы (выходы) 14.1-14.М - прямые, а 14.М + 1-14.Nинверсные.

Настроечный параметрон, построенный по балансной схеме, состоит из катушки индуктивности 2, имеющей отвод от средней точки, подключенный к генератору непрерывного напряжения накачки (Уц), и двух транзисторов 11 и 12, базы которых подключены к общей шине, эмиттеры к источнику видеоимпульсного напряжения тактовой частоты (вход управления 19), а коллекторы соединены с крайними выводами катушки индуктивности 2. Один из крайних выводов катушки индуктивности 2 является соответственно прямым

и соединен с коллектором транзистора 11, а другой инверсным и соединен с коллектором транзистора 12. Прямой вход (выход) настроечного параметрсна через последовательно соединенные резисторы связи 3 и 4, а инверсный через последовательно соединенные резисторы связи 5 и б подключены к инверсному входу (выходу) 14.М + + 1-14. N функционального парэметрона .

0

Между точкой соединения резисторов 3 и 4 связи и общей шиной включен транзистор 7, причем коллектор транзистора 7 подключен к точке соединения резисторов 3 и 4, эмит.тер - к

5 общей шине, а база - к источнику управляющего напряжения (вход управления 16). Транзистор 8 подключен между точкой соединения резисторов 5 и 6 связи и общей шиной, причем коллек0тор транзистора 8 подключен к точке соединения резисторов 5 И б, эмиттер к общей шине, а база подключена к источнику управляющего напряжения (вход управления 17) .

Инверсный вход (выход) настроеч5ного параметрона подключен через ключ на транзисторе 13 к шине опорного напряжения частоты субгармоники Uo, причем коллектор транзистора 13 соединен с инверсным входом (выходом)

0 настроечного параметрона, эмиттер подключен к шине UQ, а база к источнику управляющего напряжения (вход управления 15).

В рабочем состоянии на элемент

5 однородной вычислительной структуры поданы непрерывное напряжение .накачки Уц , непрерывное опорное напряжение частоты субгармоники UQ, а также необходимые видеоимпульсные напряже0ния тактовой частоты и управляющие напряжения (фиг. 2 и фиг. 3) .

Режим работы транзисторов 9-12 выбирается таким образом, чтобы при отсутствии положительных видеоимпульсов на входах управления 19 и 18 они

5 были открыты и шунтировали катушки индуктивности 1 и 2 соответственно. При этом в контуры параметронов вносится большое затухание, условия возбуждения субгармоники в параметронах

0 не выполняются и субгармонические колебания не возникают (вне зависимости от того, какие потенциалы поданына входы управления 16 и 17 и 15). В этом состоянии элемент однородной

5 вычислительной структуры выполняет функцию разрыва цепи в канале передачи сигналов.

Выбор необходимого такта работы элемента однородной вычислительной

0 структуры производится путем подачи «а вход управления 18 видеоимпульсного напряжения 1 и 2 или 3 тактов

В моменты

1ФИГ. 2 - и

mi тЪ

и

m 1

присутствия на входе 18 положительных импульсов транзисторы 9 и 10 эакрываются и функциональный параметро возбуждается. В том случае, если на вход 19 видеоимпульснее напряжение не поступает, то вне зависимости от того, какие потенциалы поданы на входы 16 и 17 и 15 элемент однородной вычислительной структуры выполняет : 1.Функцию соединения в цепи пере дачи сигналов в однородной вычислительной структуре, когда на один из прямых входов (выходов) 14.1-14.М поступает сигнал, а выходной сигнал снимается с другого прямого выхода. 2.Логическую операцию НЕ, когда на один из входов 14.1-14.М поступает с игнал, а выходной сигнал снимает ся с одного из инверсных выходов 14.M+1-14N или, когда входной сигнал поступает на инверсный вход параметрона, а снимается с прямого., 3.Мажоритарную функцию, когда на его сигнальные входы (выходы) 14.1-14.М поступает нечетное количе ство сигналов, а выходной сигнал сни мается с одного из прямых выходов. 4.Мажоритарную функцию с инверсией, если на входы 14.1-14.М посту пает нечетное количество сигналов, а ВЫХОДНОЙ сигнал снимается с одного из инверсных выходов 14.M+1-14.N Выбор такта возбуждения параметрона настроечной части осуществляет ся путем подачи видеоимпульсного на.пряжения на вход управления 19. В моменты присутствия на входе 19 положительных видеоимпульсов транзисто ры 11 и 12 закрываются и настроечный параметрон возбуждается всегда в одной и той же фазе, которая однозначно определяется фазой непрерывного опорного напряжения частоты субгармо ники Ue, поступающего на инверсный вход (выход) параметрона, в том случае, когда на вход управления 15 подан положительный потенциал и, следовательно, транзистор 13 открыт Положительный потенциал на вход управления 15 подается в течение всего времени выполнения элементом однородной вычислительной структуры логи ческих функций И, ИЛИ, И-НЕ, ИЛИ-НЕ Для обеспечения выполнения элемен том однородной вычислительной структуры логических функций И, ИЛИ, ИЛИНЕ, необходимо так выбирать такты видеоимпульсных напряжений, подавае мых на параметроны, чтобы настроечный параметрон всегда возбуждался в такте, предшествующем такту возбуж дения функционального параметрона. Например, (фиг. 2) функциональный параметрон работает во втором такте а настроечный параметрон - в первом такте . При подаче положительного потенциала на 16 и нулевого на вход 17 транзистор 7 открывается, перехо дит в режим насыщения и подключает точку соединения резисторов 3 и 4 к общей шине, а транзистор 8 запирается. Таким образом, прямой выход настроечного параметрона оказывается отключенным, а инверсный - подключенным к инверсному входу функционального параметрона, и радиоимпульсное опорное напряжение частоты субгармоники фазы Г с настроечного параметрона поступает на функциональный параметрон. В этом элемент однородной вычислительной структуры выполняет: 1.Логическую функцию ИЛИ от двух переменных, если входные сигналы поступают на два каких-либо прямых входа 14.1-14.М, а выходной сигнал снимается с одного из прямых выходов . 2.Функцию ИЛИ-НЕ, когда сигналы (входные) поступают на два каких-либо прямых входа 14.1-14.М, а выходной сигнал снимается с одного из инверсных выходов 14.M+1-14.N. При подаче положительного потенциала на вход управления 17 и нулевого на вход управления 16 транзистор 8 открывается, переходит в режим насьндения и подключает точку соединения резисторов 5 и 6 кобщей шине,а транзистор 7 запирается. При этом инверсный выход настроечного параметрона оказывается отключенным, а прямой - подключенным к инверсному входу функционального параметрона и радиоимпульсное опорное напряжение частоты субгармоники фазы О с настроечного параметрона поступает на функциональный параметрон. В этом случае элемент однородной вычислительной структуры выполняет: 1.Логическую функцию И от двух переменных, если два входных сигнала поступают на входы (выходы) 14.1-14.М, а выходной сигнал снимается с одного из прямых выходов. 2.Функцию И-НЕ, если два входных сигнала поступают на входы 14-1-14.М, а выходной сигнал снимается с одного из инверсных выходов 14.M+1-14.N. Элемент однородной вычислительной структуры выполняет функцию памяти, причем хранение информации осуществляется в настроечном параметроне.В этом случае на вход управления 15 в момент окончания последнего перед выполнением функции памяти тактового видеоимпульса ( t-, ) (фиг.З) поступает отрицательный потенциал (Uy), транзистор 13 закрывается и, таким обра-. зом, отключает настроечный параметрон от шины опорного напряжения частоты субгармоники UQ. В момент времени t/jHa вход управления 19 поступает положительный видеоимпульс, длительность которого равна времени хранения информации txp в элементе однородной вычислительной структуры,транэисторы 11 и 12 закрываются и в настроечном параметроне возбуждаются суб гармонические колебания на время tур. Фаза этих колебаний и, следовательно, логический О или 1, опре деляется фазой колебаний в функциональном параметроне при работе его в такте, непосредственно предшествующем выполнению элементом однородной вычислительной структуры функции памяти (фиг. 3 Urii, радиоимпульс 2), а также там, какой из входов (выходов) настроечного параметрона {прямой или инверсный) был подключен кинверсному входу (выходу) функционального параметрона до момента времени t . Например, на фиг, 3 в тахте, не:посредственно предшествующем выполнению функции памяти, элемент однородной вычислительной структуры выполняет логическую функцию ИЛИ, т.е на вход управления 16 до момента вре мени t подается положительный потенциал {U;,, ) , а на вход управления 17 - нулевой потенциал (Uvo.) . Соответственно транзистор 7 открыт, а 8 закрыт и, следовательно, прямой вход (выход) настроечного параметрона отключен от инверсного входа (выхода) функционального параметрона, а инверсный вход (выход) настроечного параметрона подключен к инверсному входу (выходу) функционального пара метрона. К моменту времени t проце навязывания фазы колебаний функциональным параметром настроечному па-раметрону заканчивается и для устра нения взаимного БЛИННИК параметронов настроечный параметров отключается от функционального параметрона Для этого на вход управления 17 подается положительный потенциал, тра зистор 8 открывается и отключает ин версный вход (выход) настроечного параметрона от инверсного входа (вы хода) функционального параметрона. Таким образом осуществляется запись информации из функционального парам рона в настроечный параметрон в пря мом коде. Запись информации может быть осу ществлена и в обратном коде, для чего в момент времени t (до момен- та времени tj) на вход управления 16 подается нулевой потенциал, а на вход управления 17 в момент времени t подается положительный потенциал Соответственно транзистор 7 закрыва ется, а транзистор 8 открывается и к инверсному входу (выходу) функцио нального параметрона подключается прямой вход (выход) и отключается инверсный вход (выход) настроечного параметрона. Для считывания информации с наст роечного параметрона в функциональный параметрон, например, в (п + 1)такте (фиг. 3), на вход управления 16 в момент времени t подается нулевой потенциал, транзистор 7 закрывается, к инверсному входу (выходу) функционального параметрона подключается прямой выход (вход) настроечного параметрона и происходит навязывание фазы колебаний настроечного параметрона функциональному параметрону. Таким образом производится считывание информации с настроечного параметрона в функциональный параметрон в инверсном коде. В момент времени tj на входе управления 10 оканчивается действие положительного потенциала (фиг. 3, Uf) , на эмиттеры транзисторов 11 и 12 подается отрицательное напряжение смещения, транзисторы открываются и шунтируют катушку индуктивности 2. Субгармонические колебания в настроечном параметроне прекращаются. Далее на вход управления 1У подаются видеоимпульсы первого такта и настроечный параметрон начинает работать в импульсном режиме. Для правильной фазировки его субгармонических колебаний в момент времени tj на вход управления 15 подаетсяположительный потенциал (U-,) .транзистор 13 открывается и инверсный вход (выход) настроечного параметрона подключается к шине опорного на-., пряжения частоты субгармоники Ug. Для считывания информации с настроечного параметрона в функциональный параметрон в прямом коде на вход управления 17 в момент времени t подается нулевой потенциал, транзистор 8 закрывается и к инверсному входу (выходу) функционального параметрона подключается инверсный вход (выход) настроечного параметрона,а на входе управления 16 до момента времени t- остается поданный в момент времени t-j положительный потенциал, поддерживающий транзистор 7 в открытом и насыщенном состоянии. После окончания выполнения функции памяти, т.е. после момента вре- мени tg-, элемент однородной вычислительной структуры может выполнять любую из своих остальных логических функций. Эффективность изобретения заключается в существенном упрощении конструкции элемента однородной вычислительной структуры, поскольку количество элементов схемы уменьшается до 13 при одновременном сокращении их номенклатуры, а так жерасширении функциональных возможностей элемента однородной вычислительной структуры, поскольку после записи бита информации в настроечный параметрон, функциональный параметрон может быть либо выключен на все время или часть -времени хранения информации в настроечном параметроне, т.е. элемент однородной вычислительной структур выполняет одновременно и функцию разрыва цепи в канале передачи сигналов

в однородной вычислительной структуре. Это позволяет использовать для реалиэс2ции автоматов соседние элементы однородной вычислительной структуры, на которые мешающий сигнал с данного элемента не поступает либо осуществлять работу в импульсном режиме, когда элемент однородной вычислительной структуры одновременно с выполнением функции памяти дополнительно выполняет еще и одну из следующих логических функций: функцию соединения в цепи передачи сигналов в однородной вычислительной структуре, логическую операцию НЕ, мажоритарную операцию, мажоритарную с инверсией .

Формула изобретения

Элемент однородной вычислительной структуры, содержащий первую и вторую катушки индуктивности с отводами от средних точек, первый второй, третий и четвертый резисторы связи, первый и второй транзисторы, причем отводы средних точек катушек индуктивности соединены между собой, первый вывод первой катушки индуктивности через последовательно соединенные первый и второй резисторы связи соединен с первым выводом второй катушки индуктивности, а второй вывод второй катушки индуктивности через последовательно соединенные третий и четвертый резисторы связи соединен с первым выводом первой катушки индуктивности, коллектор первого транзистора подключен к общему выводу первого и второго резисторов связи, а коллектор второго транзистора подключен к общему выводу третьего и четвертого резисторов связи, отличающийся тем, что, с целью упрощения конструкции и расширения функциональных возможностей за счет одновременного выполнения логических функций и функций памяти, в него дополнительно введены третий, четвертый, пятый, шестой и седьмой транзисторы, причем первый и второй выводы первой катушки индуктивности соединены соответственно с коллекторами третьего и четвертого транзисторов, а первый и второй выводы второй катушки индуктивности соединены соответственно с коллекторами пятого и шестого транзисторов, база третьего, четвертого, пятого и шестого транзисторов соединены между собой и подключены к общему выводу элемента, отводы средних точек катушек индуктивности подключены к шине напряжения накачки элемента, первый и второй выводы первой катушки индуктивности соединены соответственно с инверсным и прямым сигнальными входами (выходами) элемента, эмиттер седьмого транзистора соединен с ной опорного напряжения частоты субгармоники, а база - с пepвыI 1 входом управления элемента, второй вход управления элемента соединен с базой первого транзистора, а третий вход управления элемента соединен с базой второго транзистора, четвертыйвход управления элемента соединен с эмИттерами третьего и четвертого транзисторов, а пятый вход управления элемента соединен с эмиттерами пятого и шестого транзисторов; ЭЫй1 l ьрьг

первого и второго транзисторов соединены между собой и подключены к общему выводу элемент-а.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 415659, кл. G 06 F 7/00, 1975.

2.Авторское свидетельство СССР

№ 432679, кл. Н 03 К 19/00, 1976 (пртотип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕМЕНТ ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙСТРУКТУРЫ | 1972 |

|

SU432679A1 |

| Элементы однородной вычислительной структуры | 1980 |

|

SU930677A1 |

| ЭЛЕМЕНТ ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙСТРУКТУРЫ | 1972 |

|

SU415808A1 |

| Параметрический генератор | 1987 |

|

SU1518866A1 |

| Элемент однородной вычислительной структуры | 1984 |

|

SU1211890A1 |

| Элемент однородной вычислительной структуры | 1978 |

|

SU733107A1 |

| Ячейка однородной среды | 1984 |

|

SU1218378A1 |

| Элемент однородной вычислительной структуры | 1977 |

|

SU734878A1 |

| Регулятор постоянного тока | 1990 |

|

SU1817075A1 |

| Устройство для измерения фазы радиосигнала | 1979 |

|

SU976505A1 |

W2

A

Авторы

Даты

1981-03-15—Публикация

1979-04-16—Подача